## UNIVERSITY OF CALIFORNIA SAN DIEGO

# Enhancement Techniques for Digital Phase-Locked Loops

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Amr Ibrahim Farag Eissa

# Committee in charge:

Professor Ian Galton, Chair Professor Peter Asbeck Professor Gert Cauwenberghs Professor Truong Nguyen

Copyright

Amr Ibrahim Farag Eissa, 2024

All rights reserved.

| The dissertation of Amr Ibrahim Farag Eissa is approved, and it is acceptable in quality and |

|----------------------------------------------------------------------------------------------|

| form for publication on microfilm and electronically:                                        |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

|                                                                                              |

| Chair                                                                                        |

University of California San Diego

# DEDICATION

To My Late Father

# TABLE OF CONTENTS

| Signature Pageiii                                                          |

|----------------------------------------------------------------------------|

| Dedicationiv                                                               |

| Table of Contentsv                                                         |

| List of Figures ix                                                         |

| List of Tablesxv                                                           |

| Acknowledgementsxvi                                                        |

| Vitaxix                                                                    |

| Abstract of the Dissertationxx                                             |

| Chapter 1 An Incremental Frequency Control Scheme for Digitally Controlled |

| Oscillators                                                                |

| I. Introduction                                                            |

| II. Frequency Control in DCOs                                              |

| III. Proposed IFC Scheme                                                   |

| A. Qualitative Description5                                                |

| B. Architecture Details7                                                   |

| IV. Implementatoin Details                                                 |

| A. DCO Digital Interface9                                                  |

| B. FCE Banks                                                               |

| C. Integer FCE Bank Unit Cell11                                            |

| V. Measurement Results                                                     |

| VI. Conclusion14                                                           |

| Acknowledgements                                                           | 15        |

|----------------------------------------------------------------------------|-----------|

| Figures                                                                    | 16        |

| References                                                                 | 24        |

| Chapter 2 A Duty-Cycle-Error-Immune Reference Frequency Doubling Technique | ıe        |

| for Fractional-N Digital PLLs                                              | 27        |

| I. Introduction                                                            | 28        |

| II. Reference Frequency-Doubling in PLLs                                   | 30        |

| III. Proposed RFD Technique Qualitative Description                        | 34        |

| IV. Proposed FDC-PLL Architecture                                          | 35        |

| A. System Description                                                      | 35        |

| B, $\Delta\Sigma$ -FDC Linearized Model                                    | 38        |

| C. PLL Linearized Phase Noise Model                                        | 41        |

| $D_{\cdot}\Delta\Sigma$ -FDC Gain Calibration Details                      | 44        |

| E. Additional $\Delta\Sigma$ -FDC Properties                               | 46        |

| V. PLL Design Example                                                      | 48        |

| Appendix A: ΔΣ-FDC Linearized Model Derivation                             | 52        |

| Appendix B: PLL Phase Noise LTV Model Derivation                           | 54        |

| Acknowledgements                                                           | 60        |

| Figures                                                                    | 61        |

| Tables                                                                     | 66        |

|                                                                            | <b>60</b> |

| Chapter 3 A Charge Pump Nonlinearity Mechanism and its Mitigation in              |

|-----------------------------------------------------------------------------------|

| Fractional-N PLLs 72                                                              |

| I. Introduction                                                                   |

| II. CP Nonlinearity Mechanism and its Mitigation                                  |

| A. CP Nonlinearity Mechanism74                                                    |

| B. Proposed CP Linearization Scheme76                                             |

| III. Implementation Details                                                       |

| A. PLL Architecture Overview78                                                    |

| B. CP Design                                                                      |

| C. Simulation Results79                                                           |

| IV. Conclusion81                                                                  |

| Acknowledgements                                                                  |

| Figures                                                                           |

| Tables                                                                            |

| References                                                                        |

| Chapter 4 A 75 fs 9–11 GHz $\Delta\Sigma$ -FDC PLL IC: System Architecture Review |

| I. FDC-PLL Architecture Overview                                                  |

| II. Chip Overview                                                                 |

| III. IC Architecture Details: Analog Blocks                                       |

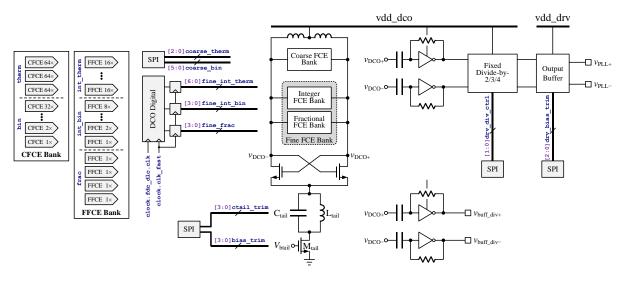

| A. Digitally-Controlled Oscillator100                                             |

| B. Multi-modulus Divider and Clocking101                                          |

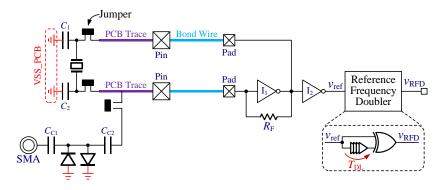

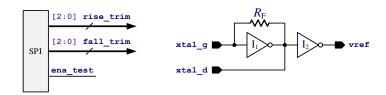

| C. Crystal Oscillator and Frequency Doubler103                                    |

| D. Phase Detector                           |  |  |  |  |

|---------------------------------------------|--|--|--|--|

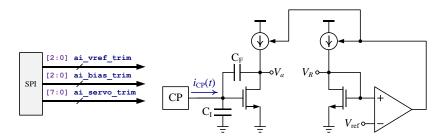

| E. Charge Pump and Active Integrator 104    |  |  |  |  |

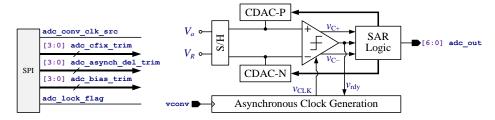

| F. Analog-to-Digital Converter              |  |  |  |  |

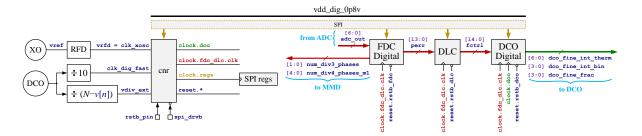

| IV. IC Architecture Details: Digital Blocks |  |  |  |  |

| A. Overview                                 |  |  |  |  |

| B. Clocking and Reset                       |  |  |  |  |

| C. FDC Digital106                           |  |  |  |  |

| D. Digital Loop Filter                      |  |  |  |  |

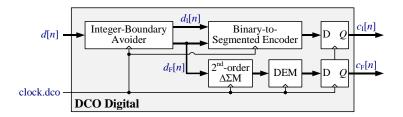

| E. DCO Digital                              |  |  |  |  |

| V. Behavioral Simulations                   |  |  |  |  |

| Acknowledgements                            |  |  |  |  |

| Figures                                     |  |  |  |  |

| Tables                                      |  |  |  |  |

| Deferences 122                              |  |  |  |  |

# LIST OF FIGURES

| Figure 1.1. Conventional DCO frequency control technique                                   | 16 |

|--------------------------------------------------------------------------------------------|----|

| Figure 1.2. (a) Top-level block diagram of the proposed IFC scheme, (b) integer FCE        |    |

| bank top-level structure, and (c) example waveforms for $d_I[n_t]$ and the FSM             |    |

| output, $m[r_t]$ , along with an illustration of the FCEs' states                          | 17 |

| Figure 1.3. Incremental switching logic signal processing details.                         | 18 |

| Figure 1.4. Proposed integer FCE bank architecture compatible with the IFC scheme          | 18 |

| Figure 1.5. Incremental switching FSM state-transition diagram.                            | 19 |

| Figure 1.6. (a) The four main unit cells comprising the integer FCE bank, (b) integer      |    |

| FCE bank layout, and (c) – (f) circuit implementation details of unit cells                |    |

| A1, A0, B0, and B1, respectively                                                           | 19 |

| Figure 1.7. (a) FCE circuit topology, (b) FCE switch implementation, and (c) integer       |    |

| FCE bank unit cell layout.                                                                 | 20 |

| Figure 1.8. Die photograph.                                                                | 21 |

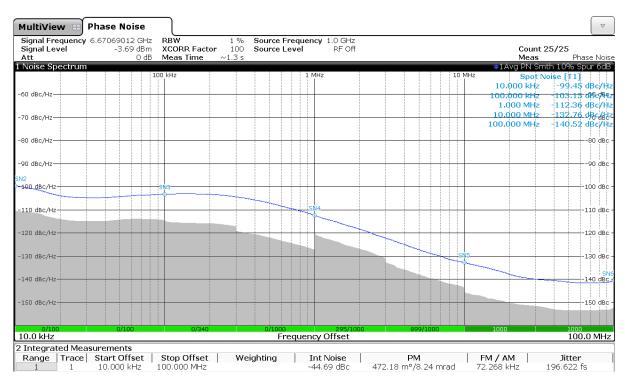

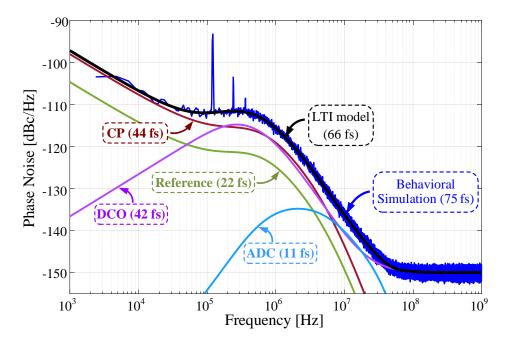

| Figure 1.9. Measured PLL phase noise at $f_{PLL} = 6.67$ GHz for a 550-kHz loop bandwidth. |    |

|                                                                                            | 21 |

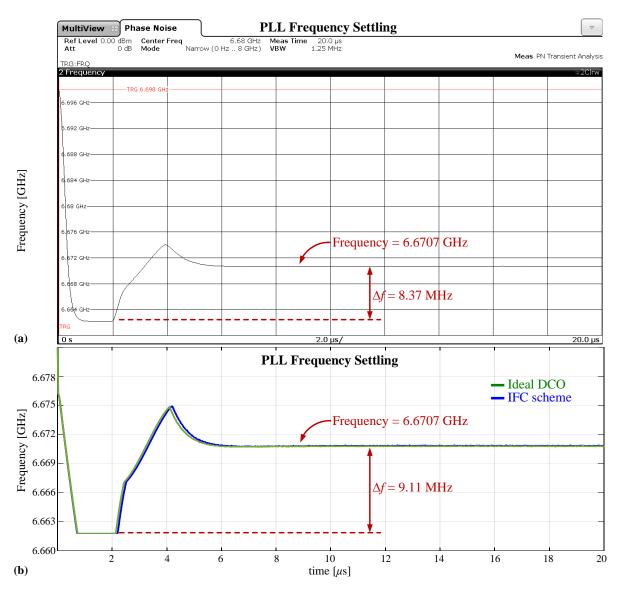

| Figure 1.10. PLL frequency-settling vs time. (a) Measurement results, and (b)              |    |

| behavioral model simulation results.                                                       | 22 |

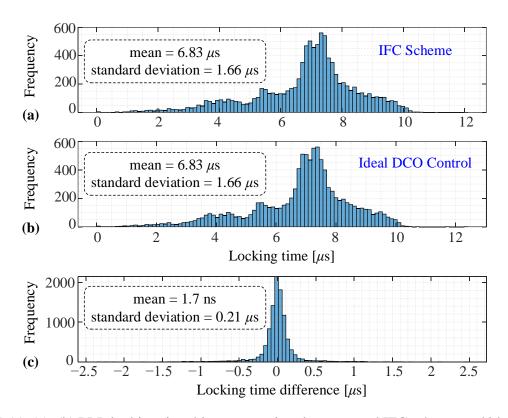

| Figure 1.11. (a), (b) PLL locking time histogram using the proposed IFC scheme and         |    |

| ideal DCO control, respectively, and (c) locking time difference histogram.                |    |

|                                                                                            | 23 |

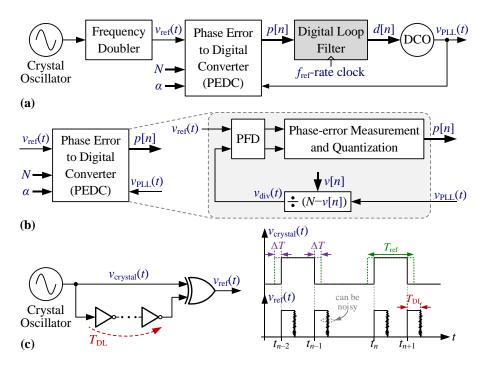

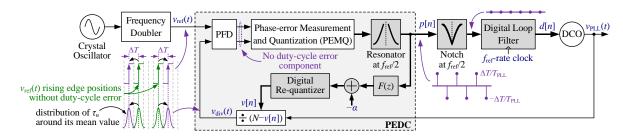

| Figure 2.1. | (a) Generic fractional-N digital PLL using a reference frequency-doubler,                                    |

|-------------|--------------------------------------------------------------------------------------------------------------|

|             | (b) general form of commonly used PEDCs that use MMD, and (c) XOR-                                           |

|             | based frequency-doubler and associated waveforms6                                                            |

| Figure 2.2. | High-level block diagram of a generic fractional-N digital PLL with the                                      |

|             | proposed reference frequency-doubling scheme                                                                 |

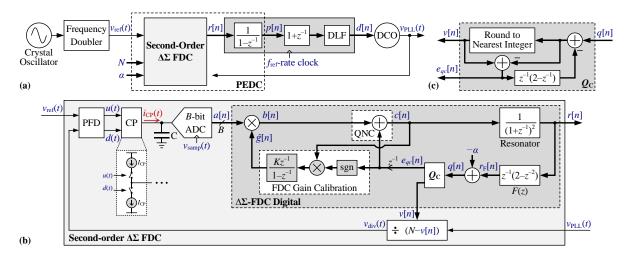

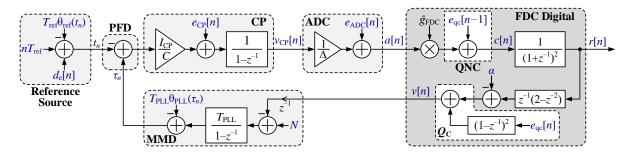

| Figure 2.3. | Block diagram of the proposed FDC-PLL: (a) PLL top-level block diagram,                                      |

|             | (b) second-order $\Delta\Sigma$ -FDC block diagram, and (c) coarse-quantizer, $Q_{\rm C}$ ,                  |

|             | implementation details6                                                                                      |

| Figure 2.4  | . (a) Linearized model of the proposed ΔΣ-FDC where $\hat{g}[n] = \hat{g}_{FDC}$ is                          |

|             | approximated as constant, and (b) FDC gain calibration behavioral model 62                                   |

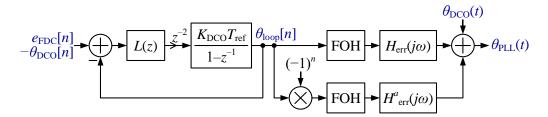

| Figure 2.5. | PLL LTV phase noise model                                                                                    |

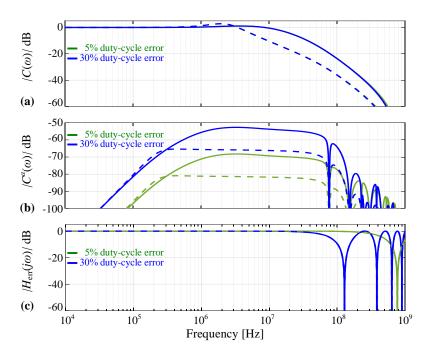

| Figure 2.6. | Magnitude responses of (a) $C(\omega)$ , (b) $C^a(\omega)$ , and (c) $H_{err}(j\omega)$ . Dashed (solid)     |

|             | lines correspond to a PLL bandwidth of 280 kHz (1.3 MHz). The 5% and                                         |

|             | 30% duty-cycle error curves coincide in (a)                                                                  |

| Figure 2.7. | PLL phase noise power spectra.                                                                               |

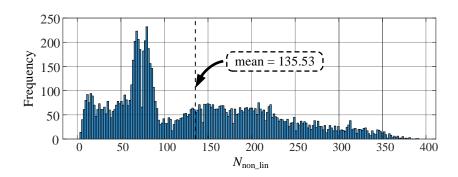

| Figure 2.8. | Histogram of $N_{\text{non-lin}}$ for 10000 PLL runs with random initial conditions 64                       |

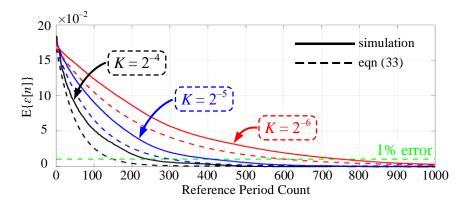

| Figure 2.9. | FDC gain calibration error sequence, $E\{\varepsilon[n]\}$ .                                                 |

| Figure 2.10 | ). Linearized behavioral model of the proposed $\Delta\Sigma$ -FDC where $\hat{g}[n] = \hat{g}_{\text{FDC}}$ |

|             | is approximated as constant6                                                                                 |

| Figure 2.11 | . (a) PLL's LTV model and (b) the FOHe and FOHo interpolation functions,                                     |

|             | $h^e_{\text{tri}}(t)$ and $h^o_{\text{tri}}(t)$ 6                                                            |

| Figure 2.12 | 2. Non-uniform linear interpolation between the $\theta_{\text{UTV}}[n]$ samples6.                           |

| Figure 2.13 | 3. (a) Block digital filtering technique, and (b) block digital filtering applied             |    |

|-------------|-----------------------------------------------------------------------------------------------|----|

|             | to the PLL's LTV phase noise model of Fig. 2.13(a)                                            | 55 |

| Figure 2.14 | 4. (a) PLL LTV phase noise model after applying the block digital filtering                   |    |

|             | technique, and (b) simplified representation.                                                 | 55 |

| Figure 3.1  | . (a) Top-level block diagram of a generic fractional-N PLL, and (b)                          |    |

|             | conventional PFD and CP operation (ideally, $I_N = I_P = I_{CP}$ )                            | 33 |

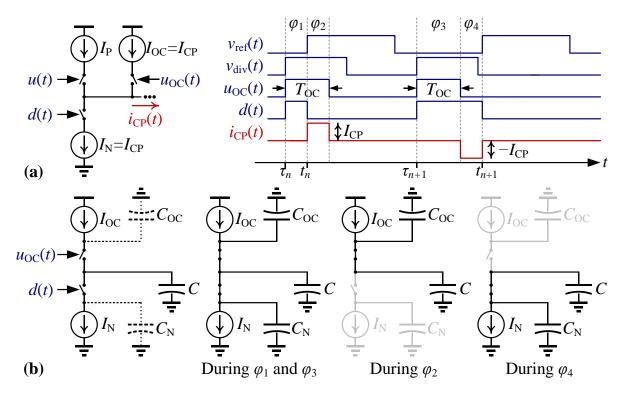

| Figure 3.2. | (a) Conventional offset-current CP linearization technique (ideally, $I_{\rm OC} = I_{\rm N}$ |    |

|             | = $I_{\rm CP}$ ), and (b) CP equivalent circuits during the different operation phases        |    |

|             | $arphi_{1	ext{-}4	ext{.}}$                                                                    | 34 |

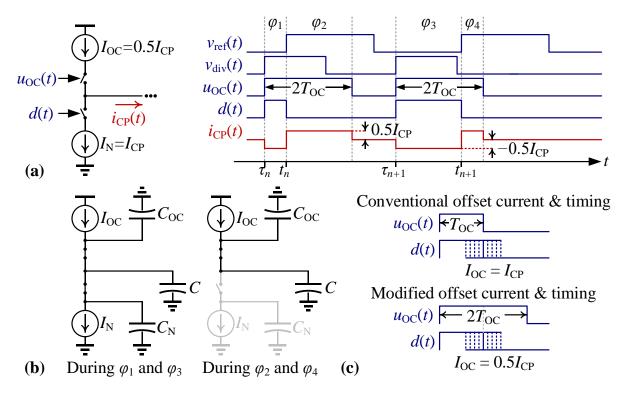

| Figure 3.3. | (a) Proposed offset-current linearization scheme (ideally, $I_N = I_{CP} = 2I_{OC}$ ),        |    |

|             | (b) CP equivalent circuits during $\varphi_{1-4}$ , and (c) conventional vs proposed          |    |

|             | schemes summary                                                                               | 35 |

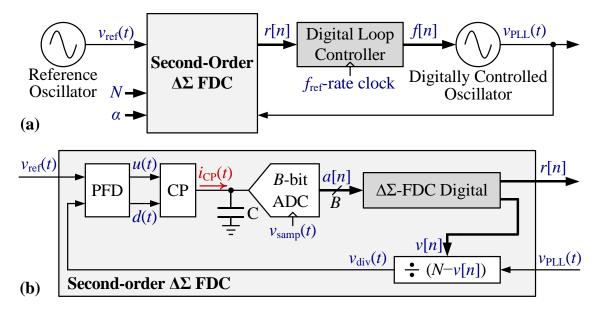

| Figure 3.4. | (a) A top-level block diagram for the PLL architecture, and (b) simplified                    |    |

|             | block diagram of the $\Delta\Sigma$ -FDC.                                                     | 35 |

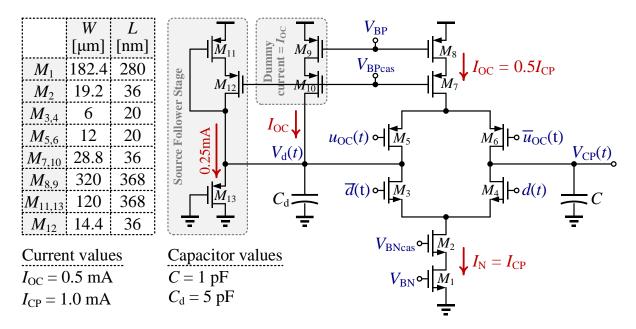

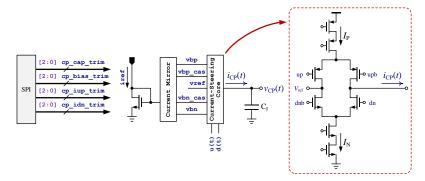

| Figure 3.5. | CP circuit implementation and device sizing.                                                  | 36 |

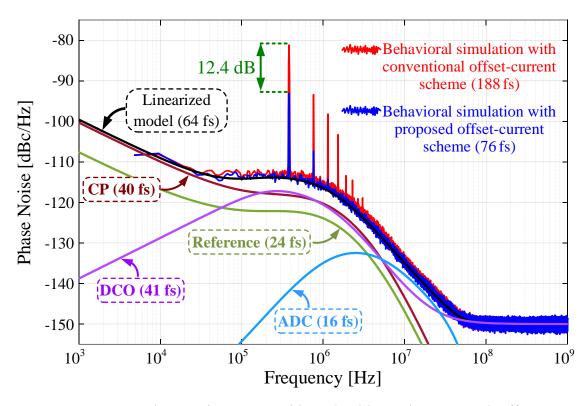

| Figure 3.6. | PLL's phase noise PSDs with and without the proposed offset current CP                        |    |

|             | linearization schemes, along with individual phase noise contributions                        |    |

|             | estimated from the PLL's linearized model.                                                    | 37 |

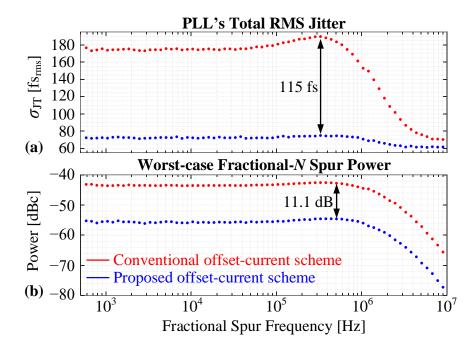

| Figure 3.7. | (a) Total integrated jitter, $\sigma_{JT}$ , and (b) power level of the largest measured      |    |

|             | fractional spur with and without the proposed offset current scheme for                       |    |

|             | fractional frequencies between 500 Hz and 10 MHz.                                             | 38 |

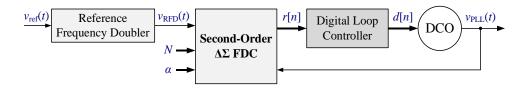

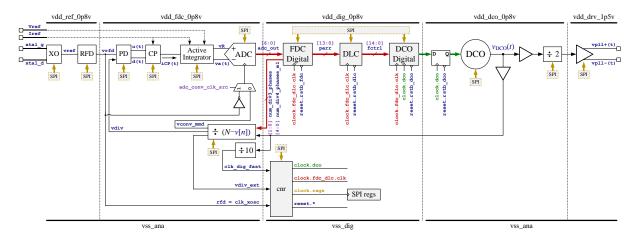

| Figure 4.1. | Top-level block-diagram of the proposed $\Delta\Sigma$ -FDC PLL architecture                  | 10 |

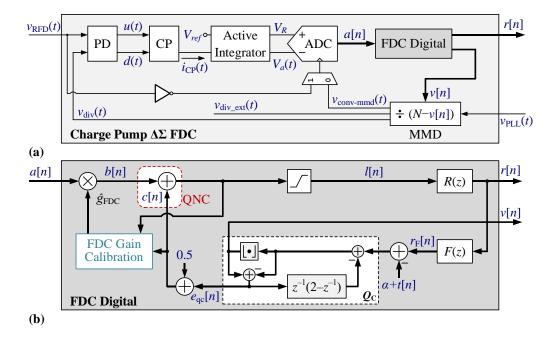

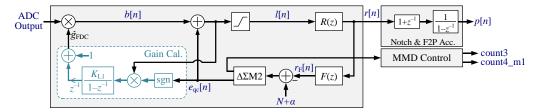

| Figure 4.2. (a) Top-level block-diagram of the proposed $\Delta\Sigma$ -FDC, and (b) FDC digital           |    |

|------------------------------------------------------------------------------------------------------------|----|

| details1                                                                                                   | 10 |

| Figure 4.3. PLL's top-level block-diagram1                                                                 | 11 |

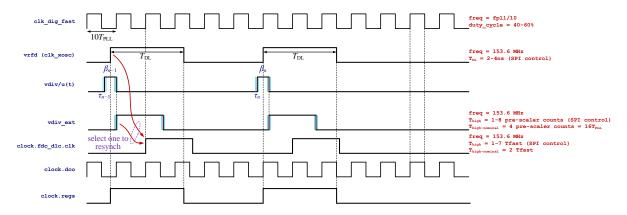

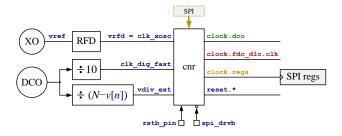

| Figure 4.4. PLL's CNR block main clock domains                                                             | 11 |

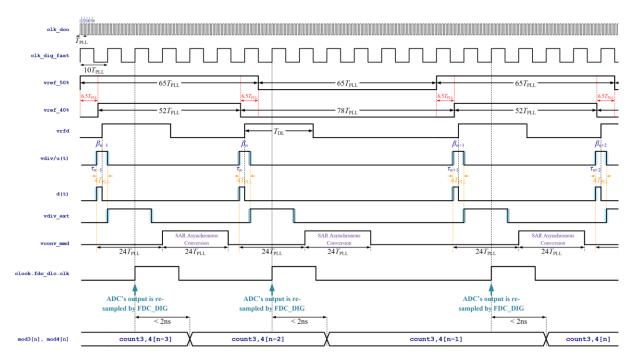

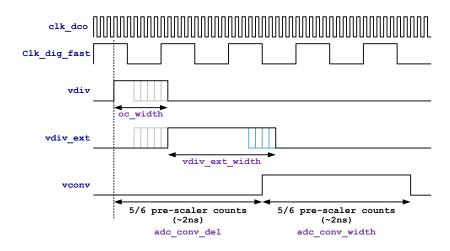

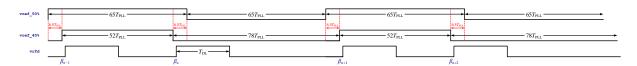

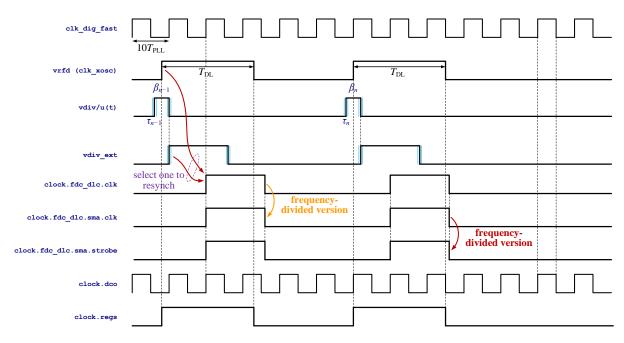

| Figure 4.5. Example timing diagram for the PLL at $f_{DCO} = 9.984$ GHz                                    | 12 |

| Figure 4.6. DCO topology                                                                                   | 12 |

| Figure 4.7. Top-level block-diagram for the MMD and clock generation circuitry1                            | 13 |

| Figure 4.8. Example output waveforms from the MMD and clock generation circuitry1                          | 13 |

| Figure 4.9. Timing diagram illustrating the timing constraints on the FDC digital and                      |    |

| MMD data sampling operation                                                                                | 13 |

| Figure 4.10. Reference signal generation configuration modes                                               | 14 |

| Figure 4.11. Crystal oscillator's Gm stage and reference buffer schematic                                  | 14 |

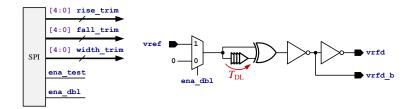

| Figure 4.12. RFD top-level diagram.                                                                        | 14 |

| Figure 4.13. Example waveforms for $v_{ref}(t)$ and $v_{RFD}(t)$ with $f_{ref} = 76.8$ MHz and $f_{PLL} =$ |    |

| 9.984GHz1                                                                                                  | 14 |

| Figure 4.14. PD implementation                                                                             | 14 |

| Figure 4.15. CP implementation.                                                                            | 15 |

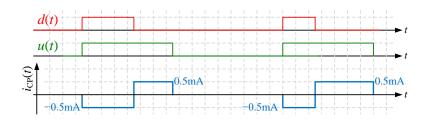

| Figure 4.16. CP control pulses and output current example waveforms                                        | 15 |

| Figure 4.17. Active integrator implementation details                                                      | 15 |

| Figure 4.18. 7-bit asynchronous top-sampling SAR ADC top-level architecture details. 1                     | 15 |

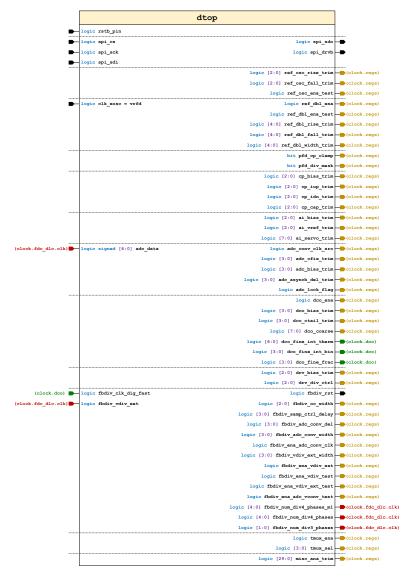

| Figure 4.19. PLL's main digital blocks, IOs, and clocking                                                  | 16 |

| Figure 4.20. the digital top IOs, grouped by block/functionality, and the respective port  |

|--------------------------------------------------------------------------------------------|

| clock domain                                                                               |

| Figure 4.21. CNR top-level block-diagram.                                                  |

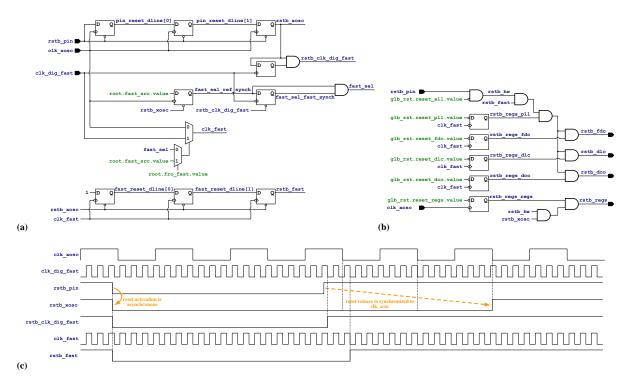

| Figure 4.22. (a) Local reset signals generation and fast clock source selection, (b) Reset |

| signals generation for different digital sub-blocks, and (c) Example                       |

| waveforms showing the asynchronous reset application and its synchronous                   |

| release117                                                                                 |

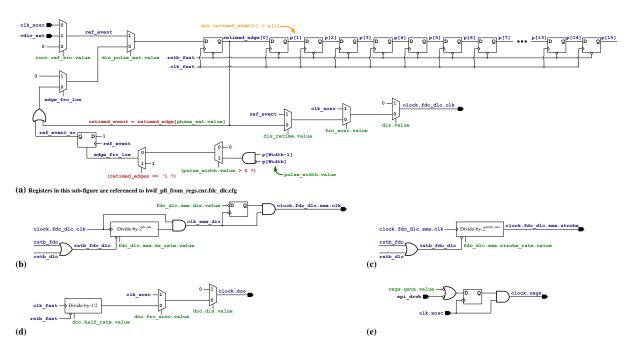

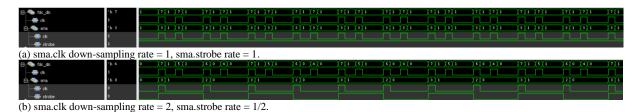

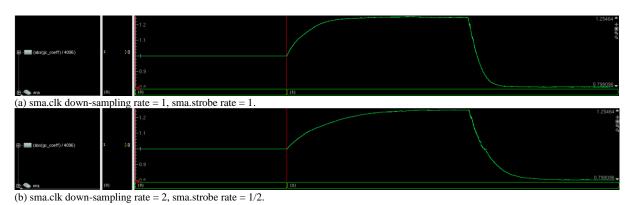

| Figure 4.23. Generation details of (a) clock.fdc_dlc, (b) clock.fdc_dlc.sma.clk, (c)       |

| clock.fdc_dlc.sma.strobe, (d) clock.dco, and (e) clock.regs118                             |

| Figure 4.24. Example waveforms for the different generated clocks from the CNR             |

| module118                                                                                  |

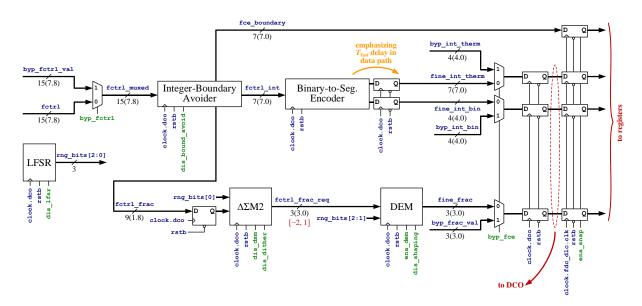

| Figure 4.25. FDC signal processing details                                                 |

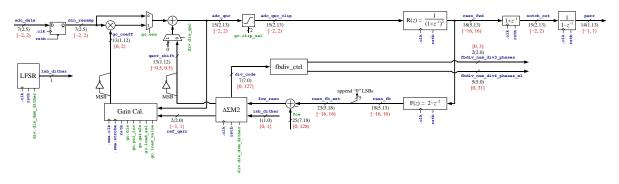

| Figure 4.26. FDC digital functional implementation details. N(u,w) indicates a bus-        |

| width of N bits interpreted as having u integer bits and w fractional bits 119             |

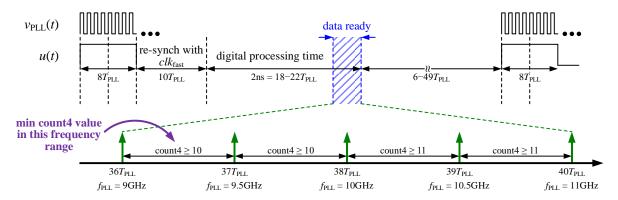

| Figure 4.27. MMD count3 and count4 values calculation. In this design $NB = 7$ and         |

| MIN_DIV4 is 10119                                                                          |

| Figure 4.28. DCO digital control signal processing details                                 |

| Figure 4.29. DCO digital functional implementation details. $N(u,w)$ indicates a bus-      |

| width of $N$ bits interpreted as having $u$ integer bits and $w$ fractional bits 120       |

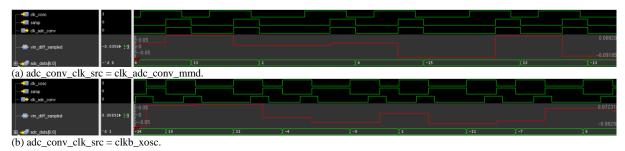

| Figure 4.30. Example waveforms showing clock.fdc_dlc generation                            |

| Figure 4.31. Example waveforms showing the two ADC clocking options                        |

| Figure 4.32. Example waveforms showing the FDC gain calibration clocking signals 120       |

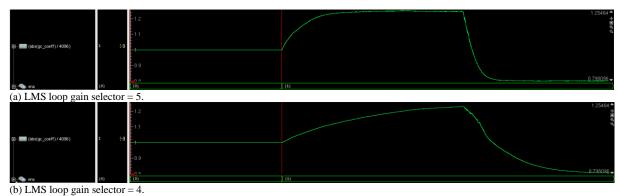

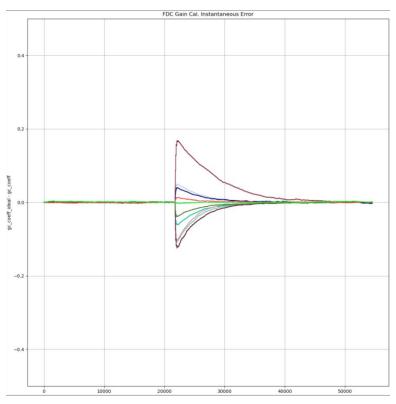

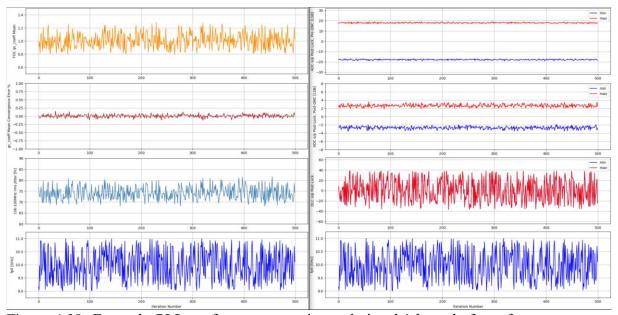

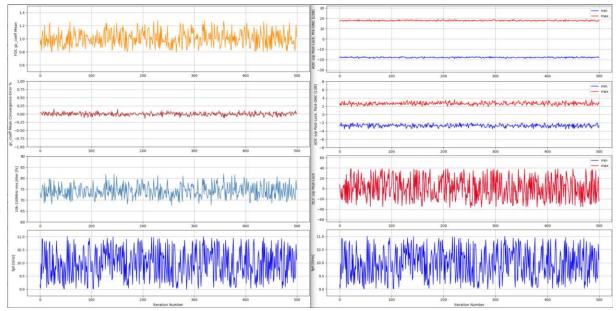

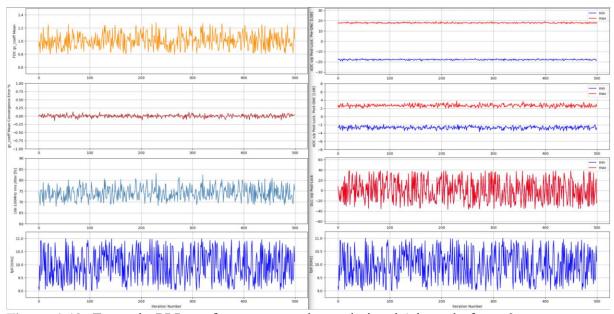

| Figure                                               | 4.33.                                                              | Example v     | vavefor  | ms showing       | the conve   | ergenc  | e of the    | FDC's      | gain |

|------------------------------------------------------|--------------------------------------------------------------------|---------------|----------|------------------|-------------|---------|-------------|------------|------|

|                                                      | ca                                                                 | libration lo  | op coe   | fficient under   | a step ch   | nange   | in the C    | P current  | for  |

|                                                      | dif                                                                | ferent LMS    | loop g   | ains             |             | •••••   |             |            | 121  |

| Figure                                               | 4.34.                                                              | Example v     | vavefor  | ms showing       | the conve   | ergenc  | e of the    | FDC's §    | gain |

|                                                      | ca                                                                 | libration loc | p coeff  | icient coefficie | ent under a | step c  | change in t | he CP cur  | rent |

|                                                      | for                                                                | r different c | locking  | options          |             | •••••   |             |            | 121  |

| Figure 4                                             | 1.35. E                                                            | xample wav    | veforms  | s showing the    | FDC's gai   | in cali | bration lo  | op coeffic | ient |

|                                                      | eri                                                                | or for rando  | om CP    | NMOS current     | steps (10   | PLL 1   | runs)       |            | 122  |

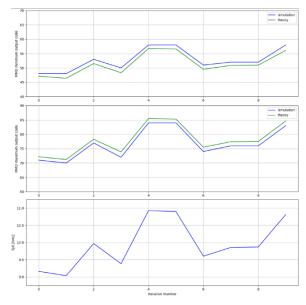

| Figure 4                                             | 1.36. T                                                            | heoretical v  | s simu   | lated minimun    | n and max   | imum    | divider's   | modulus    | (10  |

|                                                      | PL                                                                 | L runs)       |          |                  |             | •••••   | •••••       |            | 122  |

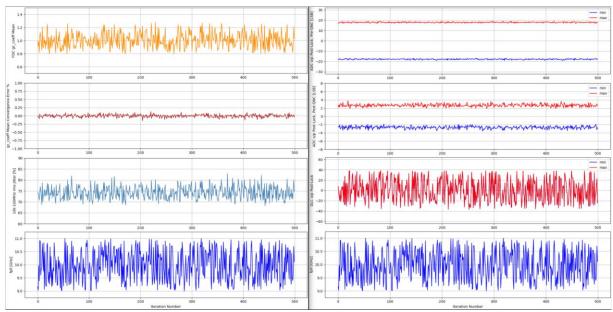

| Figure                                               | 4.37.                                                              | Example       | PLL      | performance      | metrics     | and     | signals'    | bounds     | for  |

|                                                      | ref                                                                | ference_eve   | nt = clk | xxosc and adc    | _conv_cll   | x = vrt | d_b         |            | 123  |

| Figure                                               | 4.38.                                                              | Example       | PLL      | performance      | metrics     | and     | signals'    | bounds     | for  |

|                                                      | reference_event = clk_xosc and adc_conv_clk = adc_conv_clk_mmd 123 |               |          |                  |             |         |             |            |      |

| Figure                                               | 4.39.                                                              | Example       | PLL      | performance      | metrics     | and     | signals'    | bounds     | for  |

| reference_event = vdiv_ext and adc_conv_clk = vrfd_b |                                                                    |               |          |                  |             |         |             |            |      |

| Figure                                               | 4.40.                                                              | Example       | PLL      | performance      | metrics     | and     | signals'    | bounds     | for  |

|                                                      | ref                                                                | erence_eve    | nt = vd  | iv_ext and adc   | _conv_cll   | x = ado | c_conv_cl   | k_mmd      | 124  |

# LIST OF TABLES

| Table 2.1. Contribution of different noise sources to the PLL's output    | 66  |

|---------------------------------------------------------------------------|-----|

| Table 2.2. PLL design parameters used for the behavioral simulation       | 66  |

| Table 2.3. Duty-cycle error convergence time comparison                   | 67  |

| Table 3.1. PLL design parameters used for the behavioral simulations      | 89  |

| Table 4.1. PLL target specifications                                      | 125 |

| Table 4.2. Target PLL design parameters and evaluation settings           | 126 |

| Table 4.3. DCO specifications summary                                     | 128 |

| Table 4.4. MMD specifications summary                                     | 128 |

| Table 4.5. Crystal oscillator specifications summary                      | 129 |

| Table 4.6. RFD specifications summary                                     | 129 |

| Table 4.7. PD specifications summary                                      | 129 |

| Table 4.8. CP specifications summary                                      | 130 |

| Table 4.9. Active Integrator specifications summary                       | 130 |

| Table 4.10. ADC specifications summary                                    | 131 |

| Table 4.11. CNR main inputs, outputs, and configuration signals           | 131 |

| Table 4.12. FDC's Digital main inputs, outputs, and configuration signals | 132 |

| Table 4.13. DLC main inputs, outputs, and configuration signals           | 132 |

| Table 4.14. DCO's Digital main inputs, outputs, and configuration signals | 132 |

#### ACKNOWLEDGEMENTS

All praise and gratitude are due to ALLAH. I dedicate this thesis to my father, who passed away two years ago. It is beyond comprehension how much I love and miss him. He is, unquestionably, my role model, and I will be pleased if I can follow in his footsteps in all aspects of life. No words can express how grateful I am for all what he taught me, and all the sacrifices he made for me and my family. His love, encouragement, advice, wisdom, strength, ethics, kindness, and support were invaluable to me throughout my life. Earning my PhD degree is all what he wished for. I'm sure that he would have been very happy and proud at this moment had he been with us. Thank you ... for everything.

I would like to thank Prof. Ian Galton for his generous financial support and meticulous technical supervision throughout my PhD studies. I thank him for his patience and understanding of the personal issues that I had to deal with over the course of the last few years. It would take pages to share the lessons I learned from him, but I would quote "never assume that what you hear or read is correct, think deeply about it first and try to come up with arguments to falsify it". Also, as ISPG graduates, we are lucky to inherit his academic genealogy and have David Hilbert as our academic fourth great-grandparent!!

I am grateful to have Prof. Peter Asbeck, Prof. Gert Cauwenberghs, and Prof. Truong Nguyen on my committee. My special thanks to Prof. Asbeck for recommending me to join the PhD program at UCSD. I was lucky to enroll in the last offering of his famous ECE265C course, before he retired, and learn about the world of Power Amplifiers.

I would like to thank Colin W. Wu, Eric Fogleman, Yiwu Tang, and Dongmin Park for their technical guidance and selfless sharing of their industry experience throughout my studies. Special thanks to Colin W. Wu for setting up the simulation platform and providing the SystemVerilog files used to generate the behavioral simulations in Chapter 4.

Next, the three heroines and two kids. First, my mother. I genuinely don't think motherhood can get any better. Her love, support, kind words, and strength are beyond imagination. In addition to the many things she did for our family, I owe her for helping with my studies since I was a kid, especially mathematics. During my stay in the US, my sister took care of my mother and father, filling the gap I left and more. I don't think I'll ever be able to thank her enough for that. Her support and love helped me overcome many of the challenges I had during my studies. Finally, my wife. She made a lot of sacrifices and stood with me against many challenges, especially during my PhD studies. She selflessly dedicated her life to our kids and to making us all happy. I always remind her that she shares this PhD title with me as many of the hours I spent working were only possible because she chose to do what I should have otherwise done. To my two beloved kids, thank you for giving meaning to what I am doing. I love you so much and will always be there for you.

I am in debt to Prof. Mohamed El-Nozahi, my master's advisor, who played a key role in shaping my career. I am grateful to have Dr. Samer Idres as a friend and mentor. Aside of his support, he never failed to recommend the finest dining places in Egypt and the US.

Moving to the ISPG members, I am grateful to get to know Enrique on my first day in the group. I enjoyed every moment in the countably infinite discussions we had. His critical reasoning and logical thinking process sharpened mine (so blame him if you find them messed up). He is a leader, always supportive and never fails to provide practical advice. I met Raghu next. I admire his knowledge and I enjoyed the discussions we had. Unfortunately, most of

them ended up with me realizing that I still must learn a lot to catch up with what he was saying, but I'm grateful for that. He indirectly taught me how to better understand technical material, and I benefited from his wise advice. He helped me deal with too many software-related issues, and his presence in the lab was certainly a privilege for all other lab members. Next comes Eslam whose hard work is a role model. He selflessly shared many of the industrial lessons he learnt with me, and discussions with him made me a better designer. I thank former lab members Mohamed Badr and the optimizer (a.k.a. Ahmed Hussein) for the discussions we had and the quality time we spent together. I wish both the best of luck in their current and future endeavors.

Finally, I would like to thank the Egyptian Mafia at UCSD (too many names to list :)). Special thanks to Mohammed Helal for his encouragement and support.

Chapter 1, in part, is currently being prepared for submission for publication of the material. A. I. Eissa, E. Alvarez-Fontecilla, E. Helal, I. Galton. The dissertation author is the primary investigator and author of this material. Professor Ian Galton supervised the research which forms the basis for this material.

Chapter 2, in full, is under review in the IEEE Transactions on Circuits and Systems I: Regular Papers. A. I. Eissa, E. Alvarez-Fontecilla, C. Weltin-Wu, I. Galton, 2024. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

Chapter 3, in part, is currently being prepared for submission for publication of the material. A. I. Eissa, I. Galton. The dissertation author is the primary investigator and author of this material. Professor Ian Galton supervised the research which forms the basis for this material.

# VITA

| 2024 | Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems), University of California San Diego, USA. |

|------|----------------------------------------------------------------------------------------------------------------------------|

| 2016 | Master of Science in Electrical Engineering, Ain Shams University, Cairo, Egypt.                                           |

| 2012 | Bachelor of Science in Electrical Engineering, Ain Shams University, Cairo, Egypt.                                         |

#### ABSTRACT OF THE DISSERTATION

Enhancement Techniques for Digital Phase-Locked Loops

by

## Amr Ibrahim Farag Eissa

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California San Diego, 2024

Professor Ian A. Galton, Chair

The performance of phase-locked loops (PLLs) is critical to advancing the data rates in wired and wireless communication systems. Most PLLs incorporate either analog filters and voltage-controlled oscillators (VCOs) or digital filters and digitally-controlled oscillators (DCOs). The former are called analog PLLs and the latter are called digital PLLs. To date, analog PLLs have the best phase error performance, but digital PLLs occupy smaller active area, lend themselves better to digital calibration and signal processing techniques, and are more

compatible with highly-scaled CMOS integrated circuit (IC) technology. Thus, improving the performance of digital PLLs has been the subject of intensive research for many years.

The first chapter of this dissertation presents an incremental frequency control (IFC) scheme for DCOs comprised of an arbitrarily large bank of unit-weighted frequency control elements (FCEs). The scheme requires only a pair of differential 1-bit control signals, is inherently monotonic, and avoids transient frequency glitches. Measurement results are presented to demonstrate the functionality of the proposed frequency control scheme and its negligible impact on a PLL's locking time and phase noise.

The second chapter of this dissertation presents a reference frequency-doubling (RFD) technique that is immune to crystal oscillator duty-cycle error and is not subject to the speed-accuracy trade-off associated with conventional duty-cycle error calibration techniques. The technique is presented and analyzed in the context of a delta-sigma frequency-to-digital converter ( $\Delta\Sigma$ -FDC) based PLL. Analysis and behavioral simulations with nonideal circuit parameters show a  $10\times$  improvement in the worst-case convergence time compared to prior art.

The third chapter of this dissertation describes a parasitic-capacitance-induced nonlinearity mechanism in charge pumps (CPs) used in fractional-N PLLs, along with a scheme to mitigate it. Presented in the context of a 10 GHz  $\Delta\Sigma$ -FDC based PLL, behavioral simulations with nonideal circuit parameters show that the proposed technique reduces the PLL's fractional spurs' level by more than 10 dB, achieving a worst-case in-band spur level below -54 dBc and an integrated RMS jitter below 80 fs.

The fourth chapter of this dissertation presents a system architecture review, along with behavioral simulation results, for a 9–11 GHz  $\Delta\Sigma$ -FDC PLL IC, targeting 75 fs<sub>rms</sub> jitter.

## **CHAPTER 1**

# AN INCREMENTAL FREQUENCY CONTROL SCHEME FOR DIGITALLY CONTROLLED OSCILLATORS

Abstract—The frequency of a digitally-controlled oscillator (DCO) is typically adjusted by changing the state of one or more of its frequency-control elements (FCEs), at specific times, via digital control signals. FCE banks comprised of power-of-two-weighted FCEs are attractive as they require small numbers of control signals, but they are sensitive to component and control signal propagation-delay mismatches that introduce nonlinearity and frequency glitches. Unit-weighted FCE banks are less prone to these issues. However, they require a relatively large number of control signals even when using row-column control schemes, in part, because redundant control signals are needed to avoid timing mismatches. This letter presents and experimentally demonstrates an incremental frequency control (IFC) scheme to control arbitrarily large banks of unit-weighted FCEs. The scheme requires only a pair of differential 1-bit control signals, and it avoids frequency glitches.

#### I. INTRODUCTION

Digital phase-locked loops (PLLs) have become increasingly popular over the last few decades [1], [2], [3], [4], [5], [6]. At the core of a digital PLL is a digitally-controlled oscillator (DCO) whose frequency is tuned through the digital control of a bank of frequency-control

elements (FCEs). Each FCE is driven by a 1-bit digital sequence, and the DCO's frequency is adjusted by changing the state of one or more FCEs at a time [7], [8], [9].

The choice of the FCE's frequency step-size (i.e., the amount by which the DCO's frequency changes when the FCE's input bit changes) is subject to a trade-off between the DCO's quantization-error contribution to the PLL's phase noise and tuning range. To simultaneously achieve low phase noise and wide tuning ranges, DCOs with small frequency step-size and a large number of FCEs (256 to 1024 elements) are typically implemented [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20], [21].

FCE banks comprised of power-of-two weighted elements require relatively small numbers of control signals, which is attractive as this reduces layout and routing complexity. Unfortunately, they suffer from non-monotonicities and propagation-delay timing mismatches between control signals, which introduce nonlinearity and frequency glitches [9], [13], [22]. In contrast, unit-weighted FCE banks require large numbers of control signals but are inherently monotonic and, in principle, immune to timing mismatches as the state of a single control signal changes at a time [9], [23]. Row-column control schemes reduce the number of signals needed to control unit-weighted banks [9], [11], [14], [15], [16]. However, to guarantee that only one of the row/column signals changes at a time, the number of control signals needed is still relatively large. For example, in [17], [18], and [19], 48 control lines were needed to control an 8-bit bank.

In this letter, an incremental frequency-control (IFC) scheme is presented for the control of unit-weighted FCE banks with arbitrary numbers of elements. The scheme uses a pair of differential 1-bit control signals where only one pair changes its state at a time, thus eliminating

timing-mismatch-related frequency glitches. Measurement results are presented to demonstrate the functionality of the proposed frequency control scheme and its negligible impact on a PLL's locking time and phase noise.

### II. FREQUENCY CONTROL IN DCOs

In digital PLLs, an  $f_{ref}$ -rate digital sequence is used to control the DCO's instantaneous frequency by adjusting the states of the individual FCEs in the DCO's FCE bank, where  $f_{ref}$  is the frequency of the PLL's reference oscillator [9], [24]. In applications that require low phase noise, the required DCO frequency step-size,  $\Delta$ , is in the order of tens of Hz, but practical existing FCEs have a typical minimum frequency step-size,  $\Delta_{min}$ , of tens of kHz [7], [8], [10], [12], [21], [25].

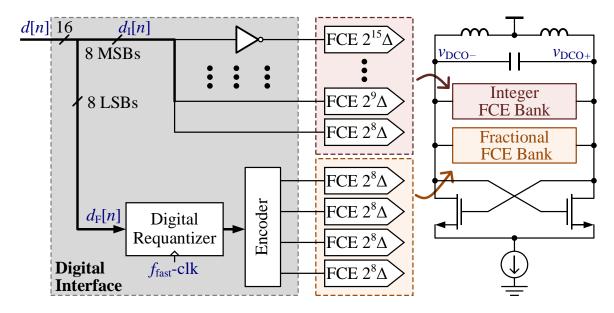

Fig. 1.1 illustrates a common solution to this problem presented in the context of a 16-bit LC-oscillator [10]. Each FCE adds to or subtracts from the overall tank capacitance, and the minimum FCE frequency step-size is  $\Delta_{\min} = 2^8 \Delta$ . The  $f_{\text{ref}}$ -rate sequence d[n] is split into two sequences,  $d_I[n]$  and  $d_F[n]$ , comprised of the eight MSBs and eight LSBs of d[n], respectively. The sequence  $d_I[n]$  directly controls a bank of power-of-two-weighted FCEs labeled *integer FCE bank*. To achieve frequency step-sizes smaller than  $\Delta_{\min}$ ,  $d_F[n]$  is re-sampled to  $f_{\text{fast}}$  (with  $f_{\text{fast}} > f_{\text{ref}}$ ), re-quantized, and the result is encoded to drive a unit-weighted FCE bank labeled fractional FCE bank. For instance,  $d_F[n]$  can be re-quantized by a second-order digital delta-sigma modulator and the encoder can be a simple binary-to-thermometer encoder. Changes in  $d_I[n]$  and  $d_F[n]$  cause the DCO frequency to change by integer and fractional multiples of  $\Delta_{\min}$ , respectively, which is why the integer and fractional FCE banks are labeled as such.

For a given  $\Delta_{\min}$ ,  $f_{\text{fast}}$  is chosen so that the digital re-quantization error does not degrade the PLL's phase noise. In addition, the integer FCE bank must be large enough to accommodate for the required DCO tuning range, typically in the range of tens of MHz. In [26], for instance, measured DCO frequency variations of about -200 kHz/°C are reported, so a 20 MHz tuning range would be needed to cover a 100 °C temperature range in such case. To meet both phase noise and tuning range requirements, FCE banks comprising 256 to 1024 unit elements are typically used [12], [14], [15], [16], [17], [18], [19], [20], [21].

The use of FCE banks comprised of power-of-two weighted FCEs allows for small numbers of control signals, which is convenient as this reduces routing complexity and the number of toggling digital lines routed near the DCO's tank. Ultimately, this reduces potential coupling of noise and spurious tones into the DCO output. Unfortunately, such FCE banks suffer from non-monotonicities and transient glitches that degrade a PLL's phase noise [9], [13], [21]. Non-monotonicities are more probable in power-of-two weighted banks with large number of elements and high mismatches between unit elements [9], [13], [23]. Unfortunately, this is the case with FCE banks as FCEs with small area and frequency step-size are needed to achieve fine frequency resolution and to minimize the phase noise degradation due to large routing-networks parasites. In addition, multiple control lines might need to toggle simultaneously, as in a 0...0011 to 0...0100 transition, and inevitable timing mismatches between the control lines result in transient glitches in the DCO output frequency.

Unit-weighted banks, in contrast, are inherently monotonic and immune to timing mismatches as only one control signal changes its state at a time [9], [23]. To mitigate the complexity associated with the large numbers of control signals needed by these banks, row-

column control schemes have been proposed. Such schemes have enabled, for example, the control of an 8-bit bank with as little as 16 digital control signals [10], [11], [12], [14]. The conventional row-column control approach, however, suffers from the timing mismatch problem because the change of state of corner units requires more than one control signal changing simultaneously [9], [17]. In [17], [18], and [19], different control signals are used for cells in even and odd columns to guarantee that a single control signal changes its state at a time. Unfortunately, this solution requires additional redundant control signals, increasing the number of control lines for an 8-bit bank, for example, to 48 lines.

#### III. PROPOSED IFC SCHEME

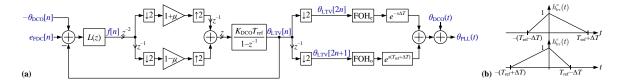

The proposed IFC scheme, shown in Fig. 1.2(a) in the context of an LC-DCO with an 8-bit unit-weighted integer FCE bank, both minimizes the number of control signals and ensures that the state of at most one control signal changes at a time [27]. The integer and fractional FCE banks in Fig. 1.2(a) are connected to the core of the LC oscillator as in Fig. 1.1, and the fractional FCE bank is controlled by  $d_F[n]$  as described in Section II. The integer FCE bank, comprised of unit-weighted FCEs, is controlled by a pair of 1-bit control signals,  $c_1[r]$  and  $c_2[r]$ , where only one of them changes its state at a time. This reduces the control and routing complexity of the bank, and eliminates timing mismatch related glitches.

## A. Qualitative Description

The proposed IFC scheme operates as follows. In unit-weighted banks, the number of FCEs with control bit of one must be equal to  $d_I[n]$ . Instead of directly driving the integer FCE

bank with  $d_I[n]$ , this sequence is first re-sampled to  $f_{fast}$ , producing  $d_I[r]$ . At each rising edge of the fast clock,  $d_I[r]$  is compared to the current number of FCEs being driven with a one, t[r-1], and the difference is used to compute the number of one-step increments or decrements that need to be issued so that  $t[r] = d_I[r]$ . The integer FCE bank is then updated by changing the state of at most one FCE per fast clock period, so only one  $f_{fast}$ -rate 1-bit control signal changes its state at a time.

Fig. 1.2(b) shows the integer FCE bank's top-level structure. As explained below, the layer of switches acts as an interface between  $c_1[r]$  and  $c_2[r]$  and the FCEs, and guarantees that at any given moment  $c_1[r]$  and  $c_2[r]$  are each connected to a single FCE. A change in the state of one of the control signals increments t[r] by one, and a change in the state of the other control signal decrements t[r] by one. The control signals  $c_1[r]$  and  $c_2[r]$  are generated within the DCO's digital interface which comprises an incremental-switching logic (ISL) block and a finite-state machine (FSM). The ISL generates the sequence  $d_1[r]$ , compares it to t[r-1], and outputs the sequence m[r] that takes on a value of -1, 0, or 1, commanding a decrease in the DCO's frequency by  $\Delta_{\min}$  (dn), no frequency change (noc), or an increase by  $\Delta_{\min}$  (up), respectively. The FSM generates  $c_1[r]$  and  $c_2[r]$ , each taking on a value of 0 or 1, based on m[r],  $c_1[r-1]$  and  $c_2[r-1]$ .

Fig. 1.2(c) shows  $d_I[n_t]$ ,  $m[r_t]$ , and how the FCEs' states change accordingly, where  $n_t$  = n over the nth period of the  $f_{ref}$ -rate clock that updates  $d_I[n]$  and  $r_t = r$  over the rth period of the  $f_{fast}$ -rate clock that updates m[r]. In this example,  $f_{fast} = 3f_{ref}$  and shaded boxes are used to

-

<sup>&</sup>lt;sup>1</sup> By definition,  $n_t$  is the largest integer less than or equal to  $f_{ref}t$  at time t, so it is a continuous-time waveform. Hence,  $d_I[n_t]$  is a continuous-time waveform even though  $d_I[n]$  is a discrete-time sequence. The same applies for  $m[r_t]$  and m[r] with n replaced by r, and  $f_{ref}$  replaced by  $f_{fast}$ .

indicate FCEs with a control bit of one. At  $t = kT_{ref}$ ,  $d_I[n_t]$  changes from 0 to 1 and so does  $m[r_t]$ , dictating FCE 1 to increase the DCO's frequency by  $\Delta_{min}$ . At  $t = kT_{ref} + T_{fast}$ ,  $m[r_t]$  goes low, signaling that no more FCE states need to be changed. The opposite happens between  $(k+1)T_{ref}$  and  $(k+2)T_{ref}$  where the state of FCE 1 is changed such the DCO's frequency decreases by  $\Delta_{min}$ . At  $t = (k+2)T_{ref}$ ,  $d_I[n_t]$  changes from 0 to 2. As the state of a single FCE changes at a time,  $m[r_t]$  stays high over two fast clock periods where the states of FCEs 2 and 3 are changed sequentially at  $t = (k+2)T_{ref}$  and  $t = (k+2)T_{ref} + T_{fast}$ , respectively.

## B. Architecture Details

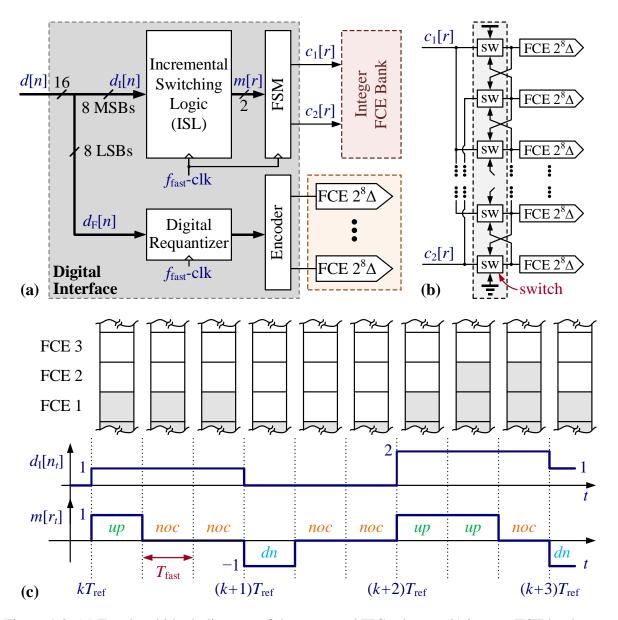

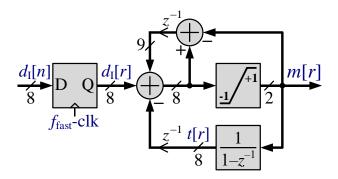

Fig. 1.3 shows the details of the ISL block. A flip-flop resamples  $d_1[n]$  at  $f_{\text{fast}}$  to generate  $d_1[r]$ . As m[r] = 1 indicates a frequency increment, t[r-1], is equal to the running sum of m[k] from k = 0 through k = r - 1. The result of  $d_1[r] - t[r-1]$  is clipped to  $\pm 1$  and a non-zero carry signal is generated if the required number of increments/decrements exceeds one, and adds to  $d_1[r]$  in the next cycle. It is worth noting that in high-performance PLLs, the frequency noise is significantly lower than  $\Delta_{\min}$  after locking, so  $d_1[n]$  should not change by more than  $\pm 1$  over a reference period in such case. Hence, the serialization of increments/decrements associated with the proposed scheme does not affect the PLL's operation or phase noise after locking. Moreover, as shown in Section V, the proposed scheme also has a negligible impact on a PLL's locking behavior.

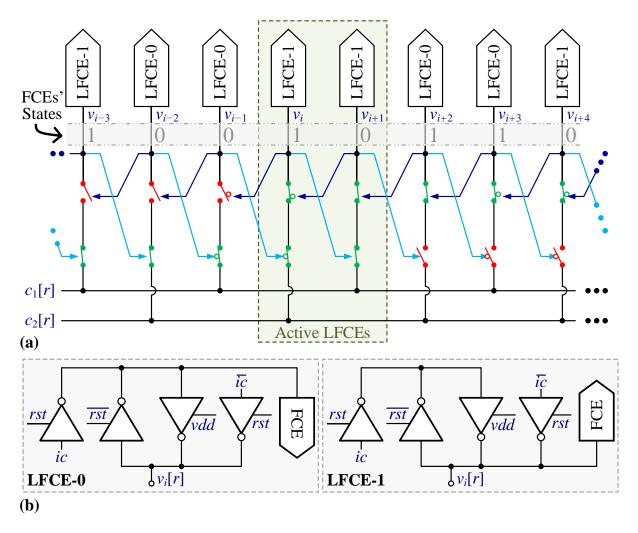

Fig. 1.4(a) shows the top-level diagram of an integer FCE bank architecture that is compatible with the IFC scheme, where LFCE stands for latched-FCE. An LFCE is a regular FCE whose control voltage,  $v_i[r]$ , is latched by a pair of cross-coupled tri-state inverters. Fig. 1.4(b) shows the topology of two types of LFCEs, LFCE-0 and LFCE-1, that are identical

except that in LFCE-0/1,  $v_i[r] = 0/1$  results in an increase in the DCO's frequency. Additionally, each LFCE has a pair of tri-state inverters that are enabled by a global reset signal (rst) and are used to initialize the bank to a hard-coded initial condition (ic). Each LFCE is connected to either  $c_1[r]$  or  $c_2[r]$  in an alternating fashion through two switches in series, with the top switch controlled by the state of the LFCE to the right and the bottom switch controlled by the state of the LFCE to the left. At any given moment, only two LFCEs, referred to as "Active LFCEs", are accessed by  $c_1[r]$  or  $c_2[r]$ , allowing for the state of a single FCE to change at a time. The LFCE topology makes sure that each FCE is properly initialized and preserves its control logic value when disconnected from its respective control signal.

To ensure that only one of  $c_1[r]$  and  $c_2[r]$  change its state at a time, the LFCE types are arranged in a ..., 1, 0, 0, 1, 1, 0, 0, 1, 1, 0, 0, 1, ... pattern, and the highlighted FCEs' states in Fig. 1.4(a) correspond to a scenario where the four FCEs to the left have a control bit of 1 and the four FCEs to the right have a control bit of 0. Consequently, the configuration of the series switches between each LFCE and either of the control signals follows a pattern that repeats every four branches. This pattern choice guarantees that at any given moment only two LFCEs are accessed by  $c_1[r]$  or  $c_2[r]$ , and for any transitioning LFCE, the LFCEs to its right and left have the same latched voltage. Hence, if  $c_1[r]$  were to change,  $c_2[r]$  does not have to change as the LFCE that is currently connected to  $c_2[r]$  and the LFCE that will be connected to  $c_2[r]$  when  $c_1[r]$  changes have the same latched voltage.

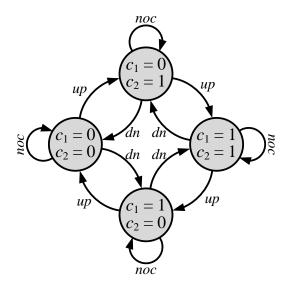

Fig. 1.5 shows the state-transition diagram of the FSM. It has four states corresponding to the possible combinations of  $c_1$  and  $c_2$  and generates  $c_1[r]$  and  $c_2[r]$ , each taking on a value of 0 or 1, based on m[r],  $c_1[r-1]$  and  $c_2[r-1]$ . As only one of the control signals changes at a

time, the two-bit binary word formed by concatenating  $c_1[r]$  and  $c_2[r]$  follows a Gray-encoder pattern. This is a result of the LFCEs pattern choice.

As the integer FCE bank architecture employs unit-weighted FCEs where the state of a single control signal and FCE are changed at a time, the IFC scheme is inherently monotonic and free of frequency glitches across the whole bank.

#### IV. IMPLEMENTATOIN DETAILS

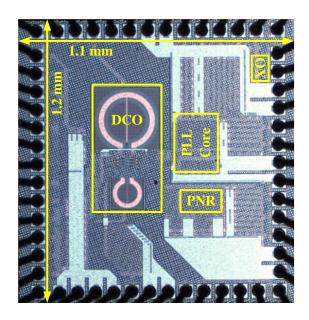

The IFC scheme was implemented as a modification to the digital fractional-*N* PLL presented in [20]. As the details of the PLL are explained in [20], only the additional implementation details relevant to the IFC scheme are presented here. The IC was implemented in the Global-Foundries 22-nm FDSOI process and consists of a digital fractional-*N* PLL, a serial peripheral interface (SPI), and additional circuitry used for testing. The PLL comprises five main blocks: crystal oscillator, core analog circuitry, place-and-route (PNR) digital block, DCO, and output drivers. All blocks run from a 0.8-V power supply, except for the output drivers that use a 1-V power supply.

## A. DCO Digital Interface

The DCO's digital interface has the form in Fig. 1.2(a), with the ISL block signal processing details shown in Fig. 1.3 and the FSM implementing the state-transition diagram in Fig. 1.5. The FSM outputs  $c_1[r]$  and  $c_2[r]$  and their inverted versions, enabling differential control for the integer FCE bank's unit cells. The digital re-quantizer in Fig. 1.2(a) is implemented as a successive re-quantizer with eight quantization blocks and first-order high-

pass shaped quantization error [28]. It generates an  $f_{\text{fast}}$ -rate sequence,  $c_{\text{F}}[r]$ , that takes on values of 0 or 1 and controls the state of a single FCE that plays the role of the fractional FCE bank (hence, no encoder is implemented). As in [20] and [26], an integer-boundary avoider can be incorporated at the interface between d[n] and  $d_{\text{I}}[n]$  and  $d_{\text{F}}[n]$  without affecting the proposed IFC scheme. The DCO digital interface circuitry is implemented as a part of the PLL's PNR digital block that is clocked at  $f_{\text{fast}}$ . The FSM and digital re-quantizer outputs are resynchronized to the fast clock within the PNR digital block before being routed to the DCO.

#### B. FCE Banks

The DCO core circuitry is the same as in [20] except for the FCE banks. The DCO has a single FCE playing the role of the fractional FCE bank and the integer FCE bank has the architecture in Fig. 1.4(a) and comprises 256 unit elements.

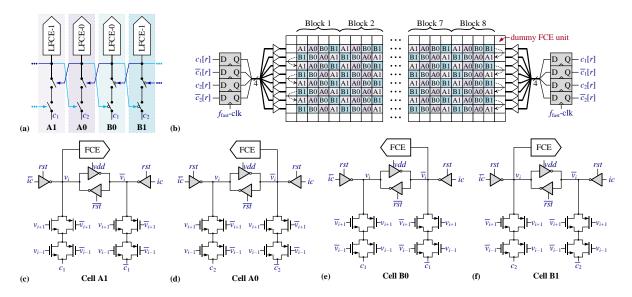

The integer FCE bank in Fig. 1.4(a) comprises blocks of four different unit cells that repeat across the bank. Fig. 1.6(a) highlights the four unit cells A1, A0, B0, B1, each controlled differentially by  $c_1[r]$ ,  $\overline{c_1}[r]$ ,  $c_2[r]$ , and  $\overline{c_2}[r]$ . The bank is laid out as illustrated in Fig. 1.6(b). The elements are placed in eight rows, each containing eight {A1, A0, B0, B1} blocks, and are surrounded by dummy FCEs to improve matching. The rows are connected in a zigzag manner as indicated by the dotted arrows between the B1 and A1 units at the bank's edges.

The control signals  $c_1[r]$ ,  $\overline{c_1}[r]$ ,  $c_2[r]$ , and  $\overline{c_2}[r]$  are routed close to each other from the digital PNR block to the bottom-middle part of the bank, and then in a tree-structured manner to both sides of the bank where they get resynchronized to the fast clock and buffered. The resynchronization aims to switch the state of the FCEs as close as possible to the DCO's differential zero-crossings to minimize disturbances to the tank's energy [10]. Routing the

control signals from both sides of the bank minimizes the delay from the control signals to the individual cells. Although not shown in Fig. 1.6(b), one of the dummy FCEs is used as the fractional FCE bank and is controlled by  $c_F[r]$  that is also locally resynchronized to the fast clock. The FCE banks occupy an area of  $120\times42~\mu\text{m}^2$ , compared to  $120\times30~\mu\text{m}^2$  in [20]. The banks are surrounded by a  $10-\mu$ m wide isolation region with reduced substrate doping.

## C. Integer FCE Bank Unit Cell

Figs. 1.6(c)-(f) show the circuit implementation details of cells A1, A0, B0, and B1, respectively. Each cell comprises an FCE unit, four tri-state inverters, and four switches. The four cells have the same topology except for the signals that control the switches and the FCE.

Initial conditions are hard-wired within each cell such that on reset one half of the FCE units add to the DCO capacitance. During initialization,  $c_1$  and  $c_2$  are set to 0 and 1, respectively, and one of the tri-state inverters in the latch is disabled to avoid fighting between latches in different cells that might occur as the switches settle to their desired configuration.

The tri-state inverters and switches sizing takes advantage of the FDSOI IC technology where the back gates of all PMOS transistors are tied to ground to reduce threshold voltages and increase speed. This allowed for the design of switches with equally-sized PMOS and NMOS transistors (aspect ratio of 420nm/20nm) and the use of minimum-sized standard-cell tri-state inverters, reducing the unit cell's area. The differential control of individual units reduces the coupling between the control signals and nearby interconnects. Also, it reduces the fighting between the latches within each unit cell and the control signal drivers at both sides of the bank, relaxing the drivers' speed and power requirements.

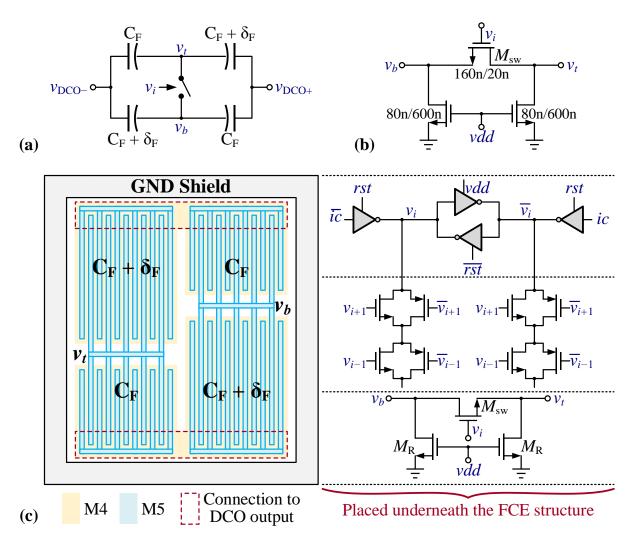

Fig. 1.7(a) and (b) show the FCE topology and its switch implementation, respectively [8]. Changing the gate voltage of  $M_{sw}$  changes the capacitance seen across nodes  $v_{DCO+}$  and  $v_{DCO-}$ , and the other two transistors are biased in the triode region to set the DC value of nodes  $v_t$  and  $v_b$ . Each FCE creates a simulated capacitance step of 63 aF, equivalent to  $\Delta_{min} = 137 \text{ kHz}$  at 6.7 GHz. The small incremental capacitance provided by the FCE structure results in a quality-factor over 200, allowing for the size of  $M_{sw}$  to be only 2× the minimum transistor size. The 256 units cover a simulated tuning range of 35 MHz.

Fig. 1.7(c) shows the layout of a unit cell in the integer FCE bank. The four capacitors are implemented as custom metal-oxide-metal (MOM) structures, and the circuitry is placed underneath them. Each of the capacitors is formed by sandwiching eleven metal 5 fingers between two metal planes drawn in metals 4 and 6. The blue drawing in Fig. 1.7(c) represents the metal 5 fingers, and the four yellow solid rectangles represent the metal 4 planes underneath the metal 5 fingers. Four metal 6 solid planes (not shown) atop the metal 5 fingers and aligned with the four metal 4 planes complete the structure for each of the capacitors. Rectangular stripes in metal 7 are used to tap the FCE terminals to the DCO outputs. As the FCE quality factor is high, metals 4 through 6 were chosen to build the capacitor, sparing the upper low-resistance metals for top-level routing to avoid degrading the DCO's tank quality factor. Metal 3 is used to form a ground shield around each unit, which minimizes the interaction between adjacent FCEs. Metals 1 and 2 are used for routing between all other circuitry underneath the FCE structure. Each unit cell occupies an area of  $2.9 \times 3.6 \, \mu m^2$ .

#### V. MEASUREMENT RESULTS

A die photograph of the prototype is shown in Fig. 1.8. The reference frequency,  $f_{ref}$ , is 80 MHz and  $f_{fast} = f_{PLL}/8 \approx 835$  MHz, which is synchronous to the DCO output. The measured power consumption of the integer FCE bank's digital circuitry is 67  $\mu$ W.

Fig. 1.9 shows a representative measured PLL phase noise profile at  $f_{PLL} = 6.67$  GHz for a PLL bandwidth of 550 kHz. The jitter and phase noise profile are in line with those reported in [20], indicating that the proposed IFC scheme has minimal impact on the PLL's phase noise. At 6.67 GHz, the measured DCO fine tuning range is 37.6 MHz corresponding to  $\Delta_{min} = 147$  kHz.

To evaluate the impact of the proposed IFC scheme on the PLL's locking behavior, the DCO's free-running frequency was set manually to 6.69 GHz and the PLL configuration was set such that when locked, the DCO frequency settles around 6.67 GHz. The DCO control was then switched back from manual control to the PLL, and the DCO's output frequency was recorded. The same experiment was replicated using behavioral simulations for two cases, one with ideal DCO control, i.e., the DCO frequency is d[n] scaled by  $2^{-8}\Delta_{\min}$ , and another with the IFC scheme. Fig. 1.10(a) shows the measured frequency settling behavior of the PLL and Fig. 1.10(b) shows the simulation results. These results show that the PLL's measured locking behavior is close to the predicted locking behavior from simulations, and they show that the locking behavior using the proposed IFC scheme is nearly identical to that with an ideal frequency control scheme.

Additional behavioral simulations were used to evaluate the impact of the IFC scheme on the PLL locking for different PLL initial conditions. Fig. 1.11(a) and (b) show histograms

of the PLL locking time using the proposed IFC scheme and an ideal control scheme, respectively, for 10,000 PLL runs. For each run, the PLL was initialized to have a random crystal oscillator initial phase and an initial DCO frequency error between -10 MHz and 10 MHz. For the results in Fig. 1.11(a) and (b), locking time is defined as the time after which  $d_1[n]$  does not change by more than  $\pm 1$  for at least 2000 consecutive reference cycles. The results show the same average locking time and statistics for both schemes. The difference in the locking times between the IFC scheme and the ideal DCO control scheme was also measured for each of the 10,000 PLL runs. Fig. 1.11(c) shows a histogram of the results, indicating an average locking time difference of 1.7 ns with a standard deviation of 0.2  $\mu$ s, thus verifying the negligible impact the IFC scheme has on the PLL's locking behavior.

#### VI. CONCLUSION

In this letter, an IFC scheme for DCOs tuning is presented. The scheme uses a pair of differential 1-bit control signals to control an arbitrarily large bank of unit-weighted FCEs, where at most one of the control signals changes its state a time. This guarantees monotonicity and eliminates frequency glitches typically caused by inevitable timing mismatches between multiple control signals. Measurement results are presented to validate the functionality of the proposed IFC scheme and verify the negligible impact it has on a PLL's locking behavior and phase noise.

# **ACKNOWLEDGEMENTS**

This chapter, in part, is currently being prepared for submission for publication of the material. A. I. Eissa, E. Alvarez-Fontecilla, E. Helal, I. Galton. The dissertation author is the primary investigator and author of this material. Professor Ian Galton supervised the research which forms the basis for this material.

# **FIGURES**

Figure 1.1. Conventional DCO frequency control technique.

Figure 1.2. (a) Top-level block diagram of the proposed IFC scheme, (b) integer FCE bank top-level structure, and (c) example waveforms for  $d_I[n_t]$  and the FSM output,  $m[r_t]$ , along with an illustration of the FCEs' states.

Figure 1.3. Incremental switching logic signal processing details.

Figure 1.4. Proposed integer FCE bank architecture compatible with the IFC scheme.

Figure 1.5. Incremental switching FSM state-transition diagram.

Figure 1.6. (a) The four main unit cells comprising the integer FCE bank, (b) integer FCE bank layout, and (c) - (f) circuit implementation details of unit cells A1, A0, B0, and B1, respectively.

Figure 1.7. (a) FCE circuit topology, (b) FCE switch implementation, and (c) integer FCE bank unit cell layout.

Figure 1.8. Die photograph.

Figure 1.9. Measured PLL phase noise at  $f_{PLL} = 6.67$  GHz for a 550-kHz loop bandwidth.

Figure 1.10. PLL frequency-settling vs time. (a) Measurement results, and (b) behavioral model simulation results.

Figure 1.11. (a), (b) PLL locking time histogram using the proposed IFC scheme and ideal DCO control, respectively, and (c) locking time difference histogram.

#### REFERENCES

- 1. C.-R. Ho and M. S.-W. Chen, "Smoothing the Way for Digital Phase-Locked Loops: Clock Generation in the Future with Digital Signal Processing for Mitigating Spur and Interference," in *IEEE Microwave Magazine*, vol. 20, no. 5, pp. 80-97, May 2019.

- 2. Y. -L. Hsueh *et al.*, "28.2 A 0.29mm2 frequency synthesizer in 40nm CMOS with 0.19psrms jitter and <-100dBc reference spur for 802.11ac," *2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC)*, San Francisco, CA, USA, 2014, pp. 472-473.

- 3. C. -W. Yao *et al.*, "A 14-nm 0.14-psrms Fractional-N Digital PLL With a 0.2-ps Resolution ADC-Assisted Coarse/Fine-Conversion Chopping TDC and TDC Nonlinearity Calibration," in *IEEE Journal of Solid-State Circuits*, vol. 52, no. 12, pp. 3446-3457, Dec. 2017.

- 4. S. Levantino, "Recent Advances in High-Performance Frequency Synthesizer Design," 2022 IEEE Custom Integrated Circuits Conference (CICC), Newport Beach, CA, USA, 2022, pp. 1-7.

- 5. F. Buccoleri *et al.*, "A 72-fs-Total-Integrated-Jitter Two-Core Fractional-N Digital PLL With Digital Period Averaging Calibration on Frequency Quadrupler and True-in-Phase Combiner," in *IEEE Journal of Solid-State Circuits*, vol. 58, no. 3, pp. 634-646, March 2023.

- 6. S. M. Dartizio *et al.*, "A Low-Spur and Low-Jitter Fractional-N Digital PLL Based on an Inverse-Constant-Slope DTC and FCW Subtractive Dithering," in *IEEE Journal of Solid-State Circuits*, vol. 58, no. 12, pp. 3320-3337, Dec. 2023.

- 7. R. B. Staszewski, Chih-Ming Hung, D. Leipold and P. T. Balsara, "A first multigigahertz digitally controlled oscillator for wireless applications," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 51, no. 11, pp. 2154-2164, Nov. 2003.

- 8. C. Venerus and I. Galton, "A TDC-Free Mostly-Digital FDC-PLL Frequency Synthesizer With a 2.8-3.5 GHz DCO," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 2, pp. 450-463, Feb. 2015.

- 9. B. Razavi, *Design of CMOS Phase-Locked Loops: From Circuit Level to Architecture Level*. Cambridge: Cambridge University Press, 2020.

- 10. R. B. Staszewski, D. Leipold, K. Muhammad and P. T. Balsara, "Digitally controlled oscillator (DCO)-based architecture for RF frequency synthesis in a deep-submicrometer CMOS Process," in *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 50, no. 11, pp. 815-828, Nov. 2003.

- 11. R. B. Staszewski, Chih-Ming Hung, N. Barton, Meng-Chang Lee and D. Leipold, "A digitally controlled oscillator in a 90 nm digital CMOS process for mobile phones," in *IEEE Journal of Solid-State Circuits*, vol. 40, no. 11, pp. 2203-2211, Nov. 2005.

- 12. L. Fanori, A. Liscidini and R. Castello, "3.3GHz DCO with a frequency resolution of 150Hz for All-digital PLL," 2010 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 2010.

- 13. I. Bashir, R. B. Staszewski and P. T. Balsara, "A Digitally Controlled Injection-Locked Oscillator With Fine Frequency Resolution," in *IEEE Journal of Solid-State Circuits*, vol. 51, no. 6, pp. 1347-1360, June 2016.

- 14. T. Pittorino, Y. Chen, V. Neubauer, T. Mayer and L. Maurer, "A UMTS-complaint fully digitally controlled oscillator with 100Mhz fine-tuning range in 0.13/spl mu/m CMOS," 2006 IEEE International Solid State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 2006.

- 15. J. Lin *et al.*, "A PVT tolerant 0.18MHz to 600MHz self-calibrated digital PLL in 90nm CMOS process," 2004 IEEE International Solid-State Circuits Conference (IEEE Cat. No.04CH37519), San Francisco, CA, 2004.

- 16. N. Da Dalt, E. Thaller, P. Gregorius and L. Gazsi, "A compact triple-band low-jitter digital LC PLL with programmable coil in 130-nm CMOS," in *IEEE Journal of Solid-State Circuits*, vol. 40, no. 7, pp. 1482-1490, July 2005.

- 17. N. Da Dalt, C. Knopf, M. Burian, T. Hartig and Hermann Eul, "A 10b 10GHz digitlly controlled LC oscillator in 65nm CMOS," 2006 IEEE International Solid State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 2006.

- 18. A. Elkholy, M. Talegaonkar, T. Anand and P. Kumar Hanumolu, "Design and Analysis of Low-Power High-Frequency Robust Sub-Harmonic Injection-Locked Clock Multipliers," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 12, pp. 3160-3174, Dec. 2015.

- 19. A. Elkholy, A. Elmallah, M. G. Ahmed and P. K. Hanumolu, "A 6.75–8.25-GHz –250-dB FoM Rapid ON/OFF Fractional-N Injection-Locked Clock Multiplier," in *IEEE Journal of Solid-State Circuits*, vol. 53, no. 6, pp. 1818-1829, June 2018.

- 20. E. Helal, E. Alvarez-Fontecilla, A. I. Eissa and I. Galton, "A Time Amplifier Assisted Frequency-to-Digital Converter Based Digital Fractional-N PLL," in *IEEE Journal of Solid-State Circuits*, vol. 56, no. 9, pp. 2711-2723, Sept. 2021.

- 21. E. Alvarez-Fontecilla, E. Helal, A. I. Eissa and I. Galton, "Spectral Breathing and Its Mitigation in Digital Fractional-N PLLs," in *IEEE Journal of Solid-State Circuits*, vol. 56, no. 10, pp. 3191-3201, Oct. 2021.

- 22. S. Akhtar, M. Ipek, J. Lin, R. B. Staszewski and P. Litmanen, "Quad Band Digitally Controlled Oscillator for WCDMA Transmitter in 90nm CMOS," *IEEE Custom Integrated Circuits Conference 2006*, San Jose, CA, USA, 2006.

- 23. Chi-Hung Lin and K. Bult, "A 10-b, 500-MSample/s CMOS DAC in 0.6 mm<sup>2</sup>," in *IEEE Journal of Solid-State Circuits*, vol. 33, no. 12, pp. 1948-1958, Dec. 1998.

- 24. R. B. Staszewski and P. T. Balsara, "Phase-domain all-digital phase-locked loop," in *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 52, no. 3, pp. 159-163, March 2005.

- 25. J. Zhuang, K. Waheed, and R.-B. Staszewski, "Design of spur-free frequency tuning interface for digitally controlled oscillators," IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 62, no. 1, pp. 46–50, Jan. 2015.

- 26. C. Weltin-Wu, G. Zhao and I. Galton, "A 3.5 GHz Digital Fractional- PLL Frequency Synthesizer Based on Ring Oscillator Frequency-to-Digital Conversion," in *IEEE Journal of Solid-State Circuits*, vol. 50, no. 12, pp. 2988-3002, Dec. 2015.

- 27. I. Galton, E. Alvarez-Fontecilla, and A. I. Eissa, "Frequency to digital converter, asynchronous phase sampler and digitally controlled oscillator methods," U.S. Patent 11437980, Sep. 6, 2022.

- 28. A. Swaminathan, A. Panigada, E. Masry and I. Galton, "A Digital Requantizer With Shaped Requantization Noise That Remains Well Behaved After Nonlinear Distortion," in *IEEE Transactions on Signal Processing*, vol. 55, no. 11, pp. 5382-5394, Nov. 2007.

# **CHAPTER 2**

# A DUTY-CYCLE-ERROR-IMMUNE REFERENCE FREQUENCY DOUBLING TECHNIQUE FOR FRACTIONAL-N DIGITAL PLLs

Abstract— Increasing a PLL's reference frequency offers significant performance advantages, but doing so by increasing the PLL's crystal oscillator frequency is not a viable option in many applications. Instead, a frequency doubler can be used to derive a reference signal with twice the frequency of the crystal oscillator, but conventional PLLs are highly sensitive to the crystal oscillator's duty cycle error in such cases. Prior solutions to this problem involve calibration techniques which impose convergence speed versus accuracy tradeoffs. In contrast, this paper proposes a system modification which makes a PLL immune to such duty cycle errors without the need for calibration. The technique is presented and analyzed in the context of a delta-sigma frequency-to-digital converter ( $\Delta \Sigma$ -FDC) based PLL. Analysis and behavioral simulations with nonideal circuit parameters show that the worst-case convergence time is at least 10 times faster than that of the prior techniques. Additionally, the proposed  $\Delta \Sigma$ -

Manuscript received 19 March 2024. This work was supported by Qualcomm, Analog Devices, and by the National Science Foundation under Award 1617545.

A. I. Eissa and I. Galton are with the Electrical and Computer Engineering Department, University of California, San Diego, La Jolla, CA 92092, USA (e-mail: <a href="mailto:aeissa@ucsd.edu">aeissa@ucsd.edu</a>). A. I. Eissa is also with the Electronics and Communications Engineering Department, Ain Shams University, Cairo, Egypt.

E. Alvarez-Fontecilla is with Analog Devices Inc., San Diego, CA 92128 USA and C. Weltin-Wu is with Aeonsemi, Inc., Santa Clara, CA 95134 USA.

FDC includes other modifications which improve its performance relative to comparable prior  $\Delta\Sigma$ -FDCs.

#### I. INTRODUCTION

Phase-locked loops (PLLs) are critical components in communication systems, and their performance requirements continue to increase as communication system standards evolve. In particular, the demand for PLLs with sub-100-fs rms jitter is increasing to enable higher data rates in wireless and wireline communication systems [1], [2], [3], [4], [5], [6]. Furthermore, reciprocal-mixing requirements in some wireless applications require PLLs with reference spurs below –80 dBc.

A PLL's phase noise spectrum usually is dominated by the phase noise of its controlled oscillator above the PLL's bandwidth and by noise from all other circuitry within the PLL's bandwidth.<sup>3</sup> The PLL's in-band phase noise consists of white and highpass shaped components, that are essentially sampled at the reference frequency,  $f_{ref}$ , so doubling  $f_{ref}$  for a given PLL bandwidth reduces the contribution to the PLL's phase noise of the white and first-order highpass shaped noise components by 3 dB and 9 dB, respectively [7]. This reduces the PLL's jitter by reducing the in-band noise, and makes it possible to further reduce the jitter by increasing the PLL's bandwidth to suppress the controlled oscillator's phase noise contribution over the wider bandwidth.

<sup>&</sup>lt;sup>3</sup> The controlled oscillator is a digitally-controlled oscillator in the case of a digital PLL and a voltage-controlled oscillator in the case of an analog PLL.

However, a PLL is generally but one component of a larger system, and its reference frequency is typically derived from the system's crystal oscillator. Unfortunately, the crystal oscillator frequency,  $f_{\text{crystal}}$ , is usually dictated by cost and system-level constraints, so increasing  $f_{\text{crystal}}$  is rarely an option when designing the PLL. Instead, a frequency doubler (FD), which uses the rising and falling edges of the crystal oscillator to generate a double-frequency reference signal, can be used to effectively double  $f_{\text{ref}}$ . The drawback of the approach is that crystal oscillators typically have duty cycle errors of 5 to 10% across process, voltage, and temperature (PVT) variations, and conventional PLLs with FDs are highly sensitive to such errors [8], [9], [10], [11], [12]. The duty-cycle error results in large spurs at integer-multiples of  $f_{\text{crystal}}$  and increase the PLL's jitter.

For example, a PLL with closed-loop bandwidth of 1.5 MHz with a 20dB/decade roll-off up to 76.8 MHz, a 10 GHz output frequency, and a 153.6 MHz reference signal from a 76.8 MHz crystal-oscillator with 5% duty-cycle error followed by an FD would have a -21.8 dBc spur at 76.8 MHz. This corresponds to 1.82 ps of jitter, not including any other error sources. Furthermore, the duty cycle error increases the dynamic range requirements of several of the PLL's circuit blocks, which generally increases their contributions to the PLL's phase noise and spurs.

Previously published techniques that address this problem rely on estimating the duty-cycle error in the analog or digital domains and canceling it through the crystal oscillator and FD analog circuitry, as in [13], [14], [15], [16], [17], and [18], or through the PLL's multi-modulus divider (MMD) as in [11], [12], [19], and [20]. However, these techniques are subject to a fundamental trade-off between convergence speed and accuracy. To sufficiently reduce

noise, the error estimation circuitry must have a small bandwidth, which leads to long convergence times. This tradeoff becomes more severe as the PLL's targeted jitter performance is improved.

A reference frequency-doubling (RFD) technique is presented in this paper which is immune to crystal oscillator duty-cycle error, so it is not subject to the speed-accuracy tradeoff of the prior solutions. It is presented and analyzed in the context of a delta-sigma frequency-to-digital converter ( $\Delta\Sigma$ -FDC) based PLL configured to achieve 75 fs rms jitter. Behavioral simulations with nonideal circuit parameters extracted from simulations of transistor-level PLL circuit blocks implemented in Global Foundries 22FDX 22 nm CMOS technology show that the worst-case convergence time is 412 reference cycles. This is at least  $10\times$  faster than that of the prior art with comparable initial duty-cycle errors and jitter. The presented  $\Delta\Sigma$ -FDC also includes a modified gain calibration technique and achieves reduced PFD and ADC spans after locking relative to comparable prior  $\Delta\Sigma$ -FDCs [21], [22].

#### II. REFERENCE FREQUENCY-DOUBLING IN PLLs

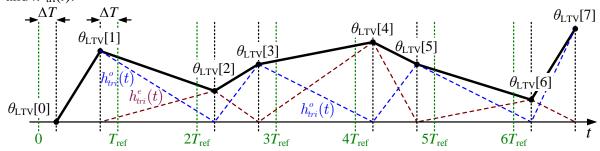

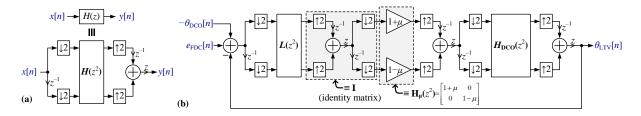

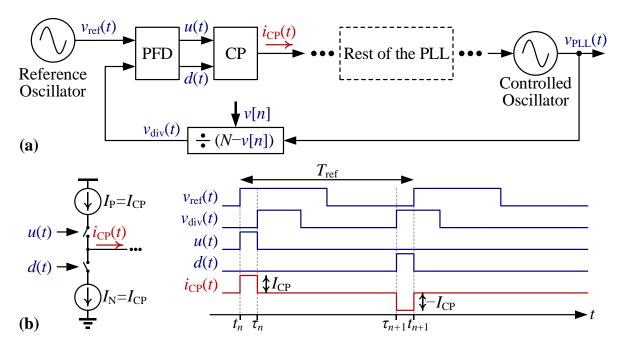

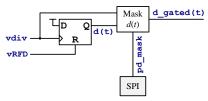

Fig. 2.1(a) shows a top-level block diagram of a generic fractional-N digital PLL where the reference signal,  $v_{ref}(t)$ , is generated by an FD, so the reference frequency,  $f_{ref}$ , is double that of the crystal frequency,  $f_{crystal}$ . The PLL is designed to generate a periodic output waveform,  $v_{PLL}(t)$ , with frequency  $f_{PLL} = (N+\alpha)f_{ref}$  where N is a positive integer and  $-\frac{1}{2} \le \alpha \le \frac{1}{2}$ . It consists of a phase-error to digital converter (PEDC), a digital loop filter (DLF), and a digitally controlled oscillator (DCO). The PEDC output, p[n], is a quantized measure of the PLL's phase error and the DCO's frequency control sequence, d[n], is a lowpass filtered version of p[n].