**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

# Analyses of Dynamic Element Matching Techniques for Data Conversion

A dissertation submitted in partial satisfaction of the requirements for the degree  ${\bf Doctor\ of\ Philosophy}$

in Electrical and Computer Engineering (Communication Theory & Systems)

by

Henrik Tholstrup Jensen

#### Committee in charge:

Professor Ian Galton, Chair Professor LeRoy Dorman Professor William Hodgkiss Professor Larry Larson Professor Paul Siegel UMI Number: 9732715

UMI Microform 9732715 Copyright 1997, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

300 North Zeeb Road Ann Arbor, MI 48103

Copyright ©

Henrik Tholstrup Jensen, 1997

All rights reserved

To my Parents...

### TABLE OF CONTENTS

|    | Signature Page                                                                      | iii |

|----|-------------------------------------------------------------------------------------|-----|

|    | Dedication                                                                          | iv  |

|    | Table of Contents                                                                   | v   |

|    | List of Figures                                                                     | vi  |

|    | Preface                                                                             | ix  |

|    | Acknowledgments                                                                     | x   |

|    | Vita and Publications                                                               | xii |

|    | Abstract of the Dissertation                                                        | xiv |

| 1. | A Low-Complexity Dynamic Element Matching DAC for Direct Digital Synthesis          | 1   |

| 2. | An Analysis of the Partial Randomization Dynamic Element Matching Technique         | 38  |

| 3. | Yield Estimation of a Second-Order $\Delta\Sigma$ ADC Employing a Noise-Shaping DAC | 70  |

### LIST OF FIGURES

|      | Chapter 1                                                                                                                                                  |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

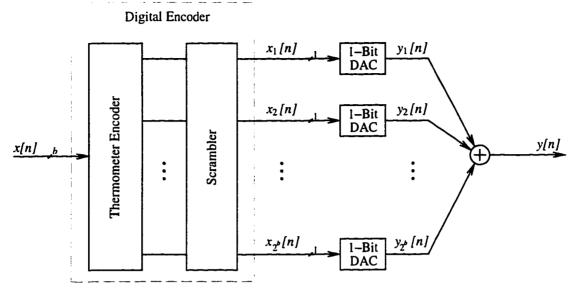

| 1.1  | The high-level topology of the low-harmonic distortion DACs presented in [2] and [4]                                                                       | 4  |

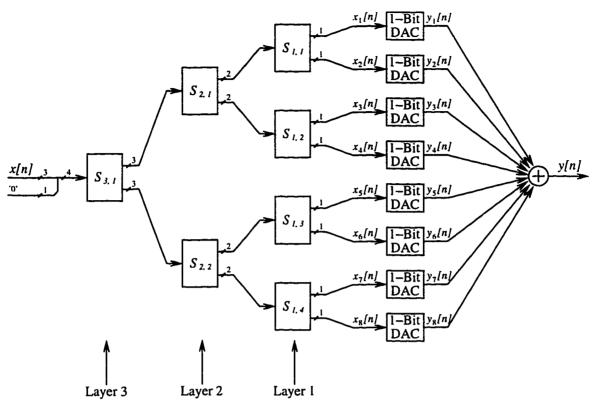

| 1.2  | A 3-bit version of the proposed DAC architecture                                                                                                           | 6  |

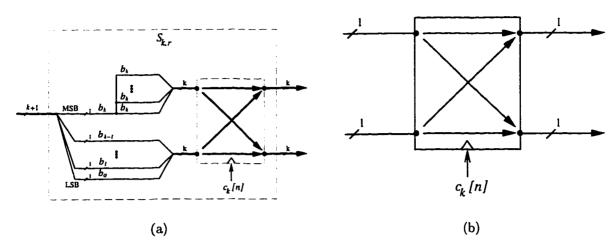

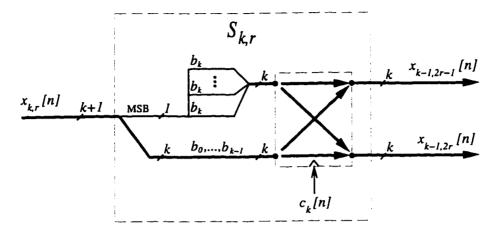

| 1.3  | Details of (a) the switching block $S_{k,r}$ , and (b) the binary switch                                                                                   | 7  |

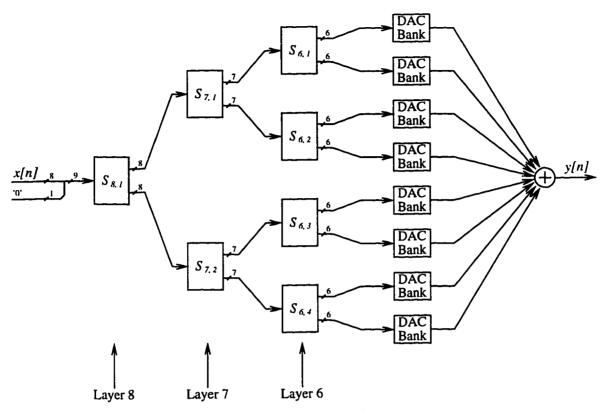

| 1.4  | An 8-bit DAC with partial randomization DEM                                                                                                                | 9  |

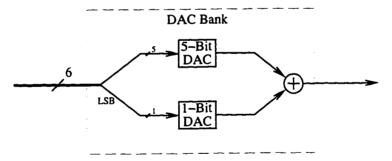

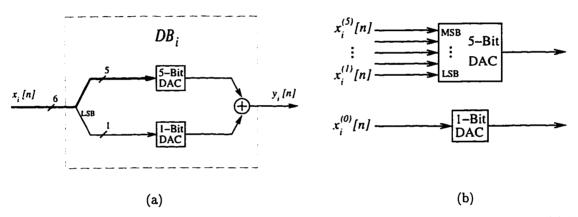

| 1.5  | Details of the DAC bank                                                                                                                                    | 9  |

| 1.6  | Simulated PSDs relative to $x_{max}^2$ of an example 8-bit DAC                                                                                             | 10 |

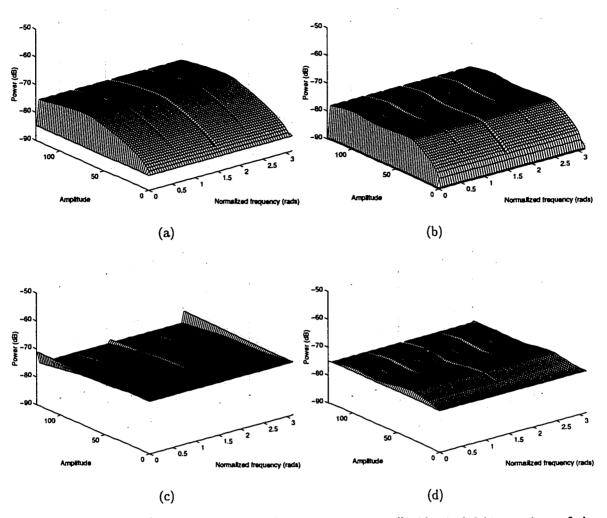

| 1.7  | Plots of $\overline{\sigma}^2$ in dB relative to $x_{max}^2$ for four nominally identical 8-bit versions of the proposed DAC                               | 15 |

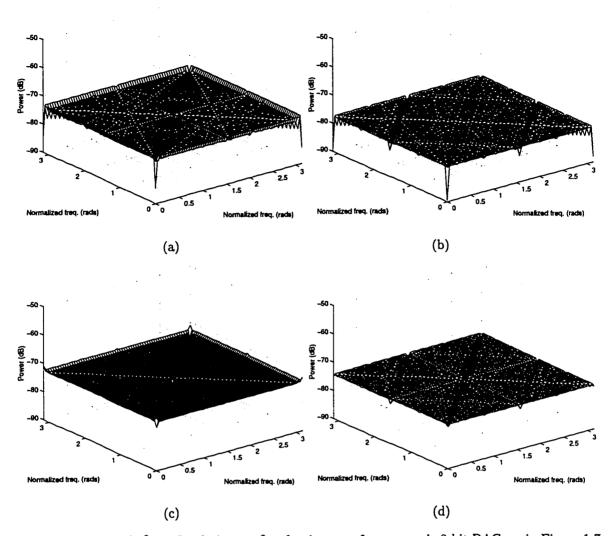

| 1.8  | Plots of $\overline{\sigma}^2$ in dB relative to $x_{max}^2$ for the same four example 8-bit DACs as in Figure 1.7 when driven by the sum of two sinusoids | 16 |

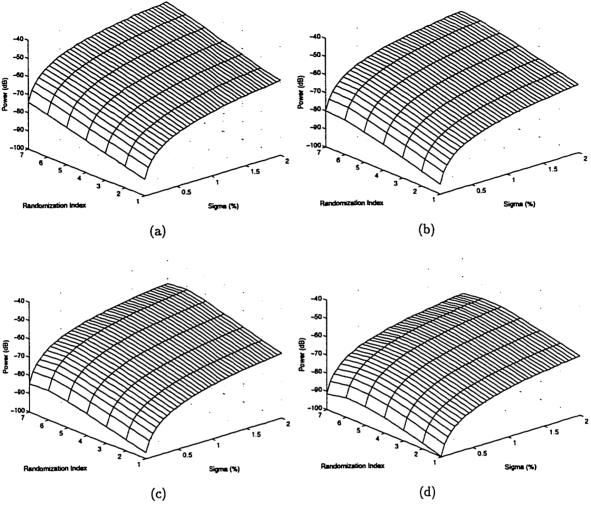

| 1.9  | IC fabrication yield estimation data for (a) 4-bit, (b) 6-bit, (c) 8-bit, and (d) 10-bit versions of the proposed DAC                                      | 17 |

| 1.10 | Simulated PSDs relative to $x_{max}^2$ of an example 8-bit DAC with partial randomization DEM                                                              | 20 |

| 1.11 | Digital hardware required to implement the digital encoders presented in [2] and of the proposed architecture versus the DAC bit-resolution                | 22 |

| 1.12 | Hardware complexity versus the range of layers with random switching of an example 8-bit digital encoder                                                   | 23 |

| 1.13 | The signal processing equivalent of the switching block $S_{k,r}$                                                                                          | 25 |

|      | Chapter 2                                                                                                                                                  |    |

| 2.1  | An 8-bit version of the proposed DAC architecture with randomization index $I=3$                                                                           | 41 |

| 2.2  | Details of the switching block of the $k^{\text{th}}$ layer                                                                                                | 42 |

| 2.3  | Details of the DAC-bank corresponding to the example 8-bit DAC of Figure 2.1                                                                                                | 42 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

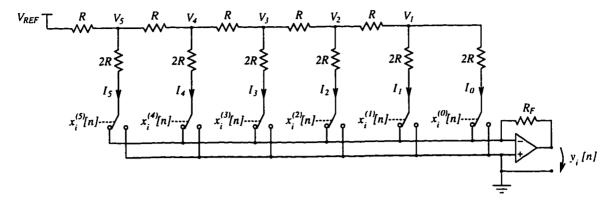

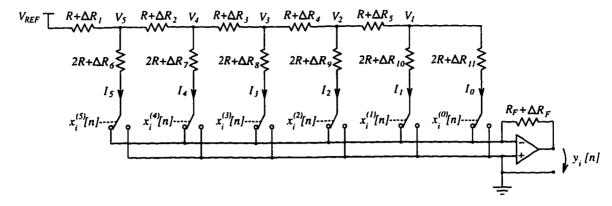

| 2.4  | An implementation of the DAC-bank using an (ideal) $R-2R$ ladder network                                                                                                    | 43 |

| 2.5  | The DAC-bank implemented using an $R-2R$ ladder network with resistor errors and non-zero ohmic switch resistance                                                           | 46 |

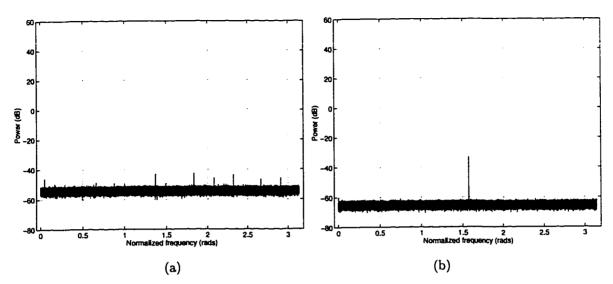

| 2.6  | Simulated PSDs relative to $x_{max}^2$ of an example 8-bit DAC implemented using $R-2R$ ladder network DAC-banks                                                            | 47 |

| 2.7  | Simulated PSD relative to $x_{max}^2$ of selected signals of the example 8-bit DAC used for Figure 2.6d                                                                     | 52 |

| 2.8  | An IC fabrication yield estimation of the minimum SFDR of the 8-bit version of the DAC implemented using $R-2R$ ladder network DAC-banks                                    | 55 |

| 2.9  | Simulated PSDs of $e[n]$ relative to $x_{max}^2$ of the example 8-bit DAC                                                                                                   | 57 |

| 2.10 | An IC fabrication yield estimation of $\overline{\sigma}^2$ in dB relative to $x_{max}^2$ of the 8-bit version of the DAC implemented using $R-2R$ ladder network DAC-banks | 58 |

|      | Chapter 3                                                                                                                                                                   |    |

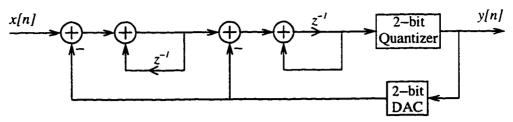

| 3.1  | The architecture of the second-order $\Delta\Sigma ADC$                                                                                                                     | 72 |

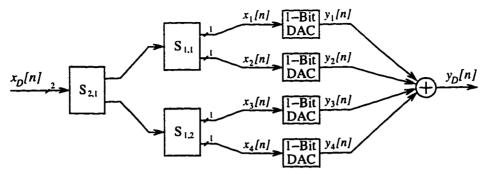

|      | The architecture of the 2-bit noise-shaping DAC                                                                                                                             | 73 |

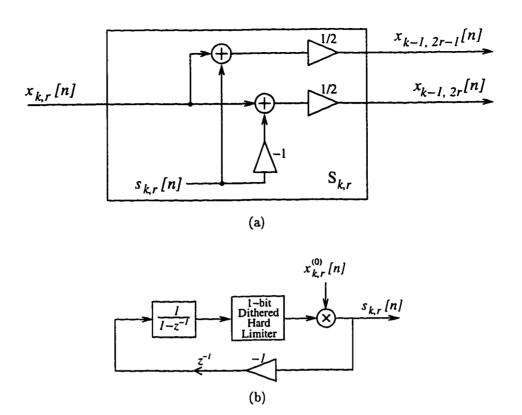

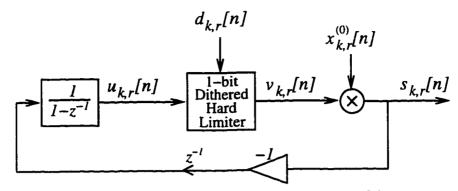

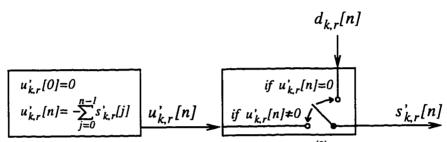

| 3.3  | (a) The general form of the switching blocks. (b) Details of the generation of the switching sequence $s_{k,r}[n]$                                                          | 74 |

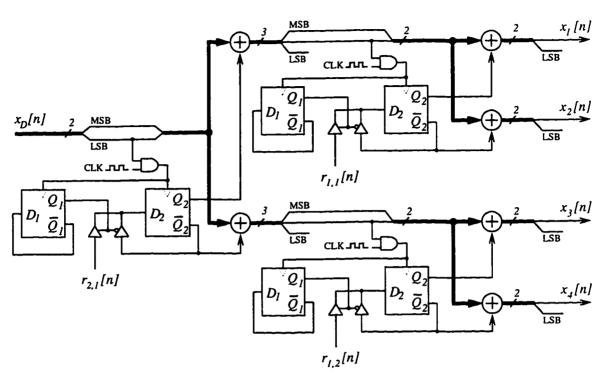

| 3.4  | A hardware-efficient gate-level implementation of the 2-bit DAC                                                                                                             | 75 |

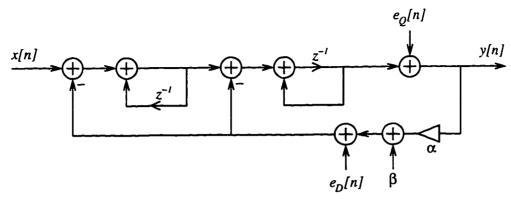

| 3.5  | The signal-processing equivalent of the second-order $\Delta\Sigma ADC$ of Figure 3.1                                                                                       | 77 |

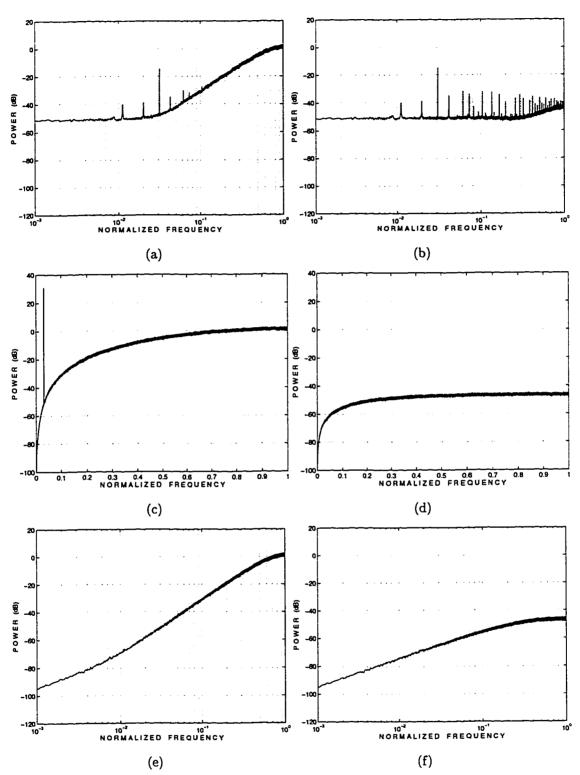

| 3.6  | Simulated PSDs of the second-order $\Delta\Sigma ADC$                                                                                                                       | 79 |

| 3.7  | Theoretically computed PSDs of the second-order $\Delta\Sigma ADC$ plotted against logarithmic scales                                                                       | 82 |

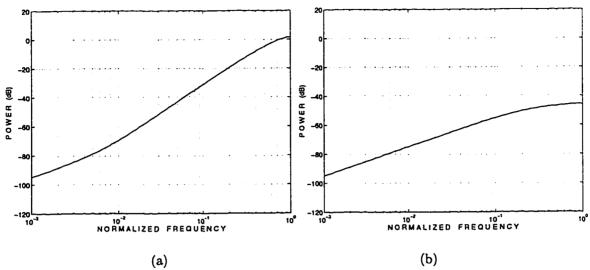

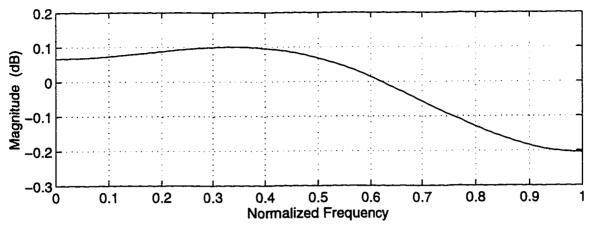

| 3.8  | Typical magnitude response of the equalization filter $E(z)$                                                                                                                | 84 |

| 3.9  |                                                                                                                                                                             |    |

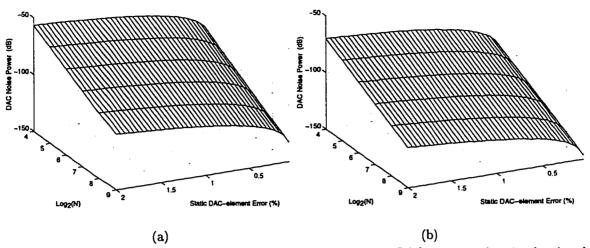

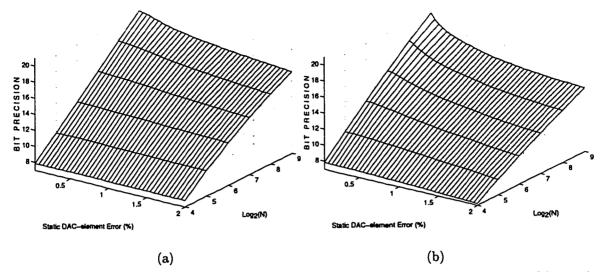

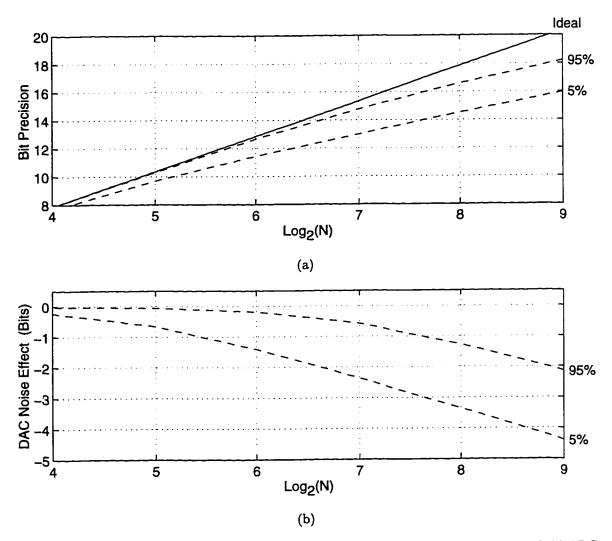

| 3.10 | An IC fabrication yield estimation of the $\Delta\Sigma$ ADC conversion bit-precision, $R$ | 88 |

|------|--------------------------------------------------------------------------------------------|----|

| 3.11 | A quantification of the detrimental effects of the DAC noise                               | 89 |

| 3.12 | The details of the generation of the switching sequences $s_{k,r}[n]$                      | 96 |

| 3.13 | A signal-processing equivalent of Figure 3.12 when $x_{k,r}^{(0)}[n] = 1$                  | 96 |

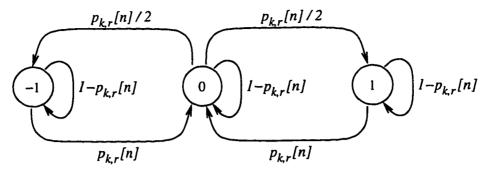

| 3.14 | A state transition diagram for $s_{k,r}[n]$                                                | 99 |

#### **PREFACE**

This dissertation is a collection of three papers that are intended for separate publication in *IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing*, each paper forming a separate chapter of the dissertation. Specifically, the first paper has been reviewed by the IEEE, revised, and accepted for publication, the second paper has been submitted to the IEEE for review, and the third paper is in preparation for review, and is in large ready for submission. Furthermore, the research covered in Chapter 1 has been presented at the 1996 IEEE International Symposium on Circuits and Systems, May 12-15, 1996, Atlanta, Georgia, and the research covered in Chapters 2 and 3 is to be presented at the 1997 IEEE International Symposium on Circuits and Systems, June 9-12, 1997, Hong Kong.

#### **ACKNOWLEDGMENTS**

First and foremost, I would like to thank Ian Galton, my advisor and close friend, for his continued guidance, support, and encouragement throughout this endeavor. I have indeed been very fortunate to have him for my advisor and teacher during my years in graduate school. His engineering ingenuity, command of the technical topics, and abilities as a teacher are nothing less than exceptional. At the personal level, his concern about my well-being during my student career has gone far beyond the call of duty. No expenses have been spared in terms of financial support, state-of-the-art equipment, and funding for participation in relevant technical conferences, in order to provide me with the optimal environment to perform research and to give me the full doctoral student experience.

Also many thanks to the rest of the Galton family; wife Kerry, daughter Riley, and son Mitchell, for their warm friendship and for excellent company on the many dinner trips to the Souplantation and other fine dining establishments...

I am grateful to Professors LeRoy Dorman and William Hodgkiss of the Scripps Institution of Oceanography, UCSD, and to Professors Larry Larson and Paul Siegel of the Department of Electrical and Computer Engineering, UCSD, for serving on the doctoral committee. I am also highly appreciative of the competence and professional, positive attitude exhibited by the staff of the Department of Electrical and Computer Engineering, UCSD, throughout my stay here.

This work was supported in part by the National Science Foundation under Grants MIP-9309656 and EEC-9320381.

Finally I wish to thank the Fulbright Commission of Denmark for its services and advice provided in the years of 1991 and 1992 when I applied to graduate school in the U.S., and thanks goes to the Knud Højgaard Foundation, the Radio-Parts

Foundation, the Denmark-America Foundation, the International Services Office of Odense University, and the Jacobsen Foundation (Risingskolen, Odense) for their generous support during my initial years in the U.S..

Chapter Acknowledgment: The text of Chapter 1, in part or in full, consists of the material that will appear as a "Regular Paper" in a future edition of *IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing.* The dissertation author was the primary researcher and the co-author listed in the publication directed and supervised the research which forms the basis for the chapter.

# VITA

| March 16, 1968 | Born, Odense, Denmark                                                                                                                                                                               |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1992           | Bachelor of Science, Odense University, Odense, Denmark                                                                                                                                             |

| 1992-1993      | Fulbright Scholar and Teaching Assistant, Department of Electrical and Computer Engineering, University of California, Irvine                                                                       |

| 1993-1994      | Research Assistant, Department of Electrical and Computer Engineering, University of California, Irvine                                                                                             |

| 1994           | Master of Science, University of California, Irvine                                                                                                                                                 |

| 1994-1997      | Research Assistant, Department of Electrical and Computer Engineering, University of California, Irvine, and Department of Electrical and Computer Engineering, University of California, San Diego |

| 1997           | Doctor of Philosophy, University of California, San Diego                                                                                                                                           |

#### **PUBLICATIONS**

- H. T. Jensen, I. Galton, "Yield estimation of a second-order  $\Delta\Sigma$ ADC employing a noise-shaping DAC," *IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, in preparation.

- H. T. Jensen, I. Galton, "An analysis of the partial randomization dynamic element matching technique," *IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, under review.

- H. T. Jensen, I. Galton, "A low-complexity dynamic element matching DAC for direct digital synthesis," *IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, accepted for publication.

- I. Galton, H. T. Jensen, "Oversampling parallel delta-sigma modulator A/D conversion," *IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, vol. 43, no. 12, pp. 801-810, December 1996.

- I. Galton, H. T. Jensen, "Delta-sigma modulator based A/D conversion without oversampling," *IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing*, vol. 42, no. 12, pp. 773-784, December 1995.

- H. T. Jensen, I. Galton, "Yield estimation of a first-order noise-shaping D/A converter," *IEEE Proceedings of the International Symposium on Circuits and Systems* 1997, ISCAS 1997, Hong Kong.

- H. T. Jensen, I. Galton, "A performance analysis of the partial randomization dynamic element matching DAC architecture," *IEEE Proceedings of the International Symposium on Circuits and Systems* 1997, ISCAS 1997, Hong Kong.

- H. T. Jensen, I. Galton, "A Hardware-efficient DAC for Direct Digital Synthesis," *IEEE Proceedings of the International Symposium on Circuits and Systems 1996*, ISCAS 1996, Atlanta, GA.

- I. Galton, D. A. Towne, J. Rosenberg, H. T. Jensen, "Clock Distribution Using Coupled Oscillators," *IEEE Proceedings of the International Symposium on Circuits and Systems* 1996, ISCAS 1996, Atlanta, GA.

- H. T. Jensen, I. Galton, "A robust parallel delta-sigma A/D converter architecture," *IEEE Proceedings of the International Symposium on Circuits and Systems* 1995, ISCAS 1995, Seattle, WA.

#### ABSTRACT OF THE DISSERTATION

# Analyses of Dynamic Element Matching Techniques for Data Conversion

by

Henrik Tholstrup Jensen

Doctor of Philosophy in Electrical and Computer Engineering

(Communication Theory & Systems)

University of California, San Diego, 1997

Professor Ian Galton, Chair

The DEALLY, a digital-to-analog converter (DAC) circuit converts a sequence of numbers represented in a digital format into exactly the same sequence of numbers represented in an analog format. As an example, the digital sequence

$$d[n] = \{ \cdots, 2, 1, 3, 2, 1, \cdots \}$$

could ideally be converted into analog form as the sequence of voltages

$$a_i[n] = {\cdots, 2V, 1V, 3V, 2V, 1V, \cdots}.$$

However, non-idealities associated with the DAC fabrication process result in circuit imperfections which cause non-ideal behavior of the DAC. As an example, a fabri-

cated DAC might convert the digital sequence d into analog form as the sequence of voltages

$$a_{ni}[n] = \{ \dots, 2.1V, 0.9V, 3.0V, 2.1V, 0.9V, \dots \}.$$

Thus, a practical DAC introduces analog error, defined as

$$a_i[n] - a_{ni}[n] = \{ \dots, -0.1 \text{V}, 0.1 \text{V}, 0.0 \text{V}, -0.1 \text{V}, 0.1 \text{V}, \dots \}.$$

In general, the analog error is a non-linear function of the digital input, so the DAC is a non-linear device, and the analog error tends to be strongly correlated with the digital input. This unfortunate property causes the DAC to be the performance limiting component in many electronic systems. For example, such is the case with direct digital synthesizers, which—using mostly digital circuitry—generate high spectral-purity sinusoidal analog signals in wireless communications systems. Another application wherein the analog error has detrimental effects is in the oversampling  $\Delta\Sigma$  data converter.

In this dissertation, recently developed digital signal processing algorithms—also known as dynamic element matching (DEM) techniques—designed to eliminate or minimize the detrimental effects of the analog error are presented and their performance analyzed. Rather than simply trying to minimize the analog error by improvements in the DAC fabrication process, the non-ideal behavior is accepted as inevitable, but its detrimental effects are mitigated using a DEM technique. Various DEM techniques are presented, each of which is optimal for a particular DAC application. In all cases, a drastic decrease of the detrimental effects of the analog error has been verified with theoretical analyses and demonstrated with simulation data.

# A Low-Complexity Dynamic Element Matching DAC for Direct Digital Synthesis<sup>†</sup>

Henrik T. Jensen, Student Member, IEEE, and Ian Galton, Member, IEEE ‡

Abstract—This paper presents and analyzes a new dynamic element matching technique for low harmonic distortion digital-to-analog conversion. The benefit of the technique over the prior art is significantly reduced hardware complexity with no reduction in performance. It is particularly appropriate for applications such as direct digital synthesis in wireless communications systems, wherein low hardware complexity is essential in addition to low harmonic distortion.

#### I. INTRODUCTION

A S a largely digital technique for generating high spectral-purity sinusoidal analog signals, direct digital synthesis (DDS) is increasingly used in wireless communications systems. The main limitation in most DDS systems is imposed by the front-end digital-to-analog converter (DAC) required to convert the digitally synthesized sinusoidal sequence into an analog waveform. In particular, non-ideal circuit behavior causes the DAC to introduce DAC noise. At least a component of the DAC noise is a non-linear function of the input sequence, so harmonic distortion

<sup>†</sup> Accepted for publication: IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: ANALOG AND DIGITAL SIGNAL PROCESSING

<sup>&</sup>lt;sup>‡</sup> The authors are with the Department of Electrical and Computer Engineering, UNIVERSITY OF CALIFORNIA. SAN DIEGO, La Jolla, CA 92093-0407, USA; email: htjensen@ece.ucsd.edu and galton@ece.ucsd.edu

is introduced that places an upper bound on the achievable spurious-free dynamic range (SFDR) of the overall system. As shown in [1] DDS applications typically require only moderate resolution (e.g., 5-12 bits) provided the harmonic distortion introduced by the DAC is low. For example, an extremely low-complexity digital portion of an 8-bit DDS system has been demonstrated that is capable of achieving a minimum SFDR of 90 dB provided the minimum SFDR of the DAC is 90 dB or greater.

Thus, a remaining problem is to develop moderate-resolution DACs that achieve such low levels of harmonic distortion. In the past, dynamic element matching (DEM) techniques have been successfully applied to decorrelate the DAC noise from the input signal in various DAC topologies. A particularly promising topology involves the use of a bank of 1-bit DACs, the outputs of which are summed together to yield a single multi-bit DAC [2], [3], [4]. For most digital input values, there are many possible input codes to the bank of 1-bit DACs that nominally yield the desired analog output value. Thus, the DAC noise arising from errors introduced by the 1-bit DACs can be "scrambled" by randomly selecting one of the appropriate codes for each digital input value. Although DACs based on this approach have been shown experimentally [2], [3] and through quantitative analysis [4] to achieve excellent SFDRs, the presented DACs suffer from excessive digital hardware complexity. For example, an 8-bit DAC based on the approach used in [2] requires 1024 binary switches and 1024 independent random control bits.

This paper presents a new DEM technique suitable for DACs applicable to DDS. The DEM technique scrambles the DAC noise such that conversion performance similar to that of the prior art is achieved, but with much lower hardware complexity. The proposed DEM technique allows for a varying degree of scrambling, providing a trade-off between harmonic distortion suppression and hardware

complexity. Two versions of the architecture are considered separately: a version with the full degree of scrambling, referred to as full randomization DEM, and a version with a reduced degree of scrambling, referred to as partial randomization DEM. With full randomization DEM, the DAC noise is white and the SFDR is optimal (infinite, in principle). Theoretical results quantifying the performance of full randomization DEM are presented and closely supported by simulation results. Simulations indicate that very good SFDR performance is achieved with partial randomization DEM, and while both DEM versions have much lower hardware complexity than the prior art, the greatest hardware-efficiency is offered by partial randomization DEM. To illustrate these results, example 8-bit DACs with 0.5% static analog mismatch errors are considered in detail; 502 binary switches and 8 independent random bits are required to implement full randomization DEM, whereas merely 46 binary switches and 3 independent random bits are required with partial randomization DEM to provide more than 97 dB of SFDR.

The remainder of the paper is divided into sections as follows. Section II reviews the architectures of the low-harmonic distortion DACs presented in [2], [3], and [4] and presents the two versions of the proposed architecture. Section III presents performance details for full randomization DEM. Section IV provides an IC fabrication yield estimate for full randomization DEM based on the results of the theoretical analysis. In Section V it is demonstrated by means of simulation results how partial randomization DEM can significantly suppress harmonic distortion while offering additional hardware reductions. A quantitative discussion of the hardware requirements of full randomization DEM and partial randomization DEM is given in Section VI. The theoretical results stated in Section III are derived in detail in the appendices.

Figure 1.1: The high-level topology of the low-harmonic distortion DACs presented in [2] and [4].

#### II. LOW-HARMONIC DISTORTION DAC APPROACHES

#### A. Background and Prior Art

The high-level topology shared by the DACs presented in [2] and [4] is shown in Figure 1.1. The digital input, x[n], is a sequence of unsigned b-bit binary numbers less than  $2^b$ , i.e,

$$x[n] \in \{0, 1, \dots, x_{max}\}, \quad x_{max} = 2^b - 1.$$

The DAC consists of a digital encoder,  $2^b$  one-bit DACs referred to as unit DAC-elements, and an analog output summing node. At the high level of Figure 1.1, the digital encoder maps each input sample to  $2^b$  output bits,  $x_1[n] \dots x_{2^b}[n]$ , such that

$$\sum_{i=1}^{2^b} x_i[n] = x[n]. \tag{1}$$

The unit DAC-elements operate according to

$$y_r[n] = \begin{cases} 1 + e_{h_r}, & \text{if } x_r[n] = 1; \\ e_{l_r}, & \text{if } x_r[n] = 0; \end{cases}$$

(2)

where  $y_r[n]$  denotes the analog output of the  $r^{th}$  unit DAC-element, and  $e_{h_r}$  and  $e_{l_r}$  are errors in the analog output levels arising from inevitable non-idealities in

the IC fabrication process. Throughout the paper, these errors are assumed to be time-invariant, but otherwise arbitrary [2] and are referred to as static DAC-element errors. The  $r^{\text{th}}$  unit DAC-element is said to be selected when  $x_r[n] = 1$ . The DAC output y[n] is formed by the analog output summing node such that

$$y[n] = \sum_{i=1}^{2^b} y_i[n]. \tag{3}$$

It follows from (1), (2), and (3) that y[n] = x[n] in the absence of static DAC-element errors. However, as shown in [5], with non-zero static DAC-element errors, the DAC output has the form

$$y[n] = \alpha x[n] + \beta + e[n], \tag{4}$$

where  $\alpha$  is a constant gain,  $\beta$  is a DC offset, and e[n] is a conversion error term referred to as DAC noise. The purpose of the digital encoder is to scramble the DAC noise by randomly selecting the unit DAC-elements such that e[n] is white and uncorrelated with x[n]. To accomplish this objective, the digital encoders of the prior art employ a thermometer-encoder and a scrambler. During each clock period, the thermometer encoder deterministically sets x[n] of its  $2^b$  output bits to "1" and the remaining  $2^b - x[n]$  of its output bits to "0". The scrambler randomly permutes the resulting  $2^b$  bits, thereby selecting x[n] of the unit DAC-elements at random. As explained in [2], the effect is to randomly modulate the DAC noise without modulating the signal component of the DAC output. The random modulation effectively converts the harmonic distortion, i.e., spurious tones, into white noise.

The scrambler implements the random permutation using a network of binary switches, each controlled by a random control bit. The binary switch is a simple 2-input × 2-output device that, depending upon the value of the random control bit, either passes the inputs directly through to the outputs or connects the inputs to the outputs in reverse order. The random control bit of each binary switch is

Figure 1.2: A 3-bit version of the proposed DAC architecture.

ideally a white random bit-sequence, statistically independent of the random control bits applied to the other binary switches. Thus, implementing the digital encoders presented in [2] and [4] requires as many random control bits as binary switches. The digital encoder in [4] is capable of randomly connecting its  $2^b$ -bit inputs to its  $2^b$ -bit outputs in any of the  $2^b$ ! possible combinations. The digital encoder in [2] implements only a subset of all combinations, being capable of randomly connecting its inputs to its outputs in  $2^{b2^{b-1}}$  possible combinations. As will be seen, the digital encoder proposed in this paper implements significantly fewer random input-output mappings than the prior art, yet provides white DAC noise, nonetheless.

#### B. Proposed DAC topology

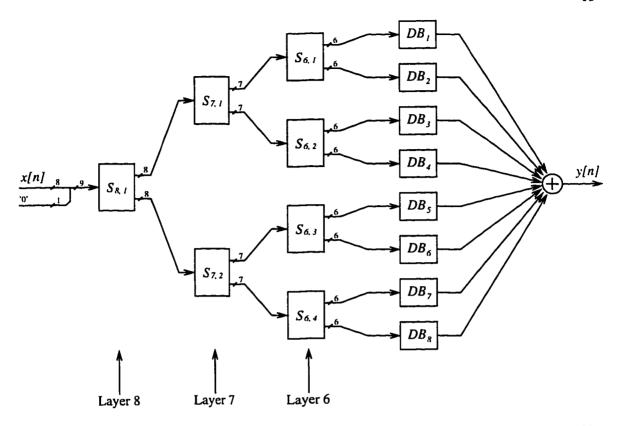

The proposed dynamic element matching DAC architecture is shown in Figure 1.2. To simplify the figure, a 3-bit example is shown. The DAC is of the general

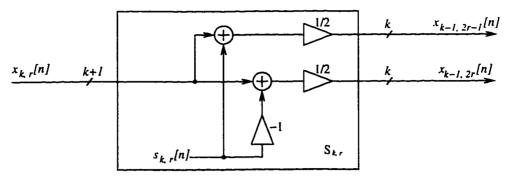

Figure 1.3: Details of (a) the switching block  $S_{k,r}$ , and (b) the binary switch.

topology introduced in [5]. The tree-structured digital encoder consists of three layers of *switching blocks*, each labeled  $S_{k,r}$ , where k denotes the layer number and r denotes the position of the switching block in the layer.

Figure 1.3a shows the functional details of the switching block  $S_{k,r}$ . The switching block has one k+1-bit input, two k-bit outputs, and a random control bit input,  $c_k[n]$ . The random control bit is common to all the switching blocks within the k<sup>th</sup> layer (for clarity, the random control bits are not shown in Figure 1.2). The  $S_{k,r}$  switching block operates such that when  $c_k[n]$  is high, the most significant bit (MSB),  $b_k$ , of the input is mapped to all k bits of the top output, and the remaining k bits of the input are mapped directly to the k bits of the bottom output. When  $c_k[n]$  is low, the situation is as above except that the mappings are interchanged. Thus, it follows that  $S_{k,r}$  can be implemented using k binary switches, all controlled by  $c_k[n]$ . Figure 1.3b shows the binary switch controlled by  $c_k[n]$ . The process of randomly mapping the input to the outputs is referred to as random switching. At the outermost layer, i.e., k = b, the DAC input x[n] is assigned to the  $S_{b,1}$  input bits  $b_1$  through  $b_b$ , and a zero is assigned to the input bit  $b_0$ , as indicated in Figure 1.2. It is shown in appendix 1.A that the digital encoder obtained by interconnecting

the switching blocks of Figure 1.3a as shown in Figure 1.2 indeed satisfies (1).

Motivated by the results of the simulated performance presented in sections III and V, two versions of the proposed architecture are now defined. The term full randomization DEM refers to a DAC with random switching in all layers, i.e., layers 1 through b. The term partial randomization DEM refers to a DAC with random switching in a limited number of layers, i.e., in layers R through b, where  $2 \le R \le b-1$ . As an example of partial randomization DEM, consider the 8-bit DAC of Figure 1.4, where random switching is performed in layers 6 through 8. Layers 1 through 5 have no effect on the scrambling of the DAC noise, so it follows that these layers can be eliminated and substituted by eight nominally identical DAC banks, each with a 6-bit input. The details of the DAC bank are shown in Figure 1.5. The LSB of the input controls a unit DAC-element, whereas the remaining 5 bits control a 5-bit conventional DAC.

#### III. PERFORMANCE DETAILS FOR FULL RANDOMIZATION DEM

#### A. Simulation Results

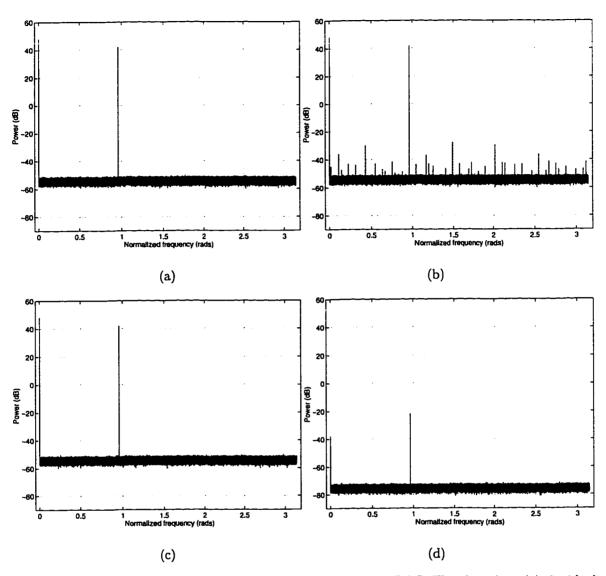

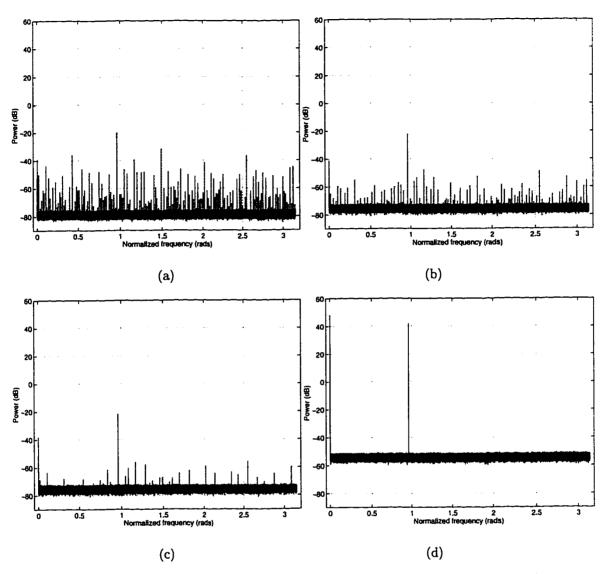

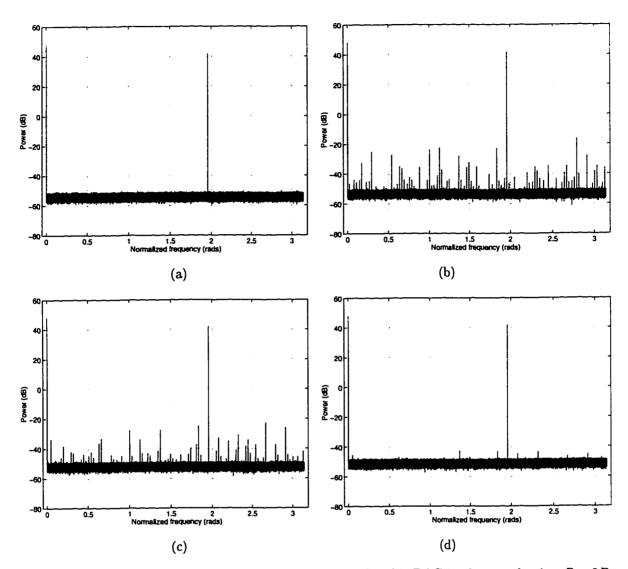

The simulated performance of an example 8-bit DAC with the proposed architecture is presented in Figure 1.6. Each graph in the figure shows the simulated power spectral density (PSD) relative to  $x_{max}^2$  of a particular signal of the DAC driven by a dithered and DC offset sinusoid. Specifically, x[n] was formed by adding dither to the sequence  $A\sin(\omega_0 n) + DC_x$ , where A = 126,  $\omega_0 = \frac{625}{2048}\pi$ , and  $DC_x = 127.5$ , and then quantizing the result to 8 bits. The dither added to the sinusoidal input was a white sequence with a triangular probability density function supported on (-1,1), so the quantization error was white noise [6].

Figure 1.6a corresponds to y[n] of an ideal DAC (i.e., a DAC with no static DAC-element errors, so y[n] = x[n]), Figure 1.6b corresponds to y[n] with no random

Figure 1.4: An 8-bit DAC with partial randomization DEM.

Figure 1.5: Details of the DAC bank.

switching (the digital encoder thus being equivalent to a thermometer encoder), Figure 1.6c corresponds to y[n] with full randomization DEM, and Figure 1.6d corresponds to the signal y[n] - x[n] with full randomization DEM. The static mismatch errors were chosen randomly from a normal distribution with a standard deviation of 0.5%. This represents a conservative estimate relative to the static DAC-element errors expected in practice, but serves to demonstrate the robustness

Figure 1.6: Simulated PSDs relative to  $x_{max}^2$  of an example 8-bit DAC. The plots show (a) the ideal DAC output y[n], (b) the DAC output y[n] with no random switching, (c) the output y[n] with full randomization DEM, and (d) the signal y[n] - x[n] with full randomization DEM.

of the proposed DEM technique [2], [7].

As is evident from the numerous spurs distributed across the spectrum in Figure 1.6b, rather severe harmonic distortion results from the static DAC-element errors in the absence of random switching. The maximum-amplitude spur occurs at a frequency of approximately  $1.5\pi$  radians, and has power -69.86 dB below the power of the desired sinusoidal signal of frequency  $\omega_0$ . Numerous additional simula-

tions performed by the authors show that the DAC exhibits similar behavior when driven by inputs of different frequencies. It follows that merely 69.86 dB of SFDR is provided. The data in Figure 1.6c indicates that harmonic distortion is not visible with full randomization DEM. As demonstrated by the simulation results and confirmed in the following section, the DAC easily provides 90 dB of SFDR and is thus applicable to the DDS system mentioned in the Introduction.

Additional details of the simulation results are as follows. The PSDs were each estimated by averaging 16 length- $2^{18}$  periodograms [8]. The frequency scales were normalized such that  $\pi$  corresponds to half the clock rate of the DAC.

#### B. Performance Equations

A detailed theoretical performance analysis of full randomization DEM is given in appendix 1.B and appendix 1.C. However, for the purpose of comparing simulation results and theory, the main results of the analysis will be stated in the following.

For a b-bit version of the proposed DAC architecture, let x[n] be a deterministic input sequence and let  $x^{(i)}[n]$  denote the i<sup>th</sup> bit of x[n],  $1 \le i \le b$ . In accordance with the usual definitions, let the *time-average means* of x[n],  $x^{(i)}[n]$ , and  $x^{(i)}[n]x^{(j)}[n]$  be defined as

$$\overline{M}_x = \lim_{P \to \infty} \frac{1}{P} \sum_{n=1}^{P} x[n],$$

$$\overline{M}_{x^{(i)}} = \lim_{P \to \infty} \frac{1}{P} \sum_{n=1}^{P} x^{(i)}[n],$$

and

$$\overline{M}_{x^{(i,j)}} = \lim_{P \to \infty} \frac{1}{P} \sum_{n=1}^{P} x^{(i)}[n] x^{(j)}[n],$$

respectively, and let the time-average autocorrelation of x[n] be defined as

$$\overline{R}_{xx}[k] = \lim_{P \to \infty} \frac{1}{P} \sum_{n=1}^{P} x[n]x[n+k].$$

The time-average autocorrelation of y[n] is defined analogously with x replaced by y in the above definition. The two main theoretical results of this paper can now be stated as follows:

**Result 1.** The output of the proposed DAC with full randomization DEM can be written in the form

$$y[n] = \alpha x[n] + \beta + e[n], \tag{5}$$

where e[n] is a zero-mean, white random process of the form

$$e[n] = \sum_{i=1}^{b} w_i[n] x^{(i)}[n], \tag{6}$$

and each  $w_i[n]$  is a zero-mean, white random process.

Appendix 1.A provides exact formulae for the constants  $\alpha$  and  $\beta$  in (5), and expressions for  $w_i[n]$  in (6) are developed in appendix 1.B. For now, it suffices to know that the random processes  $w_i[n]$  depend only upon the static DAC-element errors and are zero-mean, white, and uncorrelated with x[n]. Notice that the above results hold for any underlying statistical distribution or correlation properties of the static DAC-element errors.

**Result 2.** If  $\overline{M}_x$  and  $\overline{R}_{xx}[k]$  exist, then

$$\overline{M}_y = \alpha \overline{M}_x + \beta \tag{7}$$

and

$$\overline{R}_{yy}[k] = \alpha^2 \overline{R}_{xx}[k] + \overline{\eta} + \overline{\sigma}^2 \delta[k], \tag{8}$$

with probability 1, where

$$\overline{\eta} = 2\alpha\beta \overline{M}_x + \beta^2, \tag{9}$$

and

$$\overline{\sigma}^2 = \sum_{i=1}^b \gamma_i \, \overline{M}_{x^{(i)}} + \sum_{j=1}^{b-1} \sum_{i=j+1}^b \gamma_{i,j} \, \overline{M}_{x^{(i,j)}}. \tag{10}$$

Appendix 1.B provides formulae for the constant coefficients  $\gamma_i$  and  $\gamma_{i,j}$  in (10). For now, it suffices to know that these coefficients depend only upon the static DAC-element errors. As before, this result holds for any underlying statistical distribution or correlation properties of the static DAC-element errors.

#### C. Comparison of Simulation Results and Theory

To summarize, (8) states that  $\overline{R}_{yy}[k]$  consists of a scaled version of  $\overline{R}_{xx}[k]$ , a DC offset and white DAC noise. This general conclusion is similar to the corresponding result in [4] and is clearly supported by the simulation results of Figure 1.6.

It follows from (5) that a non-unity value of  $\alpha$  causes a term corresponding to  $(\alpha - 1)x[n]$  to occur in the signal y[n] - x[n]. This scaled version of x[n] occurring in y[n] - x[n] therefore has power

$$\Delta P_x = 10 \log_{10} \left[ (\alpha - 1)^2 \right] dB \tag{11}$$

relative to the power of x[n]. Similarly, it follows from (5) that the DC component occurring in y[n] - x[n] has power

$$\Delta P_{DC} = 10 \log_{10} \left[ \left( \alpha - 1 + \frac{\beta}{\overline{M}_x} \right)^2 \right] dB$$

(12)

relative to  $(\overline{M}_x)^2$ . To compare these predictions with the simulation results, the randomly chosen static DAC-element errors of the example 8-bit DAC were summed according to the formulae for  $\alpha$  and  $\beta$  given in appendix 1.A, and resulted in  $\alpha$  –  $1 = -6.4361 \times 10^{-4}$  and  $\beta = 7.5634 \times 10^{-2}$ , respectively. Evaluating (11) and (12) with these values of  $\alpha$  and  $\beta$  results in  $\Delta P_x = -63.83$  dB and  $\Delta P_{DC} = -85.95$  dB. Measuring the offsets corresponding to  $\Delta P_x$  and  $\Delta P_{DC}$  using the data of Figure 1.6a and Figure 1.6d yields -63.82 dB and -85.96 dB, respectively, in agreement with theory. Furthermore, evaluating (10) for the simulated values of static DAC-element errors yields a power of the DAC noise of  $\overline{\sigma}^2 = -75.45$  dB

relative to  $x_{max}^2$ . Numerically integrating the DAC noise component of the PSD of Figure 1.6d results in -75.44 dB, in agreement with theory. As an additional comment pertaining to the details of Figure 1.6, it is evident from a comparison of Figure 1.6c and Figure 1.6d that  $\bar{\sigma}^2$  is negligible relative to the power of the white quantization error and dither term of x[n].

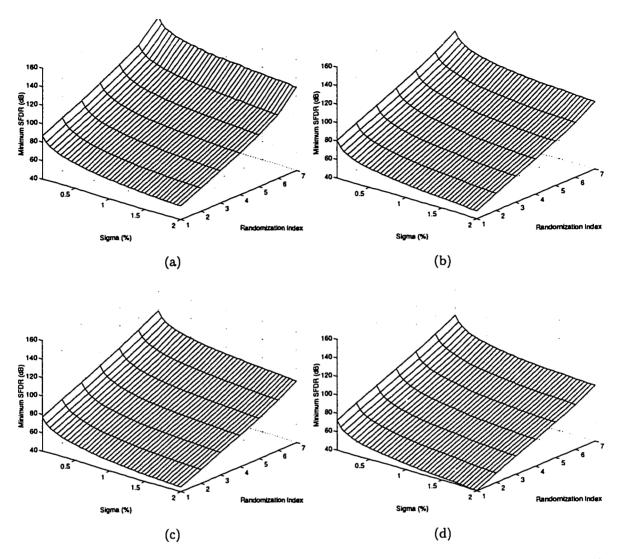

#### D. An Interpretation of the Performance Equations

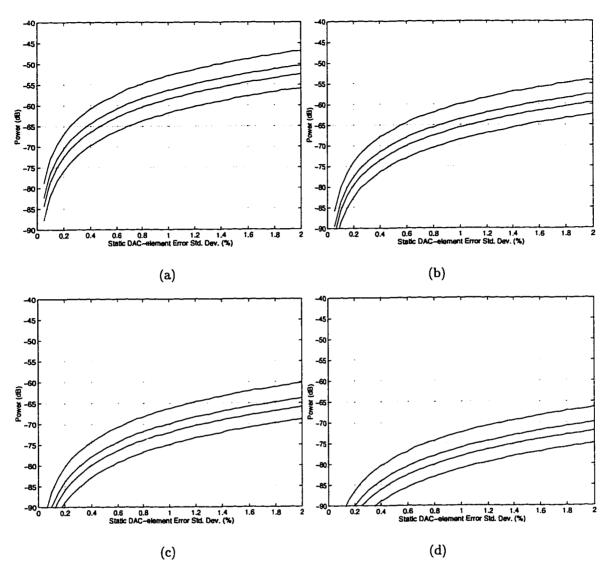

The most significant performance equations in the above are (8) and (10) which state that the DAC noise is white and give a formula for the power of the DAC noise, respectively. As is evident from (10),  $\overline{\sigma}^2$  is a linear combination of the time-average means of the individual bits of x[n] plus a linear combination of the time-average means of the products of pairs of bits of x[n]. If x[n] is the quantized version of a sinusoid  $A\sin(\omega n)$ , it follows that  $\overline{\sigma}^2$  depends on both amplitude A and frequency  $\omega$ . This is different from the architecture presented in [4] for which  $\overline{\sigma}^2$  only depends on signal amplitude. To demonstrate typical behavior of  $\bar{\sigma}^2$ , Figures 1.7a-d show plots of  $\bar{\sigma}^2$  in dB relative to  $x_{max}^2$  for four nominally identical 8-bit versions of the proposed DAC. The DACs differed only in the static DAC-element errors, which were randomly chosen from a normal distribution with a standard deviation of 0.5%. In each case, the DAC was driven by a sinusoidal input and the plot shows  $\bar{\sigma}^2$  computed using (10) as a function of input amplitude and frequency. In general, only minor dependency on frequency is observed, whereas dependency on amplitude is stronger. Notice that there is no clear trend in  $\overline{\sigma}^2$  as a function of amplitude, which is in contrast to the behavior of  $\overline{\sigma}^2$  in [4] wherein  $\overline{\sigma}^2$  decreases with increasing amplitude.

Figures 1.8a-d show plots of  $\overline{\sigma}^2$  in dB relative to  $x_{max}^2$  for the same four example 8-bit DACs as in Figure 1.7 when driven by the sum of two DC offset sinusoids, i.e., x[n] being the quantized version of  $x_1[n]+x_2[n]+x_{max}/2$ , where  $x_1[n]=A_1\sin(\omega_1 n)$

Figure 1.7: Plots of  $\overline{\sigma}^2$  in dB relative to  $x_{max}^2$  for four nominally identical 8-bit versions of the proposed DAC. The DACs in (a) through (d) differed only in the static DAC-element errors, which were randomly chosen from a normal distribution with a standard deviation of 0.5%. In each case, the DAC was driven by a sinusoidal input and the plot shows  $\overline{\sigma}^2$  computed using (10) as a function of input amplitude and frequency.

and  $x_2[n] = A_2 \sin(\omega_2 n)$ . In each plot, the amplitude of each sinusoidal component was fixed at  $A_1 = A_2 = 63$ , and  $\overline{\sigma}^2$  computed using (10) is shown as a function of  $\omega_1$  and  $\omega_2$ . Again,  $\overline{\sigma}^2$  exhibits little dependency on input frequency and attains average values of -74.82 dB, -77.84 dB, -73.02 dB, and -74.33 dB, respectively. Thus, the random variation of the static DAC-element errors of the example DACs causes a spread in the average value of  $\overline{\sigma}^2$  of 4.82 dB.

Figure 1.8: Plots of  $\bar{\sigma}^2$  in dB relative to  $x_{max}^2$  for the same four example 8-bit DACs as in Figure 1.7 when driven by the sum of two sinusoids. In each plot, the amplitude of each sinusoidal component was fixed, and  $\bar{\sigma}^2$  computed using (10) is shown as a function of the frequencies of the sinusoidal components.

#### IV. IC FABRICATION YIELD ESTIMATION

With knowledge of the statistical distribution of the static DAC-element errors, an IC fabrication yield estimate of the proposed DAC architecture with full randomization DEM can be performed using (10). IC fabrication yield estimation data provides a means by which to estimate the percentage of fabricated DACs that will result in a value of  $\overline{\sigma}^2$  less than any value of interest. The IC fabrication

Figure 1.9: IC fabrication yield estimation data for (a) 4-bit, (b) 6-bit, (c) 8-bit, and (d) 10-bit versions of the proposed DAC. The static DAC-element errors were chosen from a normal distribution with a standard deviation ranging from 0.05% to 2%. In each case, from top to bottom, the curves show the largest of the smallest 95%, 65%, 35%, and 5% of  $\overline{\sigma}^2$  values in dB relative to  $x_{max}^2$ , respectively, when driving the DAC by a sinusoidal input.

yield estimation procedure used in the following was first introduced in [4] and is based upon the idea of computing a large number of samples of  $\overline{\sigma}^2$  for a given level of static DAC-element errors, thereby generating data that closely resemble the corresponding statistical distribution of  $\overline{\sigma}^2$ .

For example, Figures 1.9a-d show IC fabrication yield estimation data corre-

sponding to 4-bit, 6-bit, 8-bit, and 10-bit DACs, respectively. In each case, from top to bottom, the curves show the largest of the smallest 95%, 65%, 35%, and 5% of  $\bar{\sigma}^2$  values in dB relative to  $x_{max}^2$ , respectively, when driving the DAC by a maximum-amplitude, DC offset sinusoidal input of frequency  $\omega_0 = \frac{625}{2048}$ . Each figure shows  $\bar{\sigma}^2$  versus increasing standard deviation of the static DAC-element errors, and each yield estimation is based upon 5000 calculated values. The static DAC-element errors were chosen as samples of independent, normally distributed random variables with a standard deviation ranging from 0.05% to 2%. This particular choice of static DAC-element errors was made for demonstration purposes only; any other distribution could have been used without changing the yield estimation procedure.

For example, with a standard deviation of 0.5%, the data of Figure 1.9c predicts that 95% of all 8-bit DACs will satisfy  $\bar{\sigma}^2 \leq -72$  dB relative to  $x_{max}^2$  and that 5% will satisfy  $\bar{\sigma}^2 \leq -81$  dB relative to  $x_{max}^2$ . Thus, 90% of all 8-bit DACs fabricated satisfy

$$-81 \text{ dB} \le \overline{\sigma}^2 \le -72 \text{ dB}$$

relative to  $x_{max}^2$ . This conclusion is supported by the data of the simulated example 8-bit DAC of Figure 1.6, for which  $\overline{\sigma}^2 = -75.44$  dB relative to  $x_{max}^2$ , and by the four example 8-bit DACs of Figure 1.7, for which  $\overline{\sigma}^2$  equals -75.53 dB, -78.35 dB, -73.91 dB, and -75.57 dB, respectively, all relative to  $x_{max}^2$ .

As mentioned previously, when driving the DAC by a sinusoidal input,  $\bar{\sigma}^2$  depends on both amplitude and frequency. With a strong dependency, this property would limit the usefulness of the IC fabrication yield estimation technique in that the resulting data only would be applicable to DACs driven by a particular sinusoid. However, as was demonstrated in Figure 1.7,  $\bar{\sigma}^2$  is largely independent of sinusoidal frequency, and repeating the yield estimate calculations with maximum-amplitude

sinusoidal inputs of several different frequencies gives results very close to the data presented in Figure 1.9. As was also demonstrated with the data in Figure 1.7, no clear trend in  $\bar{\sigma}^2$  as a function of sinusoid amplitude is observed, and repeating the yield estimate calculations with sinusoids of different amplitudes gives results very close to the data in Figure 1.9. Consequently, when computing a large number of values of  $\bar{\sigma}^2$ , the spread of  $\bar{\sigma}^2$  caused by varying amplitude is largely absorbed in the spread of  $\bar{\sigma}^2$  caused by varying random mismatch errors. It follows that Figure 1.9 represents IC fabrication yield estimation data valid for sinusoidal inputs of any amplitude and frequency.

# V. PERFORMANCE DETAILS FOR PARTIAL RANDOMIZATION DEM

In practice, a number of factors other than the static DAC-element errors limit the SFDR achievable by the DAC. Non-ideal circuit behavior such as clock-skew, clock coupling, and finite slew-rates inevitably contributes to harmonic distortion of the DAC output. Thus, the total amount of harmonic distortion of the DAC can be viewed as the effects of two components, namely a component caused by the static DAC-element errors and a component caused by all other non-ideal circuit behavior. To the extent that the latter component is below—or can be attenuated to—the maximum allowable level of harmonic distortion for a given DAC application, a better "engineering solution" to mitigate the effects of the static DAC-element errors might be to merely attenuate the resulting harmonic distortion to the maximum allowable level, thereby possibly reducing the hardware requirement of the DEM technique. The simulation results presented in the following indicate that partial randomization DEM indeed offers such an option.

#### A. Simulation Results

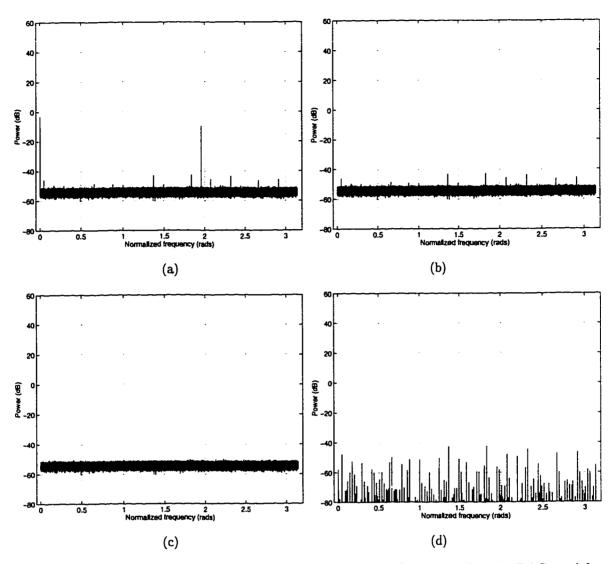

Simulation results for partial randomization DEM is shown in Figure 1.10. In

Figure 1.10: Simulated PSDs relative to  $x_{max}^2$  of an example 8-bit DAC with partial randomization DEM. The plots show (a) y[n] - x[n] with random switching in layer 8, (b) y[n] - x[n] with random switching in layers 7 and 8, (c) y[n] - x[n] with random switching in layers 6 through 8, and (d) y[n] with random switching in layers 6 through 8.

particular, Figures 1.10a-c correspond to the signal y[n] - x[n] with random switching in layer 8, layers 7 and 8, and layers 6 through 8, respectively. Figure 1.10d corresponds to y[n] with random switching in layers 6 through 8. In all cases, the DAC input and static DAC-element errors were identical to those used for the full randomization DEM example of Figure 1.6. The simulation results indicates that

the harmonic distortion is gradually attenuated as the number of layers with random switching is increased. The maximum-amplitude spurs of Figures 1.10a-c have powers -73.55 dB, -89.47 dB, and -97.49 dB, respectively, relative to the power of the desired sinusoidal signal of frequency  $\omega_0$ . Several simulations using other sinusoid frequencies and amplitudes similarly support these findings. Consequently, the SFDRs provided by the DAC are 73.55 dB, 89.47 dB, and 97.49 dB, respectively. The parameters used to compute the PSDs were identical to the parameters used to compute the PSDs of Figure 1.6.

To summarize the simulation results of Figure 1.10, partial randomization DEM increasingly suppresses harmonic distortion as the number of layers with random switching is increased, and may suffice to provide the necessary dynamic range for a given application. For example, three layers of random switching would suffice to provide the desired minimum 90 dB of SFDR for an 8-bit DAC applicable to the DDS system mentioned in the Introduction. As quantified in the next section, the hardware complexity of the digital encoder is greatly reduced with partial randomization DEM.

Additional research is needed to theoretically quantify the performance of partial randomization DEM. Among the goals for such research would be a determination of a guaranteed minimum SFDR given a specific degree of randomization.

### VI. HARDWARE COMPLEXITY OF THE DIGITAL ENCODER

The hardware complexity of the digital encoder is a function of both the required number of binary switches and the required number of random control bits. As will be shown in the following, the proposed architecture has much lower hardware complexity than the prior art.

| DAC Bits                            | 6         | 7         | 8           | 9           | 10          | 11          | 12          |

|-------------------------------------|-----------|-----------|-------------|-------------|-------------|-------------|-------------|

| Digital Encoder<br>Presented in [2] | 192 / 192 | 448 / 448 | 1024 / 1024 | 2304 / 2304 | 5120 / 5120 | 11264/11264 | 24576/24576 |

| Proposed<br>Digital Encoder         | 120 / 6   | 247 / 7   | 502 / 8     | 1013 / 9    | 2036 / 10   | 4083 / 11   | 8178 / 12   |

Figure 1.11: Digital hardware required to implement the digital encoders presented in [2] and of the proposed architecture versus the DAC bit-resolution. The table entries are given as pairs (x/y), where x is the number of binary switches and y is the number of random control bits.

## A. Full Randomization DEM

To determine the number of required binary switches, recall that the switching block  $S_{k,r}$  requires k binary switches. From this, it can be shown that the total number of binary switches required by the digital encoder of a b-bit DAC is  $2^{b+1} - b - 2$ . It can furthermore be shown that the numbers of required binary switches of the digital encoders presented in [2] and [4] are  $b2^{b-1}$  and  $(b-\frac{1}{2})2^b$ , respectively. The number of random control bits required for the proposed digital encoder is simply b, whereas the digital decoders in [2] and [4] require the same number of random control bits as binary switches.

It follows that the number of required random control bits has been reduced exponentially in b compared to the prior art, and that the number of required binary switches has been reduced linearly in b. As an example, an 8-bit DAC with the digital encoder architecture presented in [2] requires approximately twice as many binary switches as the proposed architecture, whereas 128 times as many random control bits are required.

A detailed comparison of the hardware complexity of moderate-resolution DACs is shown in Figure 1.11. The figure shows the hardware complexity of the digital encoder presented in [2] and the proposed architecture for bit-resolutions 6 through 12. The table entries are given as pairs (x/y), where x is the number of binary switches and y is the number of random control bits, respectively.

| Layers with<br>Random Switching | 8     | 7–8    | 6–8    | 5-8    | 4-8     | 3-8     | 2-8     |

|---------------------------------|-------|--------|--------|--------|---------|---------|---------|

| Hardware<br>Complexity          | 8 / 1 | 22 / 2 | 46 / 3 | 86 / 4 | 150 / 5 | 246 / 6 | 374 / 7 |

Figure 1.12: Hardware complexity versus the range of layers with random switching of an example 8-bit digital encoder. The table entries are given as pairs (x/y), where x is the number of binary switches and y is the number of random control bits.

### B. Partial Randomization DEM

As discussed previously, very low hardware complexity is achievable with partial randomization DEM. To obtain a precise count of the hardware requirement, suppose that the digital encoder implements random switching in layers R through b. It can be shown that the number of required binary switches is  $(R+1)2^{b-R+1}-b-2$ . The required number of random control bits is simply b-R+1 (i.e., the number of layers with random switching).

As an example, it follows that the 8-bit DAC with random switching in layers 6 through 8 requires  $7 \times 8 - 8 - 2 = 46$  binary switches and merely 3 random control bits. This should be compared to the requirement of 502 binary switches and 8 random control bits for full randomization DEM and the requirement of 1024 binary switches and 1024 random control bits for the digital encoder in [2]. To further illustrate the reduction of hardware complexity when using partial randomization DEM, the hardware complexity of an 8-bit example DAC versus the range of layers with random switching is tabulated in Figure 1.12.

Finally, it should be mentioned that the reduction in hardware complexity obtained with the proposed digital encoder architecture also yields a major simplification in VLSI layout; generating and routing 1024 random control bits is significantly more difficult than generating and routing 8 or fewer random control bits.

### VII. CONCLUSION

A new hardware-efficient dynamic element matching DAC architecture appro-

priate for DDS has been presented. The proposed architecture is significantly more hardware efficient than the prior art, yet provides similar performance with respect to suppression of harmonic distortion.

For full randomization DEM, quantitative results giving the power of the white conversion noise have been stated and proven, and yield estimates have been presented for selected bit-resolutions and VLSI process statistics. Computer simulation results have been presented that fully support the theoretical results for an example 8-bit DAC applicable to a certain DDS system.

Simulation results show that harmonic distortion is greatly suppressed with partial randomization DEM, which offers a considerable additional reduction in hardware complexity. It has been shown that for an example 8-bit DAC with partial randomization DEM, merely 3 layers of random switching suffice to provide greater than 90 dB of SFDR, as desired for the DDS application in question. Additional research is needed to theoretically quantify the performance of partial randomization DEM. Of particular interest would be the determination of a guaranteed minimum SFDR given a specific degree of randomization.

Non-ideal circuit behavior such as clock-skew, clock-coupling, and finite slew rates inevitably contributes to harmonic distortion of the DAC output. Such non-ideal circuit behavior is typically quite implementation dependent, and research to quantify and mitigate its effects must likely be performed on a case-by-case basis. Nevertheless, the results presented in this paper are still applicable is such situations. In particular, partial randomization DEM promises to offer the option of reducing the hardware complexity of the DEM technique to a minimum while still attenuating harmonic distortion resulting from static DAC-element errors below the level of inevitable harmonic distortion.

Figure 1.13: The signal processing equivalent of the switching block  $S_{k,r}$ .

### APPENDIX 1.A

The purpose of this appendix is to verify that the output y[n] of the proposed DAC architecture with full randomization DEM or partial randomization DEM is of the general form stated in [5], which will be repeated shortly for convenience. Then, in appendix 1.B, the general form of the DAC noise e[n] given here is re-written to the form stated in Result 1 of Section III, and an expression for the variance of e[n] is derived.

Before stating the general form of the DAC output as derived in [5], a few definitions are first presented. The DACs considered in [5] have switching blocks that perform the signal processing operations depicted in Figure 1.13, and as is shown below, the switching blocks of the DAC architecture proposed in this paper can also be viewed as shown in Figure 1.13. The k + 1-bit input of  $S_{k,r}$  is denoted  $x_{k,r}[n]$ , and the two k-bit outputs are denoted  $x_{k-1,2r-1}[n]$  and  $x_{k-1,2r}[n]$ , respectively. The i<sup>th</sup> bit of  $x_{k,r}[n]$  is denoted  $x_{k,r}^{(i)}[n]$ . The sequence  $s_{k,r}[n]$  is generated within the switching block, and, as can be verified from the figure,

$$s_{k,r}[n] = x_{k-1,2r-1}[n] - x_{k-1,2r}[n].$$

(13)

The results in [5] giving the general form of the DAC output can now be stated as follows:

Claim A. The output y[n] of a b-bit version of the proposed DAC architecture

with full randomization DEM or partial randomization DEM is of the form

$$y[n] = \alpha x[n] + \beta + e[n], \tag{14}$$

where

$$\alpha = 1 + \frac{1}{2^b} \sum_{i=1}^{2^b} (e_{h_i} - e_{l_i}), \tag{15}$$

$$\beta = \sum_{i=1}^{2^b} e_{l_i},\tag{16}$$

and

$$e[n] = \sum_{k=1}^{b} \sum_{r=1}^{2^{b-k}} \Delta_{k,r} s_{k,r}[n].$$

(17)

In (17),

$$\Delta_{k,r} = \frac{1}{2^k} \sum_{i=(r-1)2^k+1}^{(r-1)2^k+2^{k-1}} \left[ (e_{h_i} - e_{l_i}) - (e_{h_{i+2^{k-1}}} - e_{l_{i+2^{k-1}}}) \right]$$

(18)

and  $s_{k,r}[n]$  is defined by (13). These results do not depend upon any particular form or statistical properties of the static DAC-element errors.

**Proof.** As shown in [5], to prove the above claim for the DAC with full randomization DEM, it suffices to verify

$$x_{b,1}[n] = x[n],$$

(19)

$$s_{k,r}[n] = \begin{cases} \text{even if } x_{k,r}[n] \text{ is even;} \\ \text{odd if } x_{k,r}[n] \text{ is odd;} \end{cases}$$

(20)

and

$$|s_{k,r}[n]| \le \min\{x_{k,r}[n], 2^k - x_{k,r}[n]\}. \tag{21}$$

To accomplish this, a definition of the numerical value of  $x_{k,r}[n]$  is needed.

**Definition.** The numerical value of the input and outputs of the switching block proposed in this paper must be interpreted according to

$$x_{k,r}[n] = \sum_{i=1}^{k} 2^{i-1} x_{k,r}^{(i)}[n] + x_{k,r}^{(0)}[n].$$

(22)

Thus,  $x_{k,r}[n]$  is the sum of a conventional k-bit unsigned binary number and an "extra LSB",  $x_{k,r}^{(0)}[n]$ .

First, to verify (19), recall that the input to the switching block  $S_{b,1}$  was defined in Section II according to

$$x_{b,1}^{(0)}[n] = 0$$

and  $x_{b,1}^{(i)}[n] = x^{(i)}[n], 1 \le i \le b.$

Inserting this in (22) yields (19).

Next, it will be shown that the switching blocks presented in this paper perform signal processing according to Figure 1.13 such that

$$s_{k,r}[n] = \begin{cases} d_{k,r}[n], & \text{if } c_k[n] = 0; \\ -d_{k,r}[n], & \text{if } c_k[n] = 1; \end{cases}$$

(23)

where

$$d_{k,r}[n] = x_{k,r}[n] - 2^k x_{k,r}^{(k)}[n], \tag{24}$$

and  $c_k[n]$  is the random control bit of the  $k^{th}$  layer. Then, (23) and (24) will be used to verify (20) and (21).

Suppose  $c_k[n] = 0$ . It follows from Figure 1.3, (13), and (22) that

$$s_{k,r}[n] = \sum_{i=1}^{k-1} 2^{i-1} x_{k,r}^{(i)}[n] + x_{k,r}^{(0)}[n] - \left(\sum_{i=1}^{k-1} 2^{i-1} + 1\right) x_{k,r}^{(k)}[n].$$

(25)

Collecting and rearranging terms using (22) yields  $s_{k,r}[n] = d_{k,r}[n]$ . Similarly, it follows that  $s_{k,r}[n] = -d_{k,r}[n]$  when  $c_k[n] = 1$ . This verifies (23) and (24).

To verify (20), notice that the term  $2^k x_{k,r}^{(k)}[n]$  in (24) is even because k is a positive integer. Thus, if  $x_{k,r}[n]$  is even,  $d_{k,r}[n]$  is even, and if  $x_{k,r}[n]$  is odd,  $d_{k,r}[n]$  is odd.

To verify (21), notice that if  $x_{k,r}^{(k)}[n] = 1$ , (22) implies  $2^{k-1} \le x_{k,r}[n] \le 2^k$ . Thus, from (23) and (24),

$$|s_{k,r}[n]| = 2^k - x_{k,r}[n] \le x_{k,r}[n].$$

Similarly, if  $x_{k,r}^{(k)}[n] = 0$ , (22) implies  $0 \le x_{k,r}[n] \le 2^{k-1}$ , and thus

$$|s_{k,r}[n]| = x_{k,r}[n] \le 2^k - x_{k,r}[n],$$

which verifies Claim A for full randomization DEM.

The digital encoder with partial randomization DEM employing random switching in layers R through b is equivalent to the digital encoder of full randomization DEM for which  $c_k[n] = 1, k = 1, 2, ..., R - 1$ . Thus, it follows that Claim A also holds for partial randomization DEM.

### APPENDIX 1.B

The purpose of this appendix is to verify that the DAC noise e[n] has the form stated in Result 1 of Section III, and to provide an expression for the variance of e[n].

Claim B1. For a b-bit version of the DAC architecture with full randomization DEM, the DAC noise is a zero-mean, white random process of the form

$$e[n] = \sum_{i=1}^{b} w_i[n] x^{(i)}[n], \tag{26}$$

where each  $w_i[n]$  is a zero-mean, white random process of the form

$$w_i[n] = w_{i,h_i[n]}. (27)$$

In (27),

$$w_{i,j} = \sum_{m=(j-1)2^{i-1}+1}^{j2^{i-1}} (e_{h_m} - e_{l_m}) - 2^{i-1}(\alpha - 1)$$

(28)

and

$$h_i[n] = \sum_{j=1}^{b-i} 2^j c_{i+j}[n] + (1 - c_i[n]) + 1.$$

(29)

The above results do not depend upon any particular form or statistical properties of the static DAC-element errors.

**Proof.** By virtue of Claims A and B1, it is sufficient to show that (17) is equivalent to (26), which will be accomplished by induction. First, notice that substituting (22) into (23) and (24) with k = b and using  $x_{b,1}[n] = 0$  gives

$$s_{b,1}[n] = (-1)^{(1-c_b[n])} (2^{b-1}x^{(b)}[n] - \sum_{i=1}^{b-1} 2^{i-1}x^{(i)}[n]),$$

which, combined with (18), yields

$$\Delta_{b,1} s_{b,1}[n] = \left[ \frac{1}{2^{b-1}} \sum_{m=(1-c_b[n])2^{b-1}+1}^{(1-c_b[n])2^{b-1}+2^{b-1}} (e_{h_m} - e_{l_m} - \alpha + 1) \right] \left[ 2^{b-1} x^{(b)}[n] - \sum_{i=1}^{b-1} 2^{i-1} x^{(i)}[n] \right]. \tag{30}$$

To establish the induction basis, let b = 1. Then, from (17),

$$e[n] = \Delta_{1,1} s_{1,1}[n], \tag{31}$$

and inserting (30) yields

$$e[n] = \left[ \sum_{m=(1-c_1[n])+1}^{(1-c_1[n])+1} (e_{h_m} - e_{l_m} - \alpha + 1) \right] x^{(1)}[n].$$

This can be written as

$$e[n] = w_1[n]x^{(1)}[n] (32)$$

where

$$w_1[n] = w_{1,h_1[n]}$$

and  $h_1[n] = (1 - c_1[n]) + 1$ ,

so e[n] has the form of (26) for b = 1. Since  $c_1[n]$  is a white random process with possible values 0 and 1, it follows that  $h_1[n]$  is a white random process with possible values 1 and 2. But  $h_1[n]$  determines the value of  $w_1[n]$  to be either  $w_{1,1}$  or  $w_{1,2}$ , and thus  $w_1[n]$  is a white random process. It follows from (32) that e[n] is a white

random process. Furthermore, (23) and (31) show that e[n] is zero-mean, and it follows from (32) that  $w_1[n]$  is zero-mean.

Next, suppose the claim holds for  $1 \le b \le b'$ . It will be shown that the claim holds for b' + 1. Notice that (17) may be written as

$$e[n] = \Delta_{b'+1,1} s_{b'+1,1}[n] + e_1[n] + e_2[n], \tag{33}$$

where

$$e_1[n] = \sum_{k=1}^{b'} \sum_{r=1}^{2^{b'-k}} \Delta_{k,r} s_{k,r}[n], \tag{34}$$

and

$$e_2[n] = \sum_{k=1}^{b'} \sum_{r=1}^{2^{b'-k}} \Delta_{k,r+2^{b'-k}} s_{k,r+2^{b'-k}}[n].$$

(35)

It will next be argued that  $e_1[n] = 0$  if  $c_{b'+1}[n] = 1$ , and that  $e_2[n] = 0$  if  $c_{b'+1}[n] = 0$ . Suppose  $c_{b'+1}[n] = 1$ . Since  $x^{(b'+1)}[n]$  is either 0 or 1, it follows from Figure 1.3 and (22) that  $x_{b',1}[n]$  is either 0 or  $2^{b'}$ . Consequently, all the  $x_{k,r}[n]$ ,  $1 \le k \le b'$ ,  $1 \le r \le 2^{b'-k}$ , are either 0 or  $2^k$ . Thus, by (24) and (34),  $e_1[n] = 0$ . Similar reasoning verifies that  $e_2[n] = 0$  if  $c_{b'+1}[n] = 0$ .

Using (30) and invoking the induction hypothesis, (33) may be written as

$$e[n] =$$

$$\left[\sum_{m=(1-c_{b'+1}[n])2^{b'}+1}^{(1-c_{b'+1}[n])2^{b'}+2^{b'}} (e_{h_m}-e_{l_m}-\alpha+1)\right] \left[x^{(b'+1)}[n]-\sum_{i=1}^{b'} \frac{2^{i-1}}{2^{b'}}x^{(i)}[n]\right] + \sum_{i=1}^{b'} w_i[n]x^{(i)}[n].$$

(36)

From (33), it follows that

$$\sum_{i=1}^{b'} w_i[n] x^{(i)}[n] = e_1[n] + e_2[n] = \begin{cases} e_1[n], & \text{if } c_{b'+1}[n] = 0; \\ e_2[n], & \text{if } c_{b'+1}[n] = 1, \end{cases}$$

where  $w_i[n]$  is calculated from (27) with b = b'. The desired result can now be shown by comparing the coefficients of  $x^{(i)}[n]$ ,  $1 \le i \le b' + 1$ , in (36) with the coefficients

determined from (26) with b = b' + 1. The coefficient of  $x^{(b'+1)}[n]$  in (36) is

$$\sum_{m=(1-c_{b'+1}[n])2^{b'}+1}^{(1-c_{b'+1}[n])2^{b'}+2^{b'}} (e_{h_m}-e_{l_m}-\alpha+1), \tag{37}$$

which equals  $w_{b'+1}[n]$ , as asserted. Next, suppose  $c_{b'+1}[n] = 0$ . The coefficient of  $x^{(i)}[n]$ ,  $1 \le i \le b'$ , in (36) is then

$$w_i[n] - \frac{2^{i-1}}{2^{b'}} \sum_{m=2^{b'}+1}^{2^{b'}+1} (e_{h_m} - e_{l_m} - \alpha + 1).$$

Inserting the definition of  $w_i[n]$  with b = b' and rearranging terms yields

$$\sum_{m=(h_i[n]-1)2^{i-1}+1}^{h_i[n]2^{i-1}} (e_{h_m}-e_{l_m}-\alpha+1),$$

which equals  $w_i[n]$  with b = b' + 1. For  $c_{b'+1}[n] = 1$ , it can similarly be shown that the coefficient of  $x^{(i)}[n]$  in (36) is

$$\sum_{m=(2^{b'}+h_i[n]-1)2^{i-1}+1}^{(2^{b'}+h_i[n])2^{i-1}} (e_{h_m}-e_{l_m}-\alpha+1),$$

as asserted. It follows from (37) that  $w_{b'+1}[n]$  is a white random process. Thus, by the induction hypothesis, e[n] is a white random process. Also by the induction hypothesis,  $e_1[n]$  and  $e_2[n]$  in (33) are each zero-mean. It then follows from (23) and (24) that e[n] and  $w_{b'+1}[n]$  are zero-mean random processes.

Claim B2. The variance of e[n] is given by

$$\operatorname{Var}\{e[n]\} = \sum_{i=1}^{b} \gamma_i \, x^{(i)}[n] + \sum_{j=1}^{b-1} \sum_{i=j+1}^{b} \gamma_{i,j} \, x^{(i)}[n] x^{(j)}[n],$$

where

$$\gamma_i = \frac{1}{2^{b-i+1}} \sum_{j=1}^{2^{b-i+1}} (w_{i,j})^2$$

(38)

and

$$\gamma_{i,j} = \frac{1}{2^{b-j-1}} \sum_{k=1}^{2^{b-i}} w_{i,2k-1} w_{i,2k}. \tag{39}$$

**Proof.** Since e[n] is zero-mean,  $Var\{e[n]\} = E\{(e[n])^2\}$ , where  $E\{\cdot\}$  denotes the statistical expectation operator. Using (26) and rearranging terms results in

$$\operatorname{Var}\{e[n]\} = \sum_{i=1}^{b} \operatorname{E}\left\{(w_{i}[n])^{2}\right\} x^{(i)}[n] + 2 \sum_{j=1}^{b-1} \sum_{i=j+1}^{b} \operatorname{E}\left\{w_{i}[n]w_{j}[n]\right\} x^{(i)}[n]x^{(j)}[n], (40)$$

where use was made of the equality  $(x^{(i)}[n])^2 = x^{(i)}[n]$ . To evaluate (40), consider first  $E\{(w_i[n])^2\}$ . By the definition in (29),  $h_i[n]$  can be viewed as the value associated with a (b-i+1)-bit binary number, offset by 1, where the values of the bits are determined by  $c_k[n]$ ,  $k=i,i+1,\ldots,b$ . The two possible values of  $c_k[n]$  are equally probable and  $c_k[n]$  is independent of  $c_j[n]$ ,  $k \neq j$ , so it follows that the  $2^{b-i+1}$  different values of  $h_i[n]$  are equally probable. It then follows from (27) that the  $2^{b-i+1}$  different values of  $w_i[n]$  are equally probable, i.e.,  $w_i[n] = w_{i,j}$  with probability  $\frac{1}{2^{b-i+1}}$ . Thus,

$$E\{(w_i[n])^2\} = \frac{1}{2^{b-i+1}} \sum_{j=1}^{2^{b-i+1}} (w_{i,j})^2, \qquad (41)$$

as asserted.

It will next be shown that

$$\mathbb{E}\left\{w_{i}[n]w_{j}[n]\right\} = \frac{1}{2^{b-j}} \sum_{k=1}^{2^{b-i}} w_{i,2k-1}w_{i,2k}. \tag{42}$$

As derived in the above,  $w_i[n]$  depends on  $c_k[n]$ ,  $k = i, i+1, \ldots, b$ , and  $w_j[n]$  depends on  $c_k[n]$ ,  $k = j, j+1, \ldots, b$ . Thus, it follows that  $w_j[n]$  assumes one of  $2^{i-j}$  equally probable values depending upon the value of  $w_i[n]$ . Specifically, for a given value of  $w_i[n]$ , (27) may be rewritten as

$$w_i[n] = w_{i,2k-1+(1-r)}; \qquad k \in \left\{1, 2, \dots, 2^{b-i}\right\}, \qquad r \in \{0, 1\},$$

(43)

where r is the value of  $c_i[n]$ . As can be verified from (29), the possible values of  $w_j[n]$  can then be specified in terms of k, r, and an integer parameter m according to

$$w_j[n] \in \left\{ w_{j,2^{i-j}(2k-2+r)+m} : m = 1, 2, \dots, 2^{i-j} \right\},$$

(44)

where each value occurs with probability  $\frac{1}{2^{i-j}}$ . Combining (43) and (44) yields

$$\mathbb{E}\left\{w_{i}[n]w_{j}[n]\right\} = \frac{1}{2^{b-i+1}} \frac{1}{2^{i-j}} \sum_{r=0}^{1} \left(\sum_{k=1}^{2^{b-i}} w_{i,2k-1+(1-r)} \left(\sum_{m=1}^{2^{i-j}} w_{j,2^{i-j}(2k-2+r)+m}\right)\right). \tag{45}$$

To proceed with the verification of (42), it will be shown in the following that

$$\sum_{m=1}^{2^{i-j}} w_{j,2^{i-j}(2k-2+r)+m} = w_{i,2k-1+r}. \tag{46}$$

From (28) it follows that (46) can be verified by establishing the appropriate limits for the summation of the terms  $(e_{h_m} - e_{l_m} - \alpha + 1)$ . The lower summation limit on the left-hand side of (46) can easily be found to be

$$[(2k-1+r)-1]2^{i-1}+1. (47)$$

Similarly, the upper summation limit on the left-hand side of (46) can be found to be

$$(2k-1+r)2^{i-1}. (48)$$

Then (46) follows from (28) using (47) and (48). Furthermore,

$$\sum_{r=0}^{1} w_{i,2k-1+(1-r)} w_{i,2k-1+r} = 2w_{i,2k-1} w_{i,2k},$$

and (45) reduces to (42). Claim B2 follows from (40), (41), (42), and the definitions of  $\gamma_i$  and  $\gamma_{i,j}$ .

### APPENDIX 1.C

The purpose of this appendix is to verify the time-average properties of the DAC output with full randomization DEM as stated in Section III by Result 2, given here in its complete form as:

Claim C. If  $\overline{M}_x$  and  $\overline{R}_{xx}[k]$  exist, then

$$\overline{M}_{y} = \alpha \overline{M}_{x} + \beta \tag{49}$$

and

$$\overline{R}_{yy}[k] = \alpha^2 \overline{R}_{xx}[k] + \overline{\eta} + \overline{\sigma}^2 \delta[k], \tag{50}$$

with probability 1, where  $\alpha$  is given by (15),  $\beta$  is given by (16),

$$\overline{\eta} = 2\alpha\beta \overline{M}_x + \beta^2, \tag{51}$$

and

$$\overline{\sigma}^2 = \sum_{i=1}^b \gamma_i \, \overline{M}_{x^{(i)}} + \sum_{j=1}^{b-1} \sum_{i=j+1}^b \gamma_{i,j} \, \overline{M}_{x^{(i,j)}}. \tag{52}$$

In (52),  $\gamma_i$  and  $\gamma_{i,j}$  are given by (38) and (39), respectively.

Proof. From Result 1 it follows that

$$\mathbb{E}\left\{y[n]\right\} = \alpha x[n] + \beta,$$

and consequently,

$$\lim_{P \to \infty} \frac{1}{P} \sum_{n=1}^{P} \mathbb{E} \{y[n]\} = \alpha \overline{M}_x + \beta.$$

To deduce that (49) holds with probability 1, it suffices to show that y[n] obeys the strong law of large numbers. By the Kolmogorov Criterion, it suffices to show that y[n] has finite variance. This follows immediately because x[n] and the static mismatch errors are bounded.

To verify (50), consider first the statistical autocorrelation of y[n] defined as  $R_{yy}[n,k] = \mathbb{E}\{y[n]y[n+k]\}$ . From Result 1 it follows that

$$R_{yy}[n,k] = \mathbb{E}\left\{ (\alpha x[n] + \beta + e[n]) \left( \alpha x[n+k] + \beta + e[n+k] \right) \right\}.$$

Expanding, collecting terms, and making use of the facts that e[n] is a zero-mean, white random process and x[n] is deterministic, results in

$$R_{yy}[n,k] = \alpha^2 x[n]x[n+k] + \alpha\beta(x[n] + x[n+k]) + \beta^2 + \sigma^2[n]\delta[k],$$

where

$$\sigma^{2}[n] = \mathbb{E}\left\{e^{2}[n]\right\} = \text{Var}\left\{e[n]\right\}.$$

Then using Claim B and the definitions of  $\bar{\eta}$  and  $\bar{\sigma}^2$ ,

$$\lim_{P \to \infty} \frac{1}{P} \sum_{n=1}^{P} R_{yy}[n, k] = \alpha^2 \overline{R}_{xx}[k] + \overline{\eta} + \overline{\sigma}^2 \delta[k].$$

An argument identical to that presented for the corresponding result in [4] establishes (50) with probability 1.

### REFERENCES

- M. J. Flanagan, G. A. Zimmerman, "Spur-reduced digital sinusoid synthesis," IEEE Trans. on Communications, vol. 43, no. 7, pp. 2254-2262, July 1995.

- L. R. Carley, "A noise shaping coder topology for 15+ bits converters," IEEE

J. Solid-State Circuits, vol. SC-24, pp. 267-273, April 1989.

- 3. L. R. Carley and J. Kenney, "A 16-bit 4'th order noise-shaping D/A converter," *IEEE Proc. CICC*, pp. 21.7.1-21.7.4, 1988.

- I. Galton, P. Carbone, "A rigorous error analysis of D/A conversion with dynamic element matching," *IEEE Trans. on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 42, no. 12, pp. 763-772, Dec. 1995.

- 5. I. Galton, "Spectral shaping of circuit errors in digital-to-analog converters,"

IEEE Trans. on Circuits and Systems II: Analog and Digital Signal Processing,

to appear.

- R. M. Gray, T. G. Stockham Jr., "Dithered quantizers," IEEE Trans. Inform. Theory, vol. 39, no. 3, pp. 805-812, May 1993.

- 7. R. van de Plassche, Integrated Analog-to-Digital and Digital-to-Analog Converters. Boston, MA: Kluwer Academic Publishers, 1994.

- 8. A. V. Oppenheim, R. W. Schafer, *Discrete-Time Signal Processing*, Englewood Cliffs, NJ: Prentice Hall, 1989.

## CHAPTER ACKNOWLEDGMENT

The text of Chapter 1, in part or in full, consists of the material that will appear as a "Regular Paper" in a future edition of IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing.

The dissertation author was the primary researcher and the co-author listed in this publication directed and supervised the research which forms the basis for this chapter.

# An Analysis of the Partial Randomization Dynamic Element Matching Technique<sup>†</sup>

Henrik T. Jensen, Student Member, IEEE, and Ian Galton, Member, IEEE ‡

Abstract—Partial randomization DEM was recently introduced as a promising DEM technique for low harmonic distortion digital-to-analog conversion. The DEM technique is well-suited for applications such as direct digital synthesis in wireless communication systems for which low hardware complexity is essential in addition to low harmonic distortion. Previously reported simulation results demonstrate that partial randomization DEM greatly attenuates harmonic distortion resulting from static errors in the analog output levels of the DAC, while offering considerable savings in hardware compared to other DEM techniques. This paper presents the first quantitative performance analysis of partial randomization DEM. As a main result, the minimum spurious-free dynamic range provided by the digital-to-analog converter has been quantified as a function of its hardware complexity and the analog output level errors.

#### I. INTRODUCTION

DIRECT digital synthesis (DDS) has emerged as an efficient and flexible method of generating analog signals of high spectral purity [1]. A key component of a DDS system is the digital-to-analog converter (DAC), which must introduce very little harmonic distortion to honor the spectral purity of the synthesized digital

<sup>†</sup> Under review: IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: ANALOG AND DIGITAL SIGNAL PROCESSING

<sup>†</sup> The authors are with the Department of Electrical and Computer Engineering, UNIVERSITY OF CALIFORNIA, SAN DIEGO, La Jolla, CA 92093-0407, USA; email: htjensen@ece.ucsd.edu and galton@ece.ucsd.edu

signal. Unfortunately, non-ideal circuit behavior in practical DACs inevitably gives rise to *DAC noise* that consists largely of harmonic distortion and ultimately limits the achievable DDS performance.