Title:

Delta-Sigma FDC Based Fractional-N PLLs with Multi-Rate Quantizing Dynamic Element Matching

Author:

Venerus, Christian

Series:

UC San Diego Electronic Theses and Dissertations

Degree:

Ph. D.--University of California, San Diego--2013, UC San Diego

Permalink:

https://escholarship.org/uc/item/53q993wg

**Local Identifier:**

b7760067

#### Abstract:

Fractional-N phase-locked loop (PLL) frequency synthesizers are ubiquitous in modern communication systems, where they are used to synthesize a signal of high spectral purity from a reference signal of much lower frequency. In order to meet the requirements of wireless communication standard, strict limitation are placed on the spectral content of the synthesized signal. In recent years, PLL based on time-to-digital converters (TDC-PLLs) have been proposed that aim at moving the complexity of the design from the analog section to the digital section of the synthesizer: the advantages are a reduction in area, cost and power consumption over competing architectures based on delta-sigma modulation and charge pumps ([Delta][Sigma]-PLLs). Although TDC-PLLs with good performance have been demonstrated, TDC quantization noise has so far kept their phase noise and spurious tone performance below that of the best comparable [Delta][Sigma]-PLLs. An alternative approach is to use a delta-sigma frequency-todigital converter ([Delta][Sigma]FDC) in place of a TDC to retain the benefits of TDC-PLLs and [Delta][Sigma]-PLLs. Chapter 1 describes a practical [Delta][Sigma] FDC based PLL in which the quantization noise is equivalent to that of a [Delta][Sigma]-PLL. It presents a linearized model of the PLL, design criteria to avoid spurious tones in the [Delta][Sigma] FDC quantization noise, and a design methodology for choosing the loop parameters in terms of standard PLL target specifications. Chapter 2 presents a multi-rate quantizing dynamic element matching (DEM) encoder for digital to analog converters (DACs) that allows a significant reduction in the encoder power consumption with respect to a conventional encoder for oversampling DEM DACs, at the expense of a minimal signal- to-noise ratio reduction. In Chapter 3, the implementation details of a [Delta][Sigma] FDC based fractional-N phase- locked loop prototype are shown. The PLL was built to showcase the capability of the architecture analyzed in Chapter 1 to comply with the most stringent wireless communication standards. The prototype extends the architecture described in Chapter 1 by including an FDC quantization noise cancelling algorithm, and an hardware efficient implementation of a multi-rate quantizing DEM encoder for digital to frequency conversion

## **Copyright Information:**

All rights reserved unless otherwise indicated. Contact the author or original publisher for any necessary permissions. eScholarship is not the copyright owner for deposited works. Learn more at <a href="http://www.escholarship.org/help\_copyright.html#reuse">http://www.escholarship.org/help\_copyright.html#reuse</a>

## UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Delta-Sigma FDC Based Fractional-N PLLs with Multi-Rate Quantizing Dynamic Element Matching

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

## Christian Venerus

# Committee in charge:

Professor Ian A. Galton, Chair Professor Peter M. Asbeck Professor James F. Buckwalter Professor Bruce K. Driver Professor Thomas T. Liu

Copyright

Christian Venerus, 2013

All rights reserved.

| The dissertation of Christian Venerus is approved, and it is |

|--------------------------------------------------------------|

| acceptable in quality and form for publication on microfilm  |

| and electronically:                                          |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

|                                                              |

| Chair                                                        |

University of California, San Diego

2013

# **DEDICATION**

To my parents, Graziella and Nevio.

## TABLE OF CONTENTS

| Signature P  | Page                                                      | iii  |

|--------------|-----------------------------------------------------------|------|

| Dedication   |                                                           | iv   |

| Table of Co  | ontents                                                   | v    |

| List of Figu | ires                                                      | viii |

| List of Tabl | les                                                       | X    |

| Acknowled    | lgements                                                  | xi   |

| Vita         |                                                           | xiii |

| Abstract of  | the Dissertation                                          | xiv  |

| Chapter 1    | Delta-Sigma FDC Based Fractional-N PLLs                   | 1    |

|              | I. Introduction                                           | 1    |

|              | II. Background Information                                | 4    |

|              | A. Phase Noise in Fractional-N PLLs                       |      |

|              | B. $\Delta\Sigma$ Fractional- <i>N</i> PLLs               | 5    |

|              | III. Overview of The FDC-PLL                              | 7    |

|              | A. System Description                                     | 7    |

|              | B. Digital Loop Filter                                    | 9    |

|              | C. $\Delta\Sigma$ -PLL and FDC-PLL Capacitance Comparison | 10   |

|              | IV. The FDC-PLL Linearized Model                          | 11   |

|              | A. Model Derivation                                       | 11   |

|              | B. Phase Noise PSD Calculation                            | 15   |

|              | C. Loop Filter Design                                     | 18   |

|              | V. Design Example                                         | 22   |

|              | VI. Appendix                                              | 25   |

|           | A. Reference Oscillator Zero-Crossing Time Derivation                                   | 26         |

|-----------|-----------------------------------------------------------------------------------------|------------|

|           | B. Divider Output Zero-Crossing Time Derivation                                         | 26         |

|           | C. Charge Pump Output Derivation                                                        | 28         |

|           | D. Delta-Sigma Modulator Equivalence and Implications                                   | 30         |

|           | Acknowledgements                                                                        | 33         |

|           | Figures                                                                                 | 34         |

|           | Tables                                                                                  | 37         |

|           | References                                                                              | 38         |

| Chapter 2 | Multi-Rate Quantizing Dynamic Element Matching For Oversam Digital-to-Analog Conversion |            |

|           | I. Introduction                                                                         | 41         |

|           | II. Continuous-Time DEM DAC Overview                                                    | 43         |

|           | A. Ideal Continuous-Time DAC Behavior                                                   | 43         |

|           | B. Ideal Continuous-Time DAC Behavior                                                   | 44         |

|           | C. A General Oversampling DEM DAC                                                       | 47         |

|           | III. Multi-Rate Quantizing DEM                                                          | 48         |

|           | A. Problem Statement                                                                    | 48         |

|           | B. A General MRQ-DEM DAC                                                                | 49         |

|           | IV. A Multi-Rate Quantizing DEM DAC Example                                             | 5 <i>6</i> |

|           | A. The Underlying DEM DAC                                                               | 56         |

|           | B. MRQ-DEM DAC Functional Description                                                   | 60         |

|           | C. Signal Path Bypasses the Fast 1-bit DACs                                             | 62         |

|           | D. A Comparable Conventional $\Delta\Sigma$ DAC Example                                 | 63         |

|           | E. Performance Comparison                                                               | 64         |

|           | Acknowledgements                                                                        | 67         |

|           | Figures                                                                                 | 68         |

|           | Dafaranaas                                                                              | 76         |

| Chapter 3 | A 3-4 GHz GSM-Compliant 1.0/1.2V ΔΣ FDCBased Fractional in 65 nm CMOS Technology |     |

|-----------|----------------------------------------------------------------------------------|-----|

|           | I. Architecture Overview                                                         | 79  |

|           | II. ΔΣ FDC Circuit Implementation Details                                        | 82  |

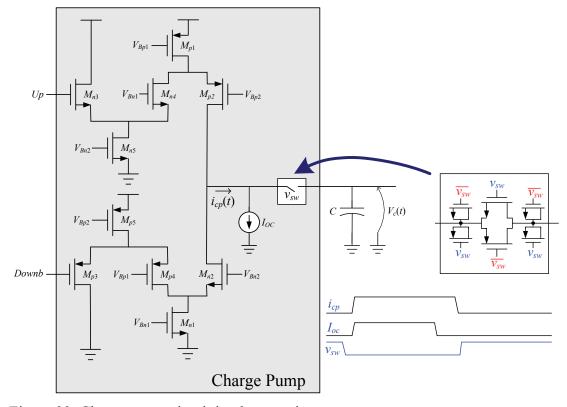

|           | A. Charge Pump                                                                   | 82  |

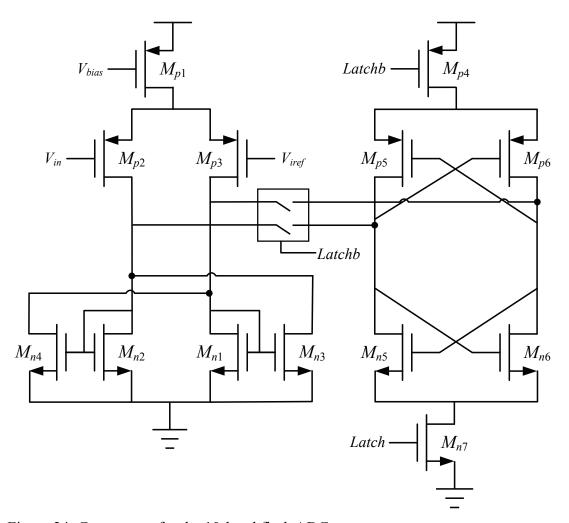

|           | B. Analog to Digital Converter                                                   | 84  |

|           | C. Divider                                                                       | 84  |

|           | III. Quantization Noise Cancellation                                             | 87  |

|           | A. General Quantization Noise Cancelling Architecture                            | 88  |

|           | B. Practical Quantization Noise Cancelling Algorithm Implementation              | 89  |

|           | IV. Digital Loop Controller                                                      | 91  |

|           | V. Multi-rate Quantizing DEM Encoder Hardware Efficient Implementation           | 92  |

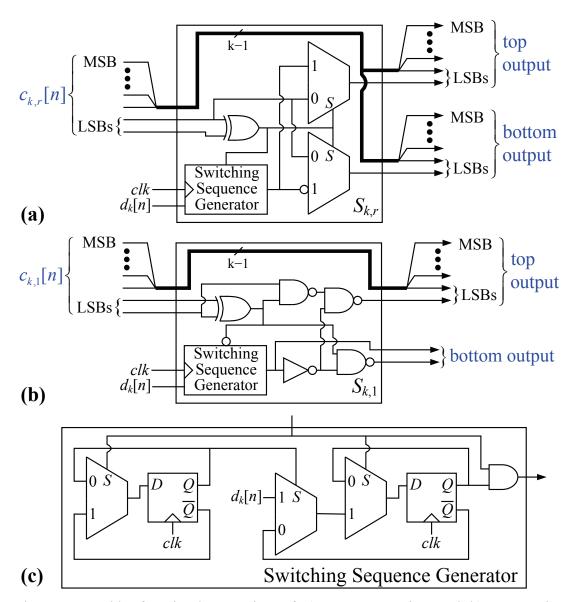

|           | A. Adder-free Non-segmenting Switching Blocks                                    | 94  |

|           | B. Adder-free Local DEM Encoder                                                  | 95  |

|           | C. Adder-free Segmenting Switching Blocks                                        | 95  |

|           | D. Adder-free Multi-rate Quantizing DEM Encoder                                  | 97  |

|           | E. MRQ-DEM $\Delta\Sigma$ Modulator Timing                                       | 102 |

|           | F. Period Distortion Compensating $\Delta\Sigma$ Modulator                       | 104 |

|           | VI. Digitally Controlled Oscillator                                              | 106 |

|           | VII. Measurement Results                                                         | 109 |

|           | Acknowledgements                                                                 | 111 |

|           | Figures                                                                          | 111 |

|           | Tables                                                                           | 126 |

|           | References                                                                       | 128 |

# LIST OF FIGURES

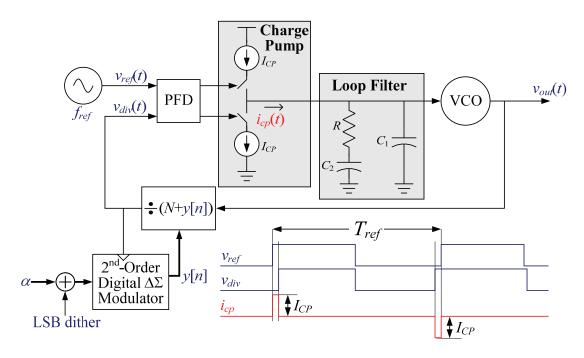

| Figure 1: | A delta-sigma modulator based fractional- $N$ PLL ( $\Delta\Sigma$ -PLL)                                                                                                                      | 34 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

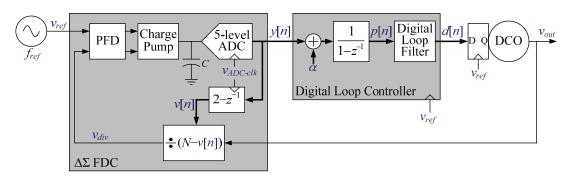

| Figure 2: | A delta-sigma FDC based fractional-N PLL (FDC-PLL)                                                                                                                                            | 34 |

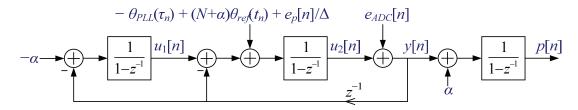

| Figure 3: | The implicit second-order delta-sigma modulator implemented by the $\Delta\Sigma$ FDC followed by the $\alpha$ adder and accumulator of the digital loop controlled                           |    |

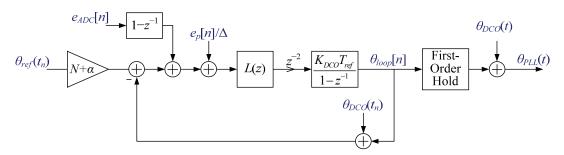

| Figure 4: | Phase noise model of the FDC-PLL.                                                                                                                                                             | 35 |

| Figure 5: | PSD of $\theta_{DCO}(t)$ used in the design and simulation of the FDC-PLL example                                                                                                             |    |

| Figure 6: | Calculated PSD plots (smooth curves) and simulated PSD plots (jagged curves) of the FDC-PLL output phase noise resulting from each of the noi sources individually and all together           |    |

| Figure 7: | Calculated and simulated PSD plots of the FDC-PLL output phase noise with all noise sources with and without the $L_{LPF}(z)$ portion of the loop filter.                                     |    |

| Figure 8: | Calculated PSD plot of the FDC-PLL output phase noise with all noise sources, and the corresponding simulated PSD with several non-ideal circ effects taken into account in addition to noise |    |

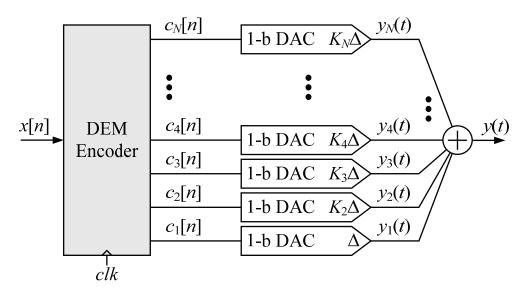

| Figure 9: | A general DEM DAC architecture                                                                                                                                                                | 68 |

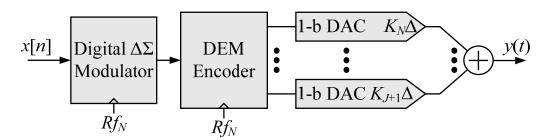

| Figure 10 | ): A general conventional oversampling DEM DAC architecture                                                                                                                                   | 68 |

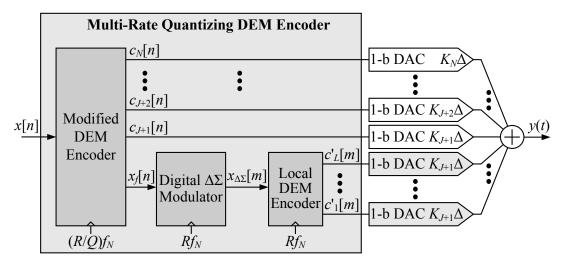

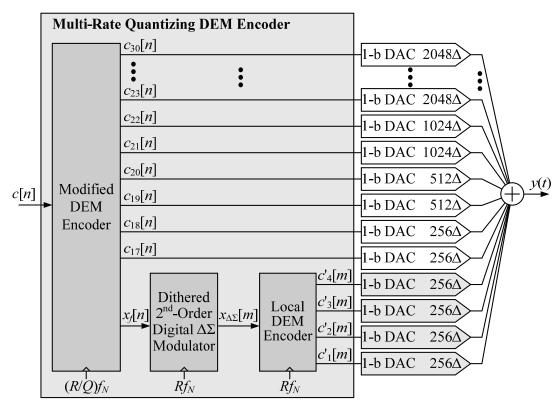

| Figure 11 | : A general oversampling DEM DAC based on the proposed multi-rate quantizing DEM encoder.                                                                                                     | 69 |

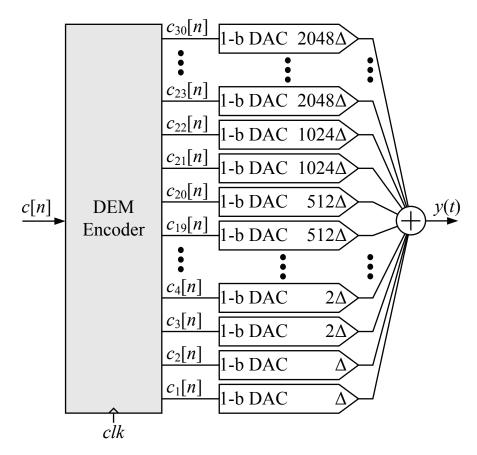

| Figure 12 | 2: The underlying DEM DAC from which the example MRQ-DEM DAC is derived.                                                                                                                      |    |

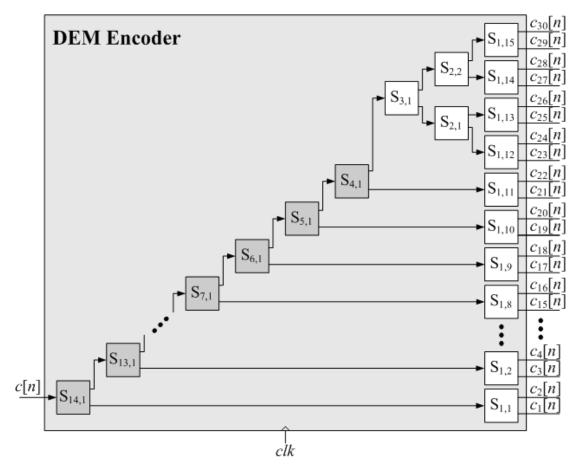

| Figure 13 | 3: Structure of the DEM encoder in the underlying DEM DAC from which the example MRQ-DEM DAC is derived.                                                                                      |    |

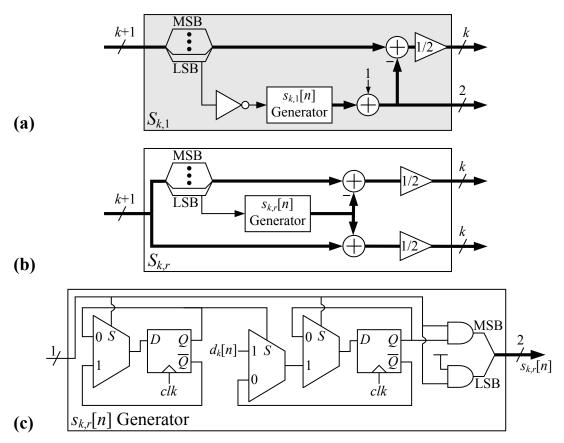

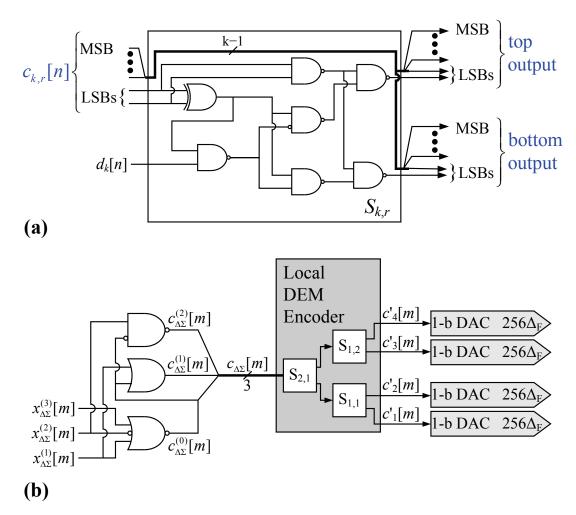

| Figure 14 | 4: Functional diagrams of (a) each segmenting switching block (b) each nor segmenting switching block, and c) the switching sequence generator within each switching block.                   |    |

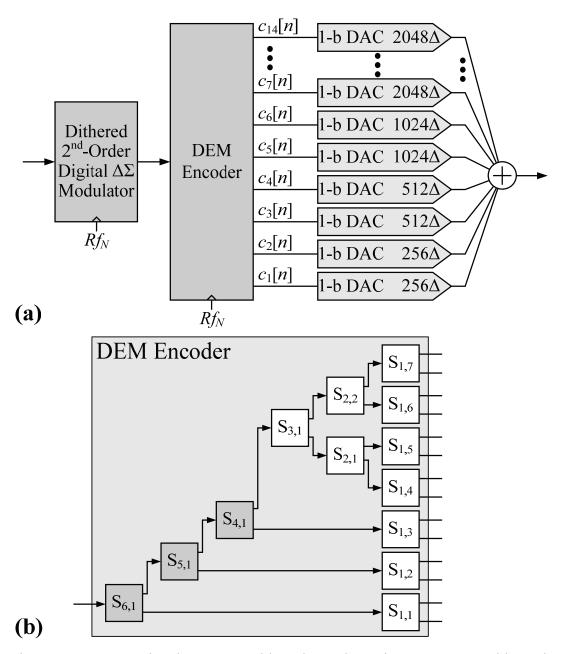

| Figure 15 | 5: High-level diagram of the example MRQ-DEM DAC                                                                                                                                              | 72 |

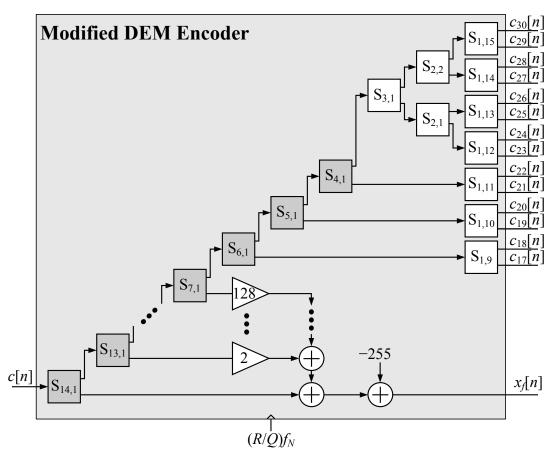

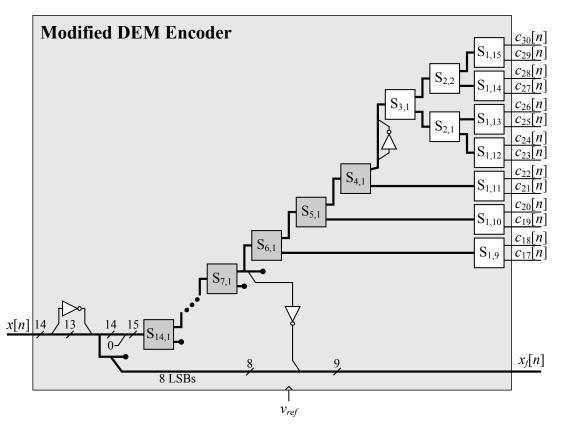

| Figure 16 | 6: Top-level functional diagram of the modified DEM encoder in the MRQ-DEM DAC                                                                                                                |    |

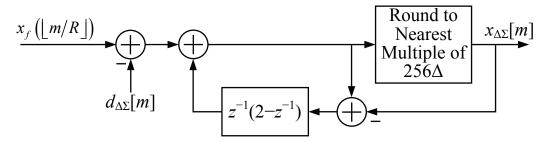

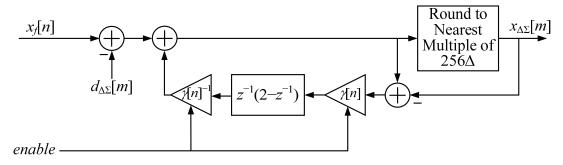

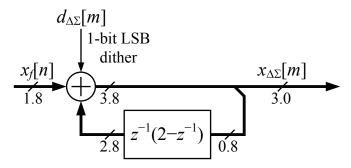

| Figure 17 | 7: Functional diagram of the dithered second-order digital $\Delta\Sigma$ modulator                                                                                                           | 73 |

| Figure 18 | 3: A conventional $\Delta\Sigma$ DAC with an input dynamic range comparable to that of the example MRQ-DEM DAC: (a) high-level diagram of the $\Delta\Sigma$ DAC                              |    |

|            | (b) top-level functional diagram of the DEM encoder                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

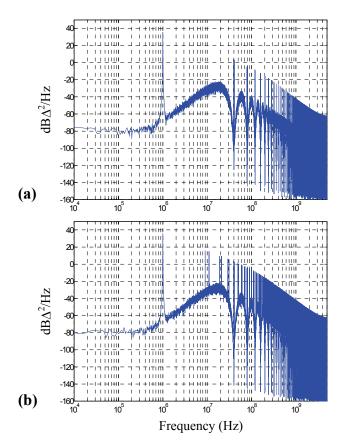

| Figure 19: | Representative output power spectra from simulations of (a) the $\Delta\Sigma$ DAC and (b) the MRQ-DEM DAC with amplitude and time constant mismatches among the 1-bit DACs. |

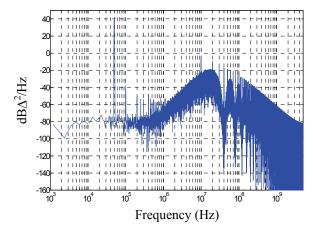

| Figure 20: | Representative output power spectrum from simulation of the MRQ-DEM DAC with DEM disabled                                                                                    |

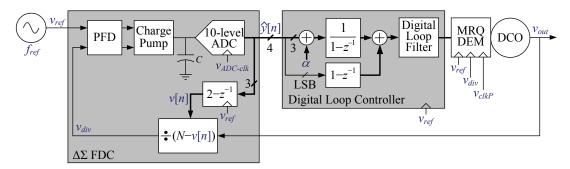

| Figure 21: | Delta-sigma FDC-PLL prototype architecture                                                                                                                                   |

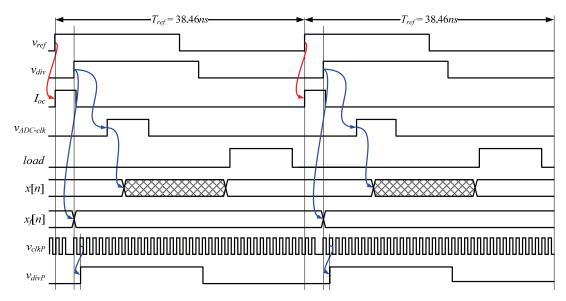

| Figure 22: | Simplified timing diagram of the FDC-PLL synthesizer prototype 112                                                                                                           |

| Figure 23: | Charge pump circuit implementation 112                                                                                                                                       |

| Figure 24: | Comparator for the 10-level flash ADC                                                                                                                                        |

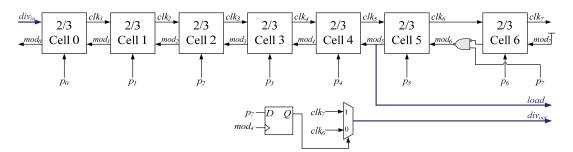

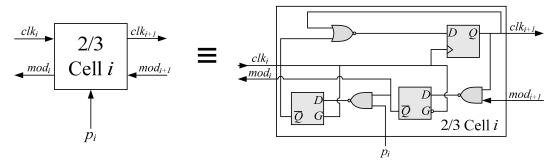

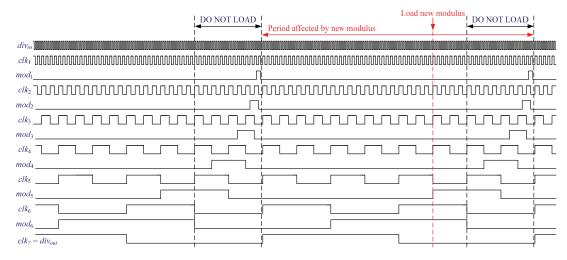

| Figure 25: | Divider architecture 113                                                                                                                                                     |

| Figure 26: | Divide-by-2/3 cell implementation                                                                                                                                            |

| Figure 27: | Representative divider time diagram for the case of a divider modulus equal to 128                                                                                           |

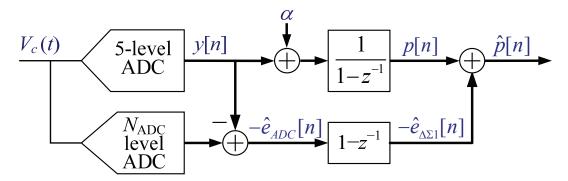

| Figure 28: | Functional diagram of the general quantization noise cancelling algorithm implementation                                                                                     |

| Figure 29: | Effect of quantization noise cancellation on the synthesizer output phase noise                                                                                              |

| Figure 30: | Measured effect of the quantization noise cancelling algorithm 116                                                                                                           |

| Figure 31: | Digital loop controller functional diagram                                                                                                                                   |

| Figure 32: | Adder-free implementation of a) non-segmenting and b) segmenting switching blocks and c) the switching sequence generator                                                    |

| Figure 33: | Implementation of a) non-segmenting switching block in the local DEM encoder and b) the local DEM encoder                                                                    |

| _          | The adder-free modified DEM encoder for an adder-free MRQ-DEM encoder implementation                                                                                         |

| Figure 35: | Functional diagram of the dithered second-order digital $\Delta\Sigma$ modulator with period distortion compensation                                                         |

| Figure 36: | Signal processing diagram of the MRQ-DEM $\Delta\Sigma$ modulator as implemented in the synthesizer prototype                                                                |

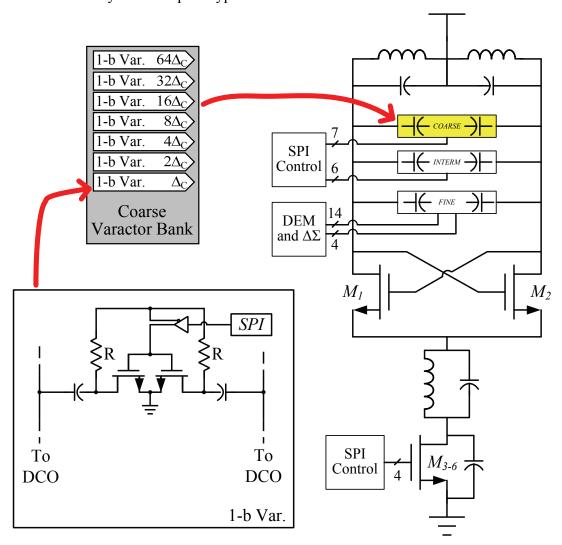

| Figure 37: | Digitally controlled oscillator – coarse tuning bank                                                                                                                         |

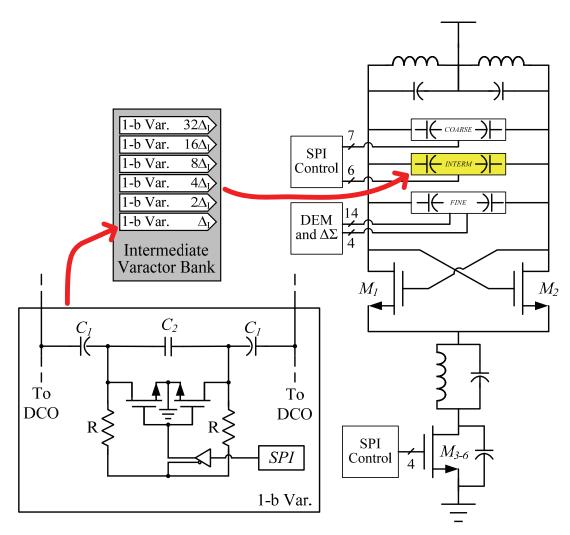

| Figure 38: | Digitally controlled oscillator – intermediate tuning bank                                                                                                                   |

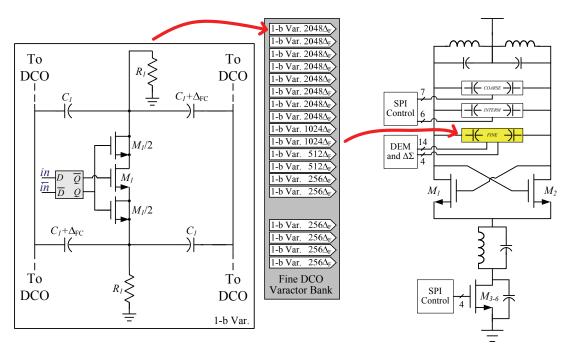

| Figure 39: | Digitally controlled oscillator – fine tuning bank                                                                                                                           |

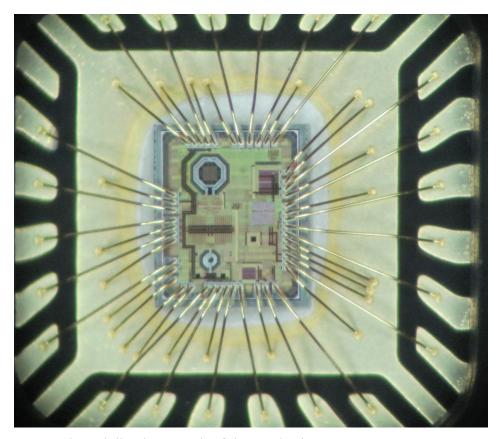

| Figure 40: | Packaged die photograph of the synthesizer prototype                                                                                                                         |

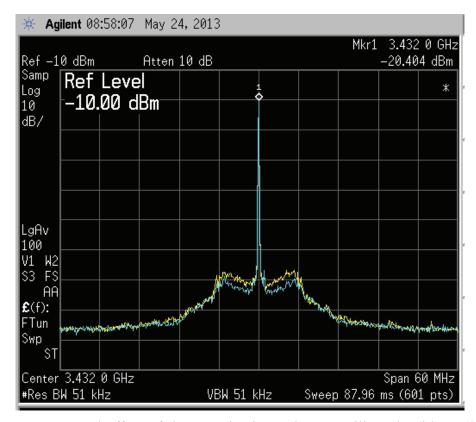

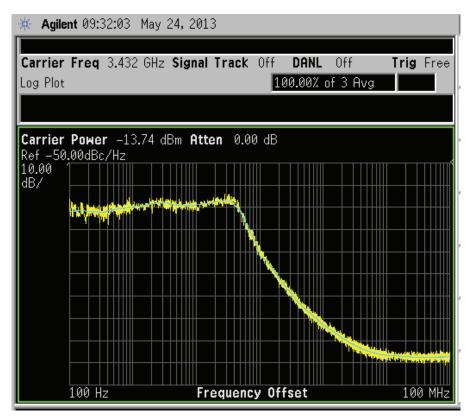

| Figure 41: Representative phase noise plot of the synthesizer prototype for | or a 40 kHz |

|-----------------------------------------------------------------------------|-------------|

| bandwidth                                                                   | 124         |

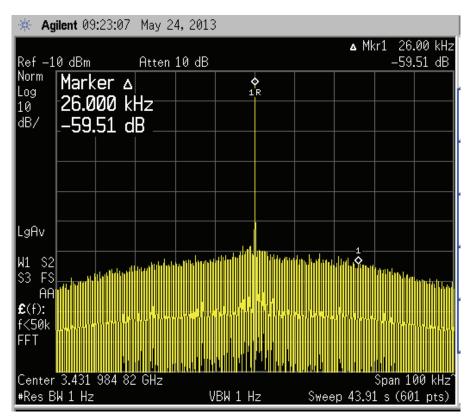

| Figure 42: Best spurious tone performance achieved by the prototype         | 125         |

# LIST OF TABLES

| Table 1: Parameters and evaluation settings of the example FDC-PLL design | 37  |

|---------------------------------------------------------------------------|-----|

| Table 2: Parameters and evaluation settings of the prototype FDC-PLL      | 126 |

| Table 3: Measured phase noise performance of the synthesizer prototype    | 127 |

| Table 4: Measured spurious tone performance of the synthesizer prototype  | 127 |

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor, Professor Ian Galton, for his constant support and encouragement through the course of the past several years. His passion, enthusiasm, mastery and commitment to this field were fundamental to my choice of starting my research endeavors. His guidance, daily advice and faith in this work made him a mentor and friend.

I want to thank Kevin Wang for his technical and personal advice, the very many hours he dedicated to mentor me and his constant encouragement.

I would like to thank all my lab colleagues and friends for their friendship and support. They were my companions in many technical conversations and enjoyable moments of distraction.

Finally, I would like thank Greg Harrison and Ginger Weavil for their CAD support.

Chapter 1, in full, has been published in the IEEE Transactions on Circuits and Systems I: Regular Papers, volume 60, number 5, pages 1274-1285, May 2013. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

Chapter 2, in full, has been submitted for review to the IEEE Transactions on Circuits and Systems I: Regular Papers. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

# VITA

| 2013        | Doctor of Philosophy in Electrical Engineering (Electronic Circuits   |

|-------------|-----------------------------------------------------------------------|

|             | and Systems), University of California, San Diego                     |

| 2007        | Laurea specialistica degree in Electrical Engineering, University of  |

|             | Padova, Italy                                                         |

| 2006 – 2007 | EAP Exchange Student, University of California, San Diego             |

| 2005        | Laurea degree in Information Engineering, University of Padova, Italy |

#### ABSTRACT OF THE DISSERTATION

Delta-Sigma FDC Based Fractional-N PLLs with

Multi-Rate Quantizing Dynamic Element Matching

by

## Christian Venerus

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2013

Professor Ian A. Galton, Chair

Fractional-N phase-locked loop (PLL) frequency synthesizers are ubiquitous in modern communication systems, where they are used to synthesize a signal of high spectral purity from a reference signal of much lower frequency. In order to meet the requirements of wireless communication standard, strict limitation are placed on the

spectral content of the synthesized signal.

In recent years, PLL based on time-to-digital converters (TDC-PLLs) have been proposed that aim at moving the complexity of the design from the analog section to the digital section of the synthesizer: the advantages are a reduction in area, cost and power consumption over competing architectures based on delta-sigma modulation and charge pumps ( $\Delta\Sigma$ -PLLs). Although TDC-PLLs with good performance have been demonstrated, TDC quantization noise has so far kept their phase noise and spurious tone performance below that of the best comparable  $\Delta\Sigma$ -PLLs. An alternative approach is to use a delta-sigma frequency-to-digital converter ( $\Delta\Sigma$  FDC) in place of a TDC to retain the benefits of TDC-PLLs and  $\Delta\Sigma$ -PLLs.

Chapter 1 describes a practical  $\Delta\Sigma$  FDC based PLL in which the quantization noise is equivalent to that of a  $\Delta\Sigma$ -PLL. It presents a linearized model of the PLL, design criteria to avoid spurious tones in the  $\Delta\Sigma$  FDC quantization noise, and a design methodology for choosing the loop parameters in terms of standard PLL target specifications.

Chapter 2 presents a multi-rate quantizing dynamic element matching (DEM) encoder for digital to analog converters (DACs) that allows a significant reduction in the encoder power consumption with respect to a conventional encoder for oversampling DEM DACs, at the expense of a minimal signal-to-noise ratio reduction.

In Chapter 3, the implementation details of a  $\Delta\Sigma$  FDC based fractional-N phase-locked loop prototype are shown. The PLL was built to showcase the capability of the architecture analyzed in Chapter 1 to comply with the most stringent wireless

communication standards. The prototype extends the architecture described in Chapter 1 by including an FDC quantization noise cancelling algorithm, and an hardware efficient implementation of a multi-rate quantizing DEM encoder for digital to frequency conversion.

# Chapter 1

# **Delta-Sigma FDC Based Fractional-N PLLs**

**Abstract**—Fractional-*N* phase-locked loop frequency synthesizers based on time-to-digital converters (TDC-PLLs) have been proposed to reduce the area and linearity requirements of conventional PLLs based on delta-sigma modulation and charge pumps ( $\Delta\Sigma$ -PLLs). Although TDC-PLLs with good performance have been demonstrated, TDC quantization noise has so far kept their phase noise and spurious tone performance below that of the best comparable  $\Delta\Sigma$ -PLLs. An alternative approach is to use a delta-sigma frequency-to-digital converter ( $\Delta\Sigma$  FDC) in place of a TDC to retain the benefits of TDC-PLLs and  $\Delta\Sigma$ -PLLs. This paper proposes a practical  $\Delta\Sigma$  FDC based PLL in which the quantization noise is equivalent to that of a  $\Delta\Sigma$ -PLL. It presents a linearized model of the PLL, design criteria to avoid spurious tones in the  $\Delta\Sigma$  FDC quantization noise, and a design methodology for choosing the loop parameters in terms of standard PLL target specifications.

#### I. Introduction

Delta-sigma modulator based fractional-N phase-locked loops ( $\Delta\Sigma$ -PLLs) of

Manuscript received February 24, 2012; revised August 01, 2012; accepted August 24, 2012. Date of publication November 16, 2012. date of current version April 24, 2013. This work was supported by the National Science Foundation under Award 0914748. This paper was recommended by Associate Editor J. Kim.

The authors are with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093 USA (e-mail:galton@ucsd.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org

Digital Object Identifier 10.1109/TCSI.2012.2221197

the type shown in Figure 1 are widely used as local oscillator frequency synthesizers in wireless communication systems because they offer excellent spectral purity with virtually unlimited frequency tuning resolution [1-4]. Unfortunately, to achieve the performance necessary for most wireless applications a  $\Delta\Sigma$ -PLL requires a highly-linear charge pump and large loop filter capacitance, often on the order of hundreds of pico-Farads. Typically, this necessitates an off-chip loop filter, which increases the pin count, circuit footprint, and overall system cost. Furthermore, in highly-scaled CMOS technology, low voltage headroom on the input node of the voltage controlled oscillator (VCO) necessitates tradeoffs that limit performance. Reducing the voltage swing requires an increase in the VCO gain which tends to increase the phase noise, yet increasing the voltage swing for a given supply voltage reduces charge pump linearity which increases spurious tones.

Recently, fractional-N PLLs have been proposed that exploit digital signal processing to avoid these problems [5, 6, 7, 8, 9, -10]. They use a time-to-digital converter (TDC), a digital loop filter, and a digitally controlled oscillator (DCO) in place of a divider, phase-frequency detector (PFD), charge pump, analog loop filter, and VCO. The TDC generates a quantized estimate of the instantaneous phase of the DCO at each positive edge of the reference oscillator. The difference between the TDC output and the calculated instantaneous phase of an ideal oscillator running at the desired output frequency is digitally lowpass filtered and the resulting digital sequence controls the DCO.

Although such TDC-based PLLs (TDC-PLLs) have been demonstrated to

have very good performance, TDC quantization noise has so far kept their phase noise and spurious tone performance below those of the best comparable  $\Delta\Sigma$ -PLLs. TDC quantization noise is relatively coarse and, unlike quantization noise in  $\Delta\Sigma$ -PLLs, it is not highpass shaped so it is not as well suppressed by the PLL.

An alternative approach that offers the advantages of both  $\Delta\Sigma$ -PLLs and TDC-PLLs is to use a delta-sigma frequency-to-digital converter ( $\Delta\Sigma$  FDC) in place of a TDC [11, 12, 13, -14]. Such  $\Delta\Sigma$  FDC based fractional-N PLLs (FDC-PLLs) have been proposed in which the  $\Delta\Sigma$  FDC performs 1-bit quantization and the DCO is implemented as a DAC followed by a VCO [15, 16]. It is likely that improved performance can be achieved in future FDC-PLLs by using the type of high-performance DCOs developed for TDC-PLLs and, as quantified in this paper, by avoiding 1-bit quantization in the  $\Delta\Sigma$  FDC.

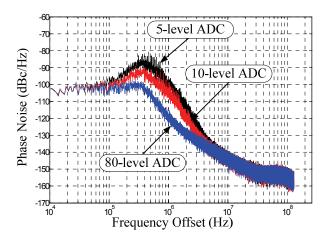

This paper proposes a practical FDC-PLL architecture and proves that its quantization noise performance is equivalent to that of a  $\Delta\Sigma$ -PLL with a second-order delta-sigma modulator. It shows that 5-level quantization in the  $\Delta\Sigma$  FDC is both necessary and sufficient to avoid spurious tones that would otherwise be caused by quantizer overloading. It derives a linearized model that accurately predicts the transfer functions imposed by the FDC-PLL on its component noise sources, and provides a design methodology based on the model for choosing the loop parameters in terms of standard PLL target specifications.

#### II. BACKGROUND INFORMATION

## A. Phase Noise in Fractional-N PLLs

The instantaneous frequency of the reference oscillator in Hz is

$$f_{ref} + \psi_{ref}(t) \tag{1}$$

where  $f_{ref}$  is the nominal reference frequency, and  $\psi_{ref}(t)$  is the reference oscillator's instantaneous frequency error. The reference oscillator's instantaneous phase in cycles relative to an initial time,  $t_0$ , is the integral of (1) from time  $t_0$  to time t:

$$p_{ref}(t) = (t - t_0) f_{ref} + \theta_{ref}(t)$$

(2)

where

$$\theta_{ref}(t) = \int_{t_0}^t \psi_{ref}(u) du \tag{3}$$

is the reference oscillator's instantaneous phase noise in cycles.

A fractional-N PLL generates a periodic output signal with an average frequency of  $(N+\alpha)f_{ref}$ , where N is an integer and  $\alpha$  is a fractional value with a magnitude less than 1. Therefore, its instantaneous output frequency in Hz can be written as

$$f_{PLL}(t) = (N + \alpha) f_{ref} + \psi_{PLL}(t)$$

(4)

where  $\psi_{PLL}(t)$  is its instantaneous frequency error. The PLL's instantaneous output phase in cycles relative to time  $t_0$  is the integral of (4) from time  $t_0$  to time t:

$$p_{PLL}(t) = (t - t_0)(N + \alpha) f_{ref} + \theta_{PLL}(t)$$

(5)

where

$$\theta_{PLL}(t) = \int_{t_0}^t \psi_{PLL}(u) du \tag{6}$$

is the PLL's instantaneous phase noise in cycles.

A fractional-N PLL must control its output frequency such that  $\psi_{PLL}(t)$  has zero mean and the power spectral density (PSD) of  $\theta_{PLL}(t)$  is within acceptable limits for the desired application. As described below, the  $\Delta\Sigma$ -PLL and the FDC-PLL each do this by estimating a phase error sequence proportional to

$$-\theta_{PLL}(t) + (N + \alpha)\theta_{ref}(t) \tag{7}$$

sampled at the reference frequency, passing the estimated phase error sequence through their loop filter, and using the output of the loop filter to control the output frequency of their VCO or DCO. The feedback ensures that  $\psi_{PLL}(t)$  has zero mean (provided that  $\psi_{ref}(t)$  has zero mean), and the characteristics of the loop filter, the DC loop gain, and the accuracy with which (7) is estimated determine the spectral properties of  $\theta_{PLL}(t)$ .

## B. $\Delta\Sigma$ Fractional-N PLLs

A typical  $\Delta\Sigma$ -PLL is shown in Figure 1. It consists of a PFD, a charge pump, an analog loop filter, a VCO, a frequency divider, and a second-order digital delta-sigma modulator clocked by the divider output.

The divider output is a two-level signal in which the nth and (n+1)th rising edges are separated by N + y[n] VCO periods, where y[n] is an integer-valued sequence from the delta-sigma modulator. As indicated in the figure for the case where the PLL is locked, if the nth rising edge of the reference signal,  $v_{ref}(t)$ , occurs before that of the divider output,  $v_{div}(t)$ , the charge pump generates a current pulse of nomi-

nal amplitude  $I_{CP}$  and duration equal to the time difference between the two edges. Otherwise, the pulse has the same magnitude and duration, but its polarity is reversed.

The input to the delta-sigma modulator is  $\alpha$  plus pseudo-random least significant bit dither, d[n], so its output has the form  $y[n] = \alpha + d[n] + e_{\Delta\Sigma}[n]$ , where  $e_{\Delta\Sigma}[n]$  is second-order highpass shaped delta-sigma quantization noise. As proven in [17], the dither prevents  $e_{\Delta\Sigma}[n]$  from containing spurious tones that would otherwise show up as spurious tones in the  $\Delta\Sigma$ -PLL's output.

As shown in [18], the net charge delivered to the loop filter by the charge pump's current pulse each reference period is proportional to the sum of a phase error term and first-order highpass shaped delta-sigma quantization noise. The phase error term is

$$-\theta_{PLL}(\tau_n) + (N + \alpha)\theta_{ref}(t_n) \tag{8}$$

where  $t_n$  and  $\tau_n$ , are the times of the positive-going zero-crossings of  $v_{ref}(t)$  and  $v_{div}(t)$ , respectively, corresponding to the *n*th charge pump pulse.

The loop bandwidth of the  $\Delta\Sigma$ -PLL is designed to be low enough that the delta-sigma quantization noise is largely suppressed by the lowpass filtering operation of the loop. Hence, the average output frequency settles to  $(N + \alpha)f_{ref}$ , as desired, with the delta-sigma quantization noise contributing only a small amount of phase noise.

## III. OVERVIEW OF THE FDC-PLL

## A. System Description

The proposed FDC-PLL is shown in Figure 2. It consists of three main components: a  $\Delta\Sigma$  FDC, a digital loop controller, and a DCO. The digital loop controller is clocked and the output of the digital loop controller is latched into the DCO on each rising edge of the reference signal.

The  $\Delta\Sigma$  FDC consists of a PFD, charge pump, integrating capacitor, 5-level ADC,  $2-z^{-1}$  digital block, and multi-modulus divider. The PFD and charge pump are the same as those in a  $\Delta\Sigma$ -PLL. As in a  $\Delta\Sigma$ -PLL, when the FDC-PLL is locked the magnitude of the difference between the time of each rising edge of  $v_{div}(t)$  and the time of the corresponding rising edge  $v_{ref}(t)$  is a small fraction of the reference oscillator period,  $T_{ref}$ . Therefore, the charge pump generates a relatively narrow (compared to  $T_{ref}$ ) positive or negative pulse of current around the time of each rising edge of  $v_{ref}(t)$ . The 5-level ADC is clocked with a delayed version of the reset signal within the PFD, such that it samples the capacitor voltage shortly after each charge pump current pulse settles to zero. The divider in the FDC-PLL is identical to that in a  $\Delta\Sigma$ -PLL, but its modulus is varied by v[n] = 2v[n] - v[n-1] instead of v[n].

By design,  $\alpha$  is restricted to the range

$$-\frac{1}{2} \le \alpha \le \frac{1}{2} \tag{9}$$

and the charge pump current,  $I_{CP}$ , ideally satisfies

$$I_{CP} = (N + \alpha) f_{ref} C\Delta \tag{10}$$

where  $\Delta$  is the step-size of the 5-level ADC.<sup>†</sup>

As shown in the Appendix, the  $\Delta\Sigma$  FDC implicitly implements second-order delta-sigma modulation. In particular,  $y[n] + \alpha$  is a measure of the PLL's frequency error plus second-order highpass shaped ADC quantization noise, so it averages to zero when the average DCO frequency is  $(N+\alpha)f_{ref}$ .

The accumulator in the digital loop controller converts the PLL's frequency error to phase error and reduces the second-order highpass shaped ADC quantization noise to first-order highpass shaped ADC quantization noise. Specifically, as shown in Section IV the output of the accumulator, p[n], consists of the phase error term given by (8) plus first-order highpass shaped ADC quantization noise. Therefore, the properties of p[n] are very similar to those of the sequence of charge pulses delivered by the charge pump to the analog loop filter in the  $\Delta\Sigma$ -PLL of Figure 1. Accordingly, the digital loop filter in the FDC-PLL performs the same function as the analog loop filter in the  $\Delta\Sigma$ -PLL. It suppresses out-of-band quantization noise and circuit error, and sets the loop dynamics.

The DCO is an analog oscillator with a means for the frequency to be controlled by a digital sequence, in this case the output of the digital loop filter, d[n]. Depending on the transfer function of the digital loop filter, the required DCO frequency change corresponding to the minimum step-size of d[n] can be very small. A common method of implementing a DCO with a very small minimum frequency step is to

<sup>&</sup>lt;sup>†</sup> As demonstrated in Section IV, deviations of the charge pump current sources on the order of several percent do not significantly degrade the performance of the FDC-PLL. Therefore, since  $\alpha$  typically has a magnitude much smaller than N, usually it is reasonable to set  $I_{CP} = N f_{ref} C \Delta$ .

quantize d[n] with a digital delta-sigma modulator clocked at a rate much higher than the reference frequency, where the clock signal is obtained by dividing the PLL output signal by a small integer [19]. For each value of d[n], the delta-sigma modulator generates multiple output values with a minimum step-size greater than that of d[n] which are used to modulate the frequency of the DCO. The natural lowpass filtering imposed by the DCO suppresses much of the quantization noise introduced by the delta-sigma modulator, so the effective minimum frequency step of the DCO is that of d[n] at the cost of additive phase noise.

In this paper, any quantization of d[n] performed by the DCO as described above is considered to happen within the DCO, so it is not shown explicitly in Figure 2. Accordingly, the *DCO phase noise* is defined to be the sum of the phase noise caused by analog oscillator noise and any phase noise caused by quantizing d[n] within the DCO.

## B. Digital Loop Filter

Given that the digital loop filter in the FDC-PLL plays the role of the analog loop filter in the  $\Delta\Sigma$ -PLL, it is reasonable to design the digital loop filter such that it has comparable filtering characteristics to the analog loop filter shown in Figure 1. This can be achieved with a digital loop filter transfer function of

$$L(z) = L_{PI}(z)L_{LPF}(z) \tag{11}$$

where

$$L_{PI}(z) = K_P + K_I \frac{1}{1 - z^{-1}}, \tag{12}$$

$K_P$  and  $K_I$  are constants called the *proportional path gain* and *integral path gain*, respectively, and  $L_{LPF}(z)$  is an all-pole lowpass filter section described shortly [20]. The  $L_{PI}(z)$  portion of the filter is often called a proportional-integral filter and is sufficient to obtain a stable feedback system. The  $L_{LPF}(z)$  portion of the filter provides attenuation above the PLL bandwidth to reduce phase noise.

Such a digital loop filter has comparable filtering characteristics to the analog loop filter shown in Figure 1 if  $L_{LPF}(z)$  contains a single pole. Unfortunately, neither filter rolls off very sharply with frequency.

In the  $\Delta\Sigma$ -PLL this problem is often addressed by adding an extra pole outside the PLL bandwidth. Usually, no more than one extra pole is added, though, because of the increased area and power consumption associated with adding multiple extra poles.

In contrast, the incremental area and power consumption associated with adding multiple extra poles to a digital filter tend to be modest. Therefore, the loop filter used in the FDC-PLL analyzed in this paper has a transfer function given by (11) with

$$L_{LPF}(z) = \prod_{i=0}^{3} \frac{\lambda_i}{1 - (1 - \lambda_i)z^{-1}}$$

(13)

where  $1 - \lambda_i$  for i = 0, 1, 2, and 3 are real poles. A design procedure for selecting  $K_P$ ,  $K_I$ , and  $\lambda_i$  for i = 0, 1, 2, and 3 in terms of the desired loop bandwidth and phase margin is presented in Section IV.

## C. $\Delta\Sigma$ -PLL and FDC-PLL Capacitance Comparison

It is mentioned in the Introduction that the capacitance in the loop filter of the

$\Delta\Sigma$ -PLL tends to be large, often on the order of hundreds of pico-Farads. To sufficiently suppress the delta-sigma quantization error, the loop bandwidth of a fractional-N PLL is usually a small fraction (e.g., several hundredths) of the reference frequency. With the analog loop filter shown in Figure 1, the loop bandwidth is proportional to  $RI_{CP}$ , and the total capacitance is approximately inversely proportional to R. Therefore, for any given loop bandwidth,  $C_1$  and  $C_2$  can be reduced by simultaneously increasing R and decreasing  $I_{CP}$ . Unfortunately, decreasing  $I_{CP}$  tends to increase the PLL's phase noise because the loop gain of the  $\Delta\Sigma$ -PLL's linearized model is proportional to  $I_{CP}$  [18]. This places a lower bound on  $I_{CP}$  for any given application, which, in turn, typically dictates a large total capacitance when the loop bandwidth is small.

In contrast, as shown in Section IV the loop bandwidth of the FDC-PLL is independent of  $I_{CP}$  and C, and the overall phase noise is not a strong function of either  $I_{CP}$  or C, so C can be much smaller than the loop filter capacitance in a comparable  $\Delta\Sigma$ -PLL. For example, C = 1.25 pF in the FDC-PLL design example presented in Section IV.

#### IV. THE FDC-PLL LINEARIZED MODEL

#### A. Model Derivation

It is proven in the Appendix that the  $\Delta\Sigma$  FDC behaves as the second-order delta-sigma modulator shown in Figure 3 along with the  $\alpha$  adder and accumulator of the digital loop controller. It is further shown that the output of the accumulator can

be written as

$$p[n] = -\theta_{PLL}(\tau_n) + (N + \alpha)\theta_{ref}(t_n) + \frac{e_p[n]}{\Lambda} + e_{\Delta\Sigma 1}[n]$$

(14)

neglecting a possible constant offset, where  $e_p[n]$  represents the combined error from noise and other non-ideal circuit behavior in the charge pump, PFD, and divider,

$$e_{\Delta\Sigma 1}[n] = e_{ADC}[n] - e_{ADC}[n-1],$$

(15)

and  $e_{ADC}[n]$  is the sum of quantization noise and any additional error from non-ideal circuit behavior in the ADC. As explained in the Appendix, a five-level ADC is necessary and sufficient to ensure that the delta-sigma modulator does not overload when the PLL is locked, which would introduce spurious tones.

The output of the loop filter, d[n], is latched into the DCO on each positive-going zero-crossing of  $v_{ref}(t)$ , so d[n-1] is applied to the DCO during the time interval  $t_n < t \le t_{n+1}$  for each positive integer n. It is assumed that the DCO's control word latency is negligible, so its instantaneous frequency during each time interval  $t_n < t \le t_{n+1}$  is

$$f_{PLL}(t) = f_c + K_{DCO}d[n-1] + \psi_{DCO}(t)$$

(16)

where  $f_c$  is the nominal center frequency of the DCO in Hz,  $K_{DCO}$  is the DCO gain in Hz, and  $\psi_{DCO}(t)$  is the DCO's instantaneous frequency error.<sup>†</sup> It follows from (4) and (16) that during the time interval  $t_n < t \le t_{n+1}$  the FDC-PLL's instantaneous frequency error can be written as

$$\psi_{PLL}(t) = f_c - (N + \alpha) f_{ref} + K_{DCO} d[n-1] + \psi_{DCO}(t)$$

(17)

<sup>&</sup>lt;sup>†</sup> The *DCO Gain* is defined as the amount by which the DCO frequency changes when d[n] changes by unity.

The ideal output frequency when the FDC-PLL is locked is  $(N + \alpha)f_{ref}$ , so d[n] can be written as

$$d[n] = \frac{1}{K_{DCO}} \left[ \left( N + \alpha \right) f_{ref} - f_c \right] + f[n]$$

(18)

where f[n] is the zero-mean component of d[n]. It follows from (17) and (18) that

$$\psi_{PLL}(t) = K_{DCO}f[n-1] + \psi_{DCO}(t)$$

(19)

during the time interval  $t_n < t \le t_{n+1}$  for each positive integer n.

Integrating (19) from time  $t_0$  to t where  $t_n < t \le t_{n+1}$  gives

$$\theta_{PLL}(t) = K_{DCO} \sum_{k=1}^{n-1} (t_{k+1} - t_k) f[k-1] + K_{DCO} f[n-1](t-t_n) + \theta_{DCO}(t)$$

(20)

where

$$\theta_{DCO}(t) = \int_{t_0}^t \psi_{DCO}(u) du \tag{21}$$

is the instantaneous phase noise introduced by the DCO. Typical reference oscillators have high spectral purity, so

$$t_{k+1} - t_k \cong T_{ref} \tag{22}$$

holds to a high degree of accuracy. Hence, (20) implies that  $\theta_{PLL}(t)$  can be written as

$$\theta_{PLL}(t) = K_{DCO} T_{ref} \sum_{k=1}^{n-1} f[k-1] + K_{DCO} f[n-1](t-t_n) + \theta_{DCO}(t)$$

(23)

for  $t_n \le t \le t_{n+1}$  which can be rewritten as

$$\theta_{PLL}(t) = \theta_{DCO}(t) + (\theta_{loop}[n+1] - \theta_{loop}[n]) \frac{(t-t_n)}{T_{ref}} + \theta_{loop}[n]$$

(24)

where

$$\theta_{loop}[n] = K_{DCO} T_{ref} \sum_{k=1}^{n-1} f[k-1].$$

(25)

The second and third term in (24) represent a linear interpolation between the nth and (n+1)th samples of  $\theta_{loop}[n]$ . This type of interpolation is called *first-order hold* interpolation [21]. To extend (24) to hold for any  $t > t_0$ , the first-order hold component can be written as a sequence of triangular time pulses with amplitudes  $\theta_{loop}[n]$ , i.e.,

$$\theta_{PLL}(t) = \theta_{DCO}(t) + \sum_{n=0}^{\infty} \theta_{loop}[n] h_{tri}(t - nT_{ref} - t_0)$$

(26)

for arbitrary  $t > t_0$ , where

$$h_{tri}(t) = \begin{cases} 1 - \frac{|t|}{T_{ref}} & \text{if } |t| < T_{ref}, \\ 0 & \text{otherwise.} \end{cases}$$

(27)

The bandwidth of a practical PLL is much smaller than the reciprocal of the maximum magnitude of the difference between  $\tau_n$  and  $t_n$ , so

$$\theta_{PLL}\left(\tau_{n}\right) \cong \theta_{PLL}\left(t_{n}\right) \tag{28}$$

holds to a high degree of accuracy. Hence (24) yields

$$\theta_{PLL}(\tau_n) \cong \theta_{DCO}(t_n) + \theta_{loop}[n].$$

(29)

Combining (14), (15), (25), (26), and (29) results in the linearized model

shown in Figure 4 where the sample-rate of the discrete-time blocks and the first-order hold interpolator is  $f_{ref}$ . The discrete-time portion of the model implements the FDC-PLL's feedback system and generates  $\theta_{loop}[n]$ , which is linearly interpolated by the first-order hold block as described above.

It follows from Figure 4 that the discrete-time loop gain of the FDC-PLL is

$$T(z) = K_{DCO} T_{ref} L(z) \frac{z^{-2}}{1 - z^{-1}}$$

(30)

and the various FDC-PLL discrete-time transfer functions are

$$\frac{\theta_{loop}}{\theta_{ref}}(z) = (N + \alpha) \frac{T(z)}{1 + T(z)}$$

(31)

$$\frac{\theta_{loop}}{\theta_{DCO}}(z) = -\frac{T(z)}{1 + T(z)} \tag{32}$$

$$\frac{\theta_{loop}}{e_{ADC}}(z) = (1 - z^{-1}) \frac{T(z)}{1 + T(z)}$$

(33)

and

$$\frac{\theta_{loop}}{e_p}(z) = \frac{1}{\Delta} \left( \frac{T(z)}{1 + T(z)} \right). \tag{34}$$

These equations describe the loop dynamics of the FDC-PLL.

#### B. Phase Noise PSD Calculation

It is assumed that the noise signals  $\theta_{ref}(t_n)$ ,  $e_{ADC}[n]$ ,  $e_p[n]$ , and  $\theta_{DCO}(t)$  can be modeled as uncorrelated, zero-mean, wide-sense stationary random processes, so the PSD of  $\theta_{PLL}(t)$  is the sum of PSD components that each correspond to one of the noise signals. Likewise, the discrete-time PSD of  $\theta_{loop}[n]$  is the sum of the discrete-time

PSD components that each correspond to one of the noise signals.

It follows from (31) that the component of the discrete-time PSD of  $\theta_{loop}[n]$  corresponding to  $\theta_{ref}(t_n)$  is

$$S_{\theta_{ref}}\left(e^{j2\pi T_{ref}f}\right)\left|\left(N+\alpha\right)\frac{T\left(e^{j2\pi T_{ref}f}\right)}{1+T\left(e^{j2\pi T_{ref}f}\right)}\right|^{2} \tag{35}$$

where  $S_{\theta_{ref}}\left(e^{j2\pi T_{ref}f}\right)$  is the discrete-time PSD of  $\theta_{ref}(t_n)$ . The continuous-time Fourier transform of the output of a first-order hold interpolator with input u[n] and sample-rate  $f_{ref}$  is

$$U\left(e^{j2\pi T_{ref}f}\right)T_{ref}\left[\frac{\sin\left(\pi T_{ref}f\right)}{\pi T_{ref}f}\right]^{2}$$

(36)

where  $U\left(e^{j2\pi T_{ref}f}\right)$  is the discrete-time Fourier transform of u[n] [21]. Therefore, the component of the PSD of  $\theta_{PLL}(t)$  corresponding to  $\theta_{ref}(t_n)$  is

$$S_{\theta_{ref}}\left(e^{j2\pi T_{ref}f}\right)T_{ref}\left|\frac{\left(N+\alpha\right)T\left(e^{j2\pi T_{ref}f}\right)}{1+T\left(e^{j2\pi T_{ref}f}\right)}\right|^{2}\left[\frac{\sin\left(\pi T_{ref}f\right)}{\pi T_{ref}f}\right]^{4}$$

(37)

By similar reasoning, the component of the PSD of  $\theta_{PLL}(t)$  corresponding to  $e_p[n]$  is

$$S_{e_p}\left(e^{j2\pi T_{ref}f}\right) \frac{T_{ref}}{\Delta^2} \left| \frac{T\left(e^{j2\pi T_{ref}f}\right)}{1 + T\left(e^{j2\pi T_{ref}f}\right)} \right|^2 \left[ \frac{\sin\left(\pi T_{ref}f\right)}{\pi T_{ref}f} \right]^4$$

(38)

where  $S_{e_p}\left(e^{j2\pi T_{ref}f}\right)$  is the discrete-time PSD of  $e_p[n]$ .

As described in the Appendix,  $e_{ADC}[n]$  is asymptotically white and uniformly

distributed between -0.5 and 0.5, so the discrete-time PSD of  $e_{ADC}[n]$  is 1/12. It follows from reasoning similar to that which led to (37) and (38) that the component of the PSD of  $\theta_{PLL}(t)$  corresponding to  $e_{ADC}[n]$  is

$$\frac{T_{ref}}{3}\sin^2\left(\pi T_{ref}f\right) \left| \frac{T\left(e^{j2\pi T_{ref}f}\right)}{1+T\left(e^{j2\pi T_{ref}f}\right)} \right|^2 \left[ \frac{\sin\left(\pi T_{ref}f\right)}{\pi T_{ref}f} \right]^4$$

(39)

in units of cycles squared per Hz. If the desired units of the PSD are radians squared per Hz, then (39) must be scaled by  $4\pi^2$ .

The component of the PSD of  $\theta_{PLL}(t)$  corresponding to DCO phase noise depends on both  $\theta_{DCO}(t)$  and  $\theta_{DCO}(t_n)$ , which are obviously correlated. Consequently, the effects of  $\theta_{DCO}(t)$  and  $\theta_{DCO}(t_n)$  must be considered together when calculating the component of the PSD of  $\theta_{PLL}(t)$  corresponding to DCO noise.

The component of  $\theta_{loop}[n]$  corresponding to DCO noise is  $\theta_{DCO}(t_n)$  filtered by the discrete-time lowpass transfer function (32). As implied by (36), the first-order hold interpolator imposes a continuous-time lowpass filtering operation on this signal component that rolls off in frequency at 40 dB per decade. As shown in Figure 4,  $\theta_{DCO}(t)$  is added to the output of the first-order hold interpolator and for a typical DCO the PSD of  $\theta_{DCO}(t)$  rolls off in frequency by no more than 20 dB per decade (except at low frequencies where 1/f noise is significant). Therefore, in calculating the component of the PSD of  $\theta_{PLL}(t)$  corresponding to DCO noise, the output of the first-order hold interpolator can be neglected for frequencies above  $f_{ref}/2$  with a high degree of accuracy.

It follows that the effect of adding  $\theta_{DCO}(t_n)$  in the feedback loop of Figure 4 is

practically equivalent to adding  $\theta_{DCO}(t)$  filtered by

$$-\frac{T\left(e^{j2\pi T_{ref}f}\right)}{1+T\left(e^{j2\pi T_{ref}f}\right)} \left[\frac{\sin\left(\pi T_{ref}f\right)}{\pi T_{ref}f}\right]^{2} \tag{40}$$

to the output of the first-order hold interpolator. This result relies on the reasonable assumption that aliasing error in  $\theta_{DCO}(t_n)$  within the passband of (32) is negligible. It follows that the component of the PSD of  $\theta_{PLL}(t)$  corresponding to DCO noise is

$$S_{\theta_{DCO}}(f) \left| 1 - \frac{T(e^{j2\pi T_{ref}f})}{1 + T(e^{j2\pi T_{ref}f})} \left[ \frac{\sin(\pi T_{ref}f)}{\pi T_{ref}f} \right]^{2} \right|^{2}$$

$$(41)$$

where  $S_{\theta_{DCO}}(f)$  is the continuous-time PSD of  $\theta_{DCO}(t)$ .

The PSD of  $\theta_{PLL}(t)$  from all of the FDC-PLL noise sources is the sum of (37), (38), (39), and (41). Typically, estimates of  $S_{\theta_{ref}}\left(e^{j2\pi T_{ref}f}\right)$ ,  $S_{e_p}\left(e^{j2\pi T_{ref}f}\right)$ , and  $S_{\theta_{DCO}}(f)$  are obtained via circuit simulation. As described in Section II, the DCO phase noise is the combination of phase noise introduced by the underlying analog oscillator and any quantization of d[n], so circuit simulations used to estimate the DCO phase noise PSD must include any such quantization noise.

## C. Loop Filter Design

The loop filter transfer function, L(z), determines the FDC-PLL's loop bandwidth, phase margin, and noise filtering characteristics. In analogy to a conventional  $\Delta\Sigma$ -PLL, the FDC-PLL's phase noise consists of highpass filtered DCO noise, i.e., (41), and lowpass filtered noise from the reference oscillator, ADC, divider, PFD, and

charge pump, i.e., (37)-(39). The design objective for L(z) is to strike a compromise among these noise filtering operations appropriate to the application's requirements while maintaining a given desired loop bandwidth and phase margin.

In a  $\Delta\Sigma$ -PLL, having a zero-frequency pole in the loop filter ensures the charge pump output current pulse sequence has zero mean, which simplifies the design of both the charge pump and PFD [4]. In contrast, the delta-sigma modulator relationship derived in the Appendix implies that in the FDC-PLL the charge pump output current pulse sequence has zero mean regardless of whether the loop filter has a zero-frequency pole. Therefore, a major reason for having a zero-frequency loop filter pole in  $\Delta\Sigma$ -PLLs does not apply to the FDC-PLL.

Nevertheless, there are still advantages to having a zero-frequency pole in an FDC-PLL's loop filter. One advantage is that it causes the transfer function portion of (41) to have a second zero-frequency zero. DCO phase noise typically has a PSD proportional to  $1/f^3$  for  $0 < f < f_c$  where  $f_c$  is the frequency below which 1/f noise is significant. Having two zero-frequency zeros in the transfer function portion of (41) prevents the portion of the PSD proportional to  $1/f^3$  from contributing significantly to the overall FDC-PLL phase noise. Another advantage is that the zero-frequency pole eliminates the dependence of  $\theta_{PLL}(t)$  on the DCO's center frequency and gain, which both vary with process, supply voltage, and temperature.

The primary disadvantage of having a zero-frequency pole in the loop filter is that it introduces negative phase into the loop gain which limits the achievable sharpness of the filter's transition band for a given phase margin. Therefore, in some applications not having a zero-frequency pole in the loop filter may offer an advantage with respect to minimizing phase noise.

Unlike the case of an analog PLL, there is a great deal of flexibility in the choice of L(z), regardless of whether it has a zero-frequency pole. The remainder of this section evaluates the practical choice of L(z) given by (11) with (12) and (13), which includes a zero-frequency pole.

A reasonable design procedure is to first choose values of  $K_P$  and  $K_I$  via the equations derived below that result in the desired loop bandwidth and phase margin to the extent that

$$\left| L_{LPF} \left( e^{j2\pi T_{ref} f_u} \right) \right|^2 \cong 1 \quad \text{and} \quad 2\pi T_{ref} f_u \ll 1$$

(42)

where  $f_u$  is the unity-gain frequency of the FDC-PLL's loop gain. This requires that the poles of  $L_{LPF}(z)$  be initially chosen such that

$$2\pi T_{ref} f_u \ll \lambda_i < 1. \tag{43}$$

Then a trial and error procedure can be used in which the  $\lambda_i$  values are reduced to improve noise suppression while the  $K_P$  and  $K_I$  values are adjusted to maintain the desired loop bandwidth and phase margin.

By definition, the unity gain frequency of the FDC-PLL's loop gain,  $f_u$ , satisfies

$$\left| T \left( e^{j2\pi T_{ref} f_u} \right) \right|^2 = 1. \tag{44}$$

It can be verified from (12), (30), and (42) that

$$f_u \cong \frac{K_{DCO}}{2\pi} \sqrt{\frac{K}{2}} \sqrt{1 + \sqrt{1 + \frac{4K_I^2}{\left(K_{DCO}T_{ref}\right)^2 K^2}}}$$

(45)

where

$$K \triangleq K_P \left( K_P + K_I \right). \tag{46}$$

Typically,  $K_P \gg K_I$  in which case (45) reduces to

$$f_u \cong \frac{K_{DCO}K_P}{2\pi} \tag{47}$$

Furthermore,

$$\left| \frac{T\left(e^{j2\pi T_{ref}f_u}\right)}{1 + T\left(e^{j2\pi T_{ref}f_u}\right)} \right|^2 \left[ \frac{\sin\left(\pi T_{ref}f_u\right)}{\pi T_{ref}f_u} \right]^4 \cong \frac{1}{2}$$

(48)

given  $2\pi T_{ref} f_u \ll 1$ , so the FDC-PLL's loop bandwidth,  $f_{BW}$ , is approximately given by

$$f_{BW} \cong f_u \,. \tag{49}$$

The FDC-PLL's phase margin in radians is

$$PM = \pi + \angle T \left( e^{j2\pi T_{ref} f_u} \right). \tag{50}$$

With (12), (11), (30), (42), and (45), this can be written as

$$PM = \pi + \tan^{-1} \left( \frac{K_P \sin\left(2\pi T_{ref} f_u\right)}{K_I + K_P \left[1 - \cos\left(2\pi T_{ref} f_u\right)\right]} \right)$$

$$-2 \tan^{-1} \left( \frac{\sin\left(2\pi T_{ref} f_u\right)}{1 - \cos\left(2\pi T_{ref} f_u\right)} \right) - 4\pi T_{ref} f_u.$$

(51)

It follows from the above analysis that for fixed  $K_{DCO}$  and  $T_{ref}$  the loop band-

width depends primarily on  $K_P$  and for fixed  $K_{DCO}$ ,  $T_{ref}$ , and loop bandwidth the phase margin depends primarily on  $K_I$ . Therefore, it is straightforward to choose  $K_I$  and  $K_P$  using (47), (49), and (51) to achieve a desired loop bandwidth and phase margin provided (42) holds. Then, a trial and error process can be applied in which the  $\lambda_i$  values are reduced to improve phase noise suppression and  $K_I$  and  $K_P$  are increased to maintain the desired loop bandwidth and phase margin. The trial and error process is guided by plotting (37), (38), (39), and (41) at each iteration.

## V. DESIGN EXAMPLE

The design methodology described above has been applied to select the example FDC-PLL design parameters presented in Table I. This section applies the linearized model to calculate the example FDC-PLL's expected performance with realistic input noise levels, and compares the calculated performance to the performance predicated by computer simulation. The example was chosen because it is suitable for use as a carrier synthesizer for the widely-used GSM mobile handset standard and facilitates comparison with previously published TDC-based PLLs [7, 10].

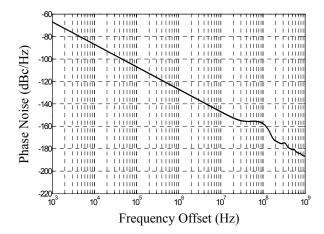

To apply the linearized model to calculate the FDC-PLL's output phase noise PSD, i.e., the PSD of  $\theta_{PLL}(t)$ , the PSDs of the input noise sources  $\theta_{DCO}(t)$ ,  $\theta_{ref}(t_n)$ , and  $e_p[n]$  must be known or estimated. In this example, the input noise sources are estimated to be in line with what can be achieved in a 65 nm CMOS process with a 1 V power supply. The simulated DCO is identical to that presented in [19], so  $\theta_{DCO}(t)$ , which includes both DCO quantization noise and analog noise, is taken to have a PSD

consistent with the results presented in [19] as shown in Figure 5. The  $\theta_{ref}(t_n)$  and  $e_p[n]$  input noise source levels were estimated via periodic steady-state (PSS) circuit simulations of transistor-level reference buffer, divider, PFD, and charge pump circuits.

PSS simulation of the reference buffer indicates that  $\theta_{ref}(t)$  can be modeled as white noise with a PSD level of -150 dBc/Hz. Therefore, the discrete-time PSD level of  $\theta_{ref}(t_n)$  is  $-150 - 10\log_{10}(T_{ref}) = -76$  dBc.

Simulations indicate that  $e_p[n]$  is dominated by the charge pump, which has the form of the single-ended design presented in [22]. The quantization step-size of the ADC is 80 mV. Its input voltage, and, therefore, the output voltage of the charge pump, ranges from 0.3 V to 0.7 V. The choices of C and  $I_{CP}$  are related via (10), and for this example design they are 1.25 pF and 359  $\mu$ A, respectively. Additionally,  $I_{OC} = -I_{CP}$  ( $I_{OC}$  is defined in the Appendix) and  $I_{OC} = 2$  ns. PSS simulations of the charge pump and offset current circuitry indicate that  $e_p[n]$  can be modeled as white noise with a discrete-time PSD level of -64 dBV.

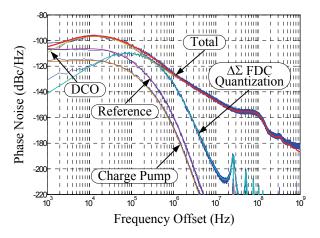

All the PSD plots in Figures 6 through 8 were obtained with the input noise source levels described above. The calculated PSD plots shown in the figures where obtained via (37), (38), (39), and (41). The simulated PSD plots shown in the figures where obtained via an event-driven C-language simulator. The simulator calculates the times of successive events, which include the positive-going zero crossings of  $v_{ref}(t)$ ,  $v_{div}(t)$ , and  $v_{out}(t)$ , the sample times of the 5-level ADC, and the desired output sample times of the  $\theta_{PLL}(t)$ . Each event time is calculated as a function of the FDC-

PLL's state variables, and the state variables are updated at each event time.

Figure 6 shows the simulated and calculated PSD of  $\theta_{PLL}(t)$  for several cases.<sup>†</sup> In one of the cases all of the noise sources presented above are considered together. In each of the other cases, only one of the noise sources is considered with all the other noise sources set to zero. Therefore, the figure shows how each noise source contributes to the total FDC-PLL output phase noise.

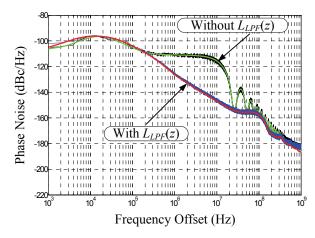

Figure 7 shows the simulated and calculated PSD of  $\theta_{PLL}(t)$  for two cases to demonstrate the effect of the  $L_{LPF}(z)$  portion of the FDC-PLL's loop filter. One case is that shown in Figure 6 for all the noise sources acting together. The other case differs only in that the simulation and calculations were made with  $L_{LPF}(z)$  effectively disabled by setting its  $\lambda_i$  coefficients to 1, and  $K_I$  and  $K_P$  adjusted to maintain approximately the same phase margin and bandwidth as the first case.

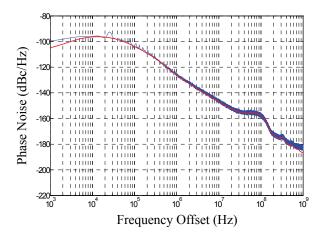

Figure 8 shows the effect of typical non-ideal circuit behavior. The smooth curve is the same calculated PSD of  $\theta_{PLL}(t)$  shown in Figure 6 for all the noise sources acting together. The jagged curve is the corresponding simulated PSD but with several non-ideal circuit effects taken into account in addition to noise. The non-ideal circuit effects involve the charge pump, offset current, sampling capacitor, and 5-level ADC. The magnitudes of the positive and negative charge pump current sources were increased and decreased, respectively, by 5%, and the offset current magnitude was decreased by 5%. A capacitor leakage current of -200 nA per reference period was introduced. Randomly chosen errors of 10 mV, -5 mV, 6 mV, and -8 mV, respec-

<sup>&</sup>lt;sup>†</sup>In each plot, the smooth curves represent the calculated PSDs, and the jagged curves represent simulated PSDs.

tively, were introduced into the ADC threshold voltages. The errors were made larger than would be expected in practice to demonstrate the robustness of the FDC-PLL architecture.

The simulated and calculated results presented in Figures 6 and 7 demonstrate that the linearized model accurately predicts the expected phase noise performance of the example FDC-PLL for the considered evaluation settings. Furthermore, the simulation results presented in Figure 8 suggest that the FDC-PLL is robust with respect to non-ideal circuit behavior. Numerous additional FDC-PLL design parameters and evaluation cases considered by the authors have yielded consistently positive results.

## VI. APPENDIX

This Appendix proves that the  $\Delta\Sigma$  FDC followed by the  $\alpha$  adder and accumulator in the digital loop controller perform the signal processing operations shown in Figure 3. It also applies known delta-sigma modulator results to draw various conclusions about the quantization noise introduced by the 5-level ADC.

The derivation consists of four parts. The first two parts derive expressions for the positive-going zero-crossing times of the reference oscillator and the divider output, respectively. The third part derives an expression for the voltage across the capacitor at the output of the charge pump. The fourth part combines the results of the previous parts to show that the ADC's quantization noise is that of a second-order delta-sigma modulator.

# A. Reference Oscillator Zero-Crossing Time Derivation

Recall that  $t_k$ , for k = 0, 1, 2, ..., are the times of consecutive positive-going zero-crossings of the reference oscillator signal,  $v_{ref}(t)$ . The phase in cycles of an oscillator at each of its positive-going zero crossings is integer-valued, so the definition of  $t_k$  implies that the phase of the reference oscillator at time  $t_k$  is

$$p_{ref}\left(t_{k}\right) = k\tag{52}$$

for all non-negative integers k.

Exactly one reference oscillator cycle occurs during the time interval  $t_{k-1} < t \le t_k$ , so it follows from (2) and (52) that

$$t_k - t_{k-1} = \frac{1 - \psi_{ref}[k]}{f_{ref}} \tag{53}$$

where

$$\psi_{ref}[k] = \theta_{ref}(t_k) - \theta_{ref}(t_{k-1}) \tag{54}$$

is the change in the reference oscillator's instantaneous phase noise in cycles between times  $t_{k-1}$  and  $t_k$ . Summing (53) from k = 1 through any positive integer n yields

$$t_n = t_0 + \frac{1}{f_{ref}} \sum_{k=1}^{n} \left( 1 - \psi_{ref}[k] \right). \tag{55}$$

## B. Divider Output Zero-Crossing Time Derivation

Recall that  $\tau_k$ , for each k = 0, 1, 2, ..., is the time of the positive-going zero-

<sup>&</sup>lt;sup>†</sup> Note that  $\psi_{ref}[n]$  is a different function than  $\psi_{ref}(t)$ , but they are related in that  $\psi_{ref}[n]$  is proportional to the average of  $\psi_{ref}(t)$  over the *n*th reference period. The functions  $\psi_{PLL}[n]$  and  $\psi_{PLL}(t)$  are similarly distinct.

crossing of the FDC-PLL's output signal,  $v_{out}(t)$ , that triggers the kth rising edge of the divider output,  $v_{div}(t)$ . Without loss of generality, assume that  $\tau_k$  is indexed such that

$$p_{PLL}\left(\tau_{0}\right) = 0. \tag{56}$$

The kth output value of the 5-level ADC, y[k], is a digitized sample of the charge pump capacitor voltage sampled after time  $\tau_k$ , but well before time  $\tau_{k+1}$ , and it follows from Figure 2 that

$$v[k] = 2y[k] - y[k-1]. (57)$$

Therefore, the kth sample of v[k] is available prior to time  $\tau_{k+1}$ . The divider modulus is immediately updated when the sample is available such that exactly N-v[k] DCO cycles occur during the time interval  $\tau_k < t \le \tau_{k+1}$ . The definition of  $\tau_k$  implies that

$$p_{PLL}(\tau_k) - p_{PLL}(\tau_{k-1}) = N - \nu[k-1]. \tag{58}$$

It follows from (5) and (58) that

$$\tau_{k} - \tau_{k-1} = \frac{N - \nu[k-1] - \psi_{PLL}[k]}{(N+\alpha)f_{ref}}$$

(59)

where

$$\psi_{PLL}[k] = \theta_{PLL}(\tau_k) - \theta_{PLL}(\tau_{k-1}) \tag{60}$$

is the change in the FDC-PLL's instantaneous output phase noise in cycles over the interval  $\tau_{k-1} < t \le \tau_k$ . Summing (59) from k = 1 through any positive integer n yields

$$\tau_{n} = \tau_{0} + \frac{1}{(N+\alpha)f_{ref}} \sum_{k=1}^{n} (N - v[k-1] - \psi_{PLL}[k]). \tag{61}$$

# C. Charge Pump Output Derivation

Subtracting (55) from (61) gives

$$\tau_{n} - t_{n} = \tau_{0} - t_{0} + \frac{1}{(N+\alpha) f_{ref}} \sum_{k=1}^{n} (x[k] - v[k-1])$$

(62)

where

$$x[k] = -\alpha - \psi_{PLL}[k] + (N + \alpha)\psi_{ref}[k]. \tag{63}$$

The  $-\alpha$  term in x[n] can be interpreted as the phase change in cycles over one reference period of an ideal oscillator of frequency  $Nf_{ref}$  minus that of the ideal output of the FDC-PLL. The definitions of  $\psi_{ref}[k]$  and  $\psi_{PLL}[k]$  imply that the average value of  $x[k]+\alpha$  is zero when the FDC-PLL is locked, and that  $(x[k]+\alpha)/T_{ref}$  is a measure of the average over the kth reference period of the difference between  $(N+\alpha)$  times the instantaneous frequency of the reference oscillator and the instantaneous frequency of the output signal.

It follows from (5) and (56) that

$$\tau_0 - t_0 = -\frac{\theta_{PLL}(\tau_0)}{(N+\alpha)f_{ref}}.$$

(64)

Substituting (57) and (64) into (62) gives

$$(\tau_{n} - t_{n})(N + \alpha) f_{ref} = -y[n-1] + \sum_{k=1}^{n} (x[k] - y[k-1]) + y[-1] - \theta_{PLL}(\tau_{0}).$$

(65)

Suppose the FDC-PLL is locked for all  $t \ge t_0$  so that

$$\left|\tau_{n} - t_{n}\right| < T_{ref} \tag{66}$$

for all  $n \ge 0$ , where  $T_{ref} = 1/f_{ref}$  is the nominal period of the reference oscillator. If the PFD and charge pump are as shown in Figure 1, then in the absence of non-ideal circuit behavior the output of the charge pump is a sequence of current pulses given by

$$i_{cp}(t) = \begin{cases} I_{CP} & \text{when } t_n \le t \le \tau_n \\ -I_{CP} & \text{when } \tau_n \le t \le t_n \\ 0 & \text{otherwise} \end{cases}$$

(67)

for all positive integers n. An additional current pulse of fixed duration and fixed (positive or negative) amplitude may also be included in  $i_{cp}(t)$  each reference period to reduce nonlinear distortion introduced by the PFD and charge pump [23], [24].

The ADC samples the capacitor voltage each reference period shortly after the charge pump current sources settle to zero. Let  $V_c[n]$  be the voltage sampled by the ADC during the nth reference period minus the midscale voltage of the ADC (i.e.,  $V_c[n] = 0$  corresponds to the middle of the ADC's input range). The operation of the charge pump implies that

$$V_{c}[n] = V_{c}[n-1] + \left(\tau_{n} - t_{n}\right) \frac{I_{CP}}{C} + T_{OC} \frac{I_{OC}}{C} + e_{p}[n]$$

(68)

where  $T_{OC}$  and  $I_{OC}$  are the duration and amplitude, respectively, of the additional current pulse if it is used (otherwise  $I_{OC} = 0$ ), and  $e_p[n]$  represents the combined error from noise and other non-ideal circuit behavior in the charge pump, PFD, and divider. Each sample of  $e_p[n]$  is the result of error in the amount of charge in the current pulses integrated onto the capacitor during the nth reference period.

Substituting (10) and (65) into (68) results in

$$\frac{V_{c}[n]}{\Delta} = \frac{V_{c}[n-1]}{\Delta} - y[n-1] + \sum_{k=1}^{n} (x[k] - y[k-1])

+ y[-1] - \theta_{PLL}(\tau_{0}) + \theta_{offset} + \frac{e_{p}[n]}{\Delta}$$

(69)

where

$$\theta_{offset} = T_{OC} \frac{I_{OC}}{C\Lambda} \,. \tag{70}$$

## D. Delta-Sigma Modulator Equivalence and Implications

The output of the ADC, y[n], can take on values from the set  $\{-2, -1, 0, 1, 2\}$  and can be written as

$$y[n] = \frac{1}{\Lambda} V_c[n] + e_{ADC}[n] \tag{71}$$

where  $e_{ADC}[n]$  is the sum of quantization noise and any additional error from non-ideal circuit behavior in the ADC. The ADC has only five levels, so its quantization is very coarse. Therefore, it is assumed that the only non-negligible component of  $e_{ADC}[n]$  is quantization noise, so the *n*th output sample of the ADC is taken to be  $V_c[n]/\Delta$  rounded to the nearest integer when

$$-2.5\Delta \le V_c[n] \le 2.5\Delta \,, \tag{72}$$

and -2 or 2, respectively, when  $V_c[n]$  is less than  $-2.5\Delta$  or greater than  $2.5\Delta$ .

Equations (69) and (71) are equivalent to the block diagram shown in Figure 3 to the left of the  $\alpha$  adder for n = 1, 2, 3, ..., where

$$u_2[n] = \frac{V_c[n]}{\Lambda} \tag{73}$$

and the initial condition on  $u_1[n]$  is

$$u_1[0] = y[-1] - \theta_{PLL}(\tau_0) + \theta_{offset}.$$

(74)

The block diagram has the well-known form of a second-order delta-sigma modulator, so its output can be written as

$$y[n] = x[n] + \frac{e_p[n] - e_p[n-1]}{\Lambda} + e_{\Delta \Sigma 2}[n]$$

(75)

where

$$e_{\Delta\Sigma^2}[n] = e_{ADC}[n] - 2e_{ADC}[n-1] + e_{ADC}[n-2]$$

(76)

is second-order highpass shaped quantization noise [25, 26].

If (72) is satisfied for a given integer n, then  $e_{ADC}[n]$  is the quantization noise caused by rounding  $u_2[n]$  to the nearest integer. In this case the delta-sigma modulator is said to be non-overloading at time n. Otherwise, the delta-sigma modulator is said to be overloaded at time n. If the delta-sigma modulator is non-overloading for all n = 1, 2, 3, ..., then  $e_{ADC}[n]$  is asymptotically white and uniformly distributed between -0.5 and 0.5 under the realistic assumption that x[n] contains a small amount of independent random noise [27]. In contrast, if the delta-sigma modulator becomes overloaded, then  $e_{ADC}[n]$  becomes correlated with x[n], its variance increases, and it often contains spurious tones. Hence, for best phase noise performance it is desirable to keep the delta-sigma modulator non-overloading once the FDC-PLL is locked.

Sufficient conditions for the delta-sigma modulator to be non-overloading for n = 1, 2, 3, ... are that it is non-overloading for n = 1 and n = 2, and

$$\left| x[n] + \frac{e_p[n] - e_p[n-1]}{\Delta} \right| \le 1 \tag{77}$$

for n = 3, 4, 5, ... The proof of this result is as follows. It can be verified from Figure 3 that

$$u_{2}[k] = x[k] + \frac{e_{p}[k] - e_{p}[k-1]}{\Delta}$$

$$-2e_{ADC}[k-1] + e_{ADC}[k-2]$$

(78)

If the delta-sigma modulator is non-overloading for n = k - 1 and n = k - 2, then  $e_{ADC}[k-1]$  and  $e_{ADC}[k-2]$  are each bounded in magnitude by 0.5, so (73) and (78) imply that

$$|V_c[k]| \le \left( \left| x[k] + \frac{e_p[k] - e_p[k-1]}{\Delta} \right| + 1.5 \right) \Delta.$$

(79)

This implies that (72) is satisfied and therefore that the delta-sigma modulator is non-overloading for n = k provided (77) holds for n = k. The result follows from induction.

It follows from (63) that (77) is satisfied for any  $\alpha$  in the range given by (9) if

$$\left| \frac{e_p[n] - e_p[n-1]}{\Delta} - \psi_{PLL}[n] + (N + \alpha) \psi_{ref}[n] \right| \le \frac{1}{2}. \tag{80}$$

Frequency synthesizers usually are designed to have low phase noise, so the left side of (80) is expected to be far less than  $\frac{1}{2}$  in practice. Furthermore, in most practical cases the magnitude of  $\alpha$  is much larger than the left side of (80). In such cases it can be verified that only four of the five ADC levels are exercised once the FDC-PLL is locked. Thus, the five ADC levels are easily sufficient to ensure that the delta-sigma modulator remains non-overloading once the FDC-PLL is locked, which also ensures that  $e_{ADC}[n]$  does not contain spurious tones induced by quantizer overloading.

Nevertheless, it can be verified from well-known delta-sigma modulator prop-

erties, that when the magnitude of  $\alpha$  is 0.5, four ADC levels would only be sufficient to ensure that the delta-sigma modulator remains non-overloading in the absence of any noise other than quantization noise. Therefore, in practice five ADC levels are necessary to avoid overloading for values of  $\alpha$  with magnitudes close to 0.5.

Substituting (63) into (75) gives

$$y[n] + \alpha = -\psi_{PLL}[n] + (N + \alpha)\psi_{ref}[n] + \frac{e_p[n] - e_p[n-1]}{\Lambda} + e_{\Delta\Sigma 2}[n].$$

(81)

This sequence is accumulated prior to the loop filter, so the input to the loop filter can be written as (14) neglecting a possible offset that depends on the initial value of the accumulator output.