### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Enabling Techniques for Wide Bandwidth Fractional-N Phase Locked Loops

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in Electrical and Computer Engineering (Electronic Circuits and Systems)

by

Sudhakar Pamarti

### Committee in charge:

Professor Ian Galton, Chair Professor Peter Asbeck Professor Bhaskar Rao Professor Robert Bitmead Professor Patrick Fitzsimmons

2003

UMI Number: 3091331

### UMI Microform 3091331

Copyright 2003 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Copyright Sudhakar Pamarti, 2003 All rights reserved. To my sister

# TABLE OF CONTENTS

|    | Signature page                                                             | iii        |

|----|----------------------------------------------------------------------------|------------|

|    | Dedication                                                                 | iv         |

|    | Table of contents                                                          | . <b>v</b> |

|    | List of figures                                                            | vi         |

|    | List of tables                                                             | ix.        |

|    | Acknowledgements                                                           | . X        |

|    | Vita and Publications                                                      | . xi       |

|    | Abstract of the dissertation                                               | . xii      |

| 1. | A wideband 2.4 GHz delta-sigma fractional-N PLL with 1 Mb/s in-loop        |            |

|    | modulation                                                                 | 1          |

| 2. | Phase noise cancellation design tradeoffs in delta-sigma fractional-N PLLs | 38         |

| 3. | One-bit dithering in digital delta-sigma modulators                        | 75         |

# LIST OF FIGURES

## CHAPTER 1

| Fig. 1.1: High-level functional diagram of the implemented $\Delta\Sigma$ fractional-N PLL 3                                  |

|-------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2: The "core" of a typical fractional-N PLL                                                                            |

| Fig. 1.3: Illustration of increase of the useable PLL bandwidth due to phase noise cancellation                               |

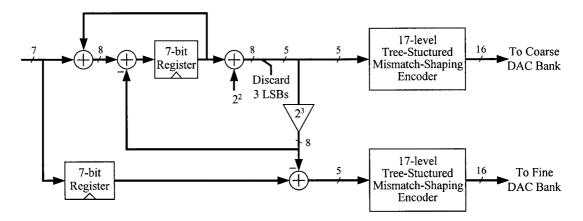

| Fig. 1.4: Details of employed digital $\Delta\Sigma$ modulators                                                               |

| Fig. 1.5: Details of the mismatch-shaping digital encoder                                                                     |

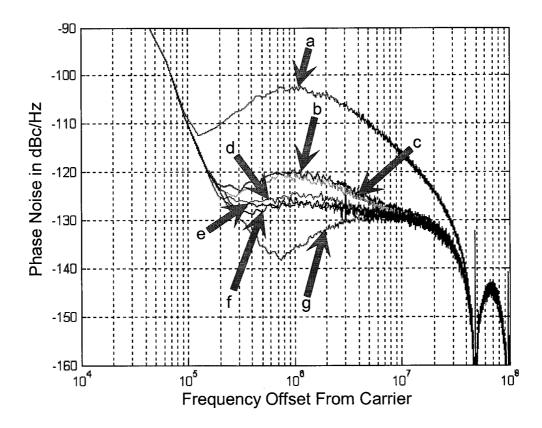

| Fig. 1.6: Simulated output phase noise PSD plots of the implemented PLL15                                                     |

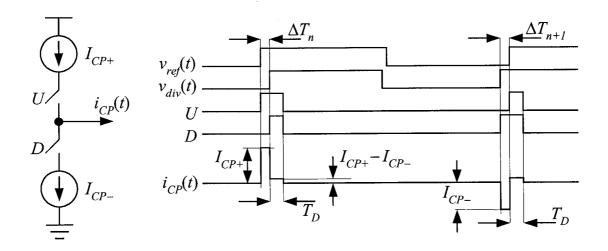

| Fig. 1.7: A conventional charge pump and the associated timing diagram16                                                      |

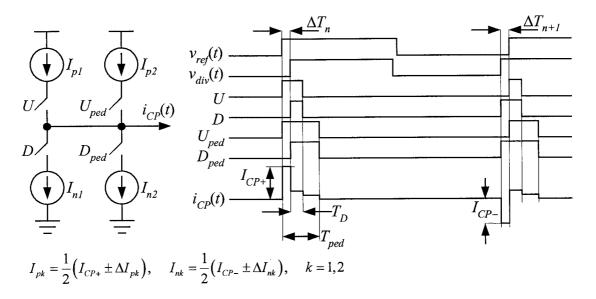

| Fig. 1.8: The modified charge pump and the associated timing diagram                                                          |

| Fig. 1.9: The frequency divider circuit.                                                                                      |

| Fig. 1.10: The modified PFD circuit                                                                                           |

| Fig. 1.11: The modified charge pump circuit                                                                                   |

| Fig. 1.12: The DAC pulse generator and the <i>k</i> th coarse 1-bit current pulse DAC circuits                                |

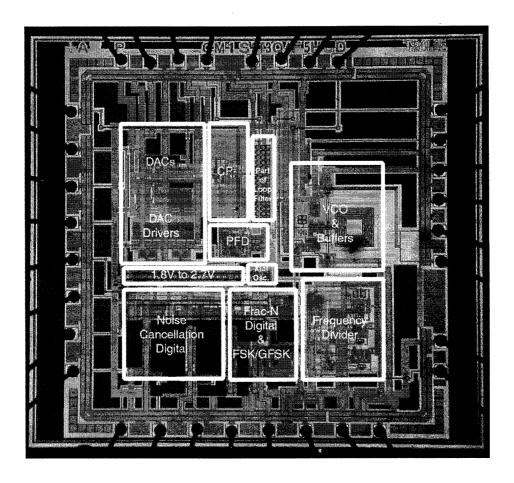

| Fig. 1.13: Die photograph                                                                                                     |

| Fig. 1.14: Measured PSD plots of the output signal and phase noise of the PLL tuned to 2.431 GHz without modulation           |

| Fig. 1.15: Measured PSD plot of the output signal of the PLL tuned to 2.431 GHz with 1 Mb/s FSK modulation                    |

| Fig. 1.16: Measured eye pattern corresponding to the output signal shown in Fig. 1.17.                                        |

| Fig. 1.17: Measured PSD plots of the PLL tuned to 2.453 GHz with the charge pump linearization technique enabled and disabled |

# CHAPTER 2

| Fig. 2.1: A high level functional diagram of the presented $\Delta\Sigma$ fractional-N PLL39                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.2: A model for the cancellation technique including a gain error in the cancellation path                                                                                                          |

| Fig. 2.3: Illustration of bandwidth extension made possible by the phase noise cancellation technique                                                                                                     |

| Fig. 2.4: Mechanism of imperfect phase noise cancellation                                                                                                                                                 |

| Fig. 2.5: A model for the cancellation technique including the effect of finite DAC pulse width                                                                                                           |

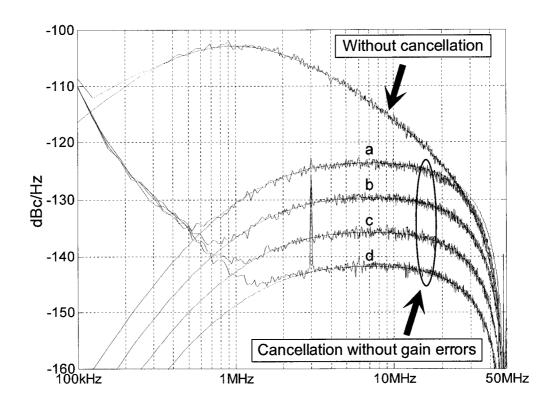

| Fig. 2.6: Predicted and simulated phase noise PSD for the cancellation technique for DAC pulses of duration (a) 32 (b) 16 (c) 8 and (d) 4 VCO periods                                                     |

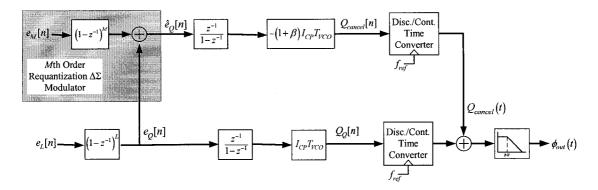

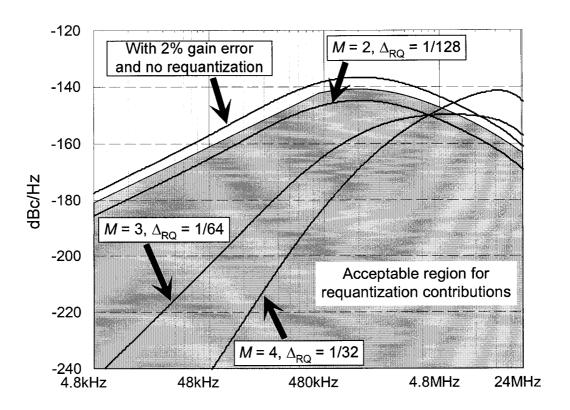

| Fig. 2.7: A model for the cancellation technique including the requantization $\Delta\Sigma$ modulator                                                                                                    |

| Fig. 2.8: Illustration of the effects of requantization on the phase noise of the PLL output                                                                                                              |

| Fig. 2.9: A model for the cancellation technique including the segmentation of the DAC                                                                                                                    |

| Fig. 2.10: A model of the cancellation technique including dither                                                                                                                                         |

| CHAPTER 3                                                                                                                                                                                                 |

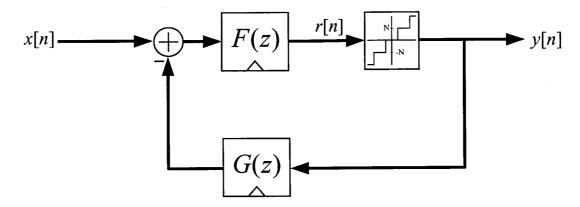

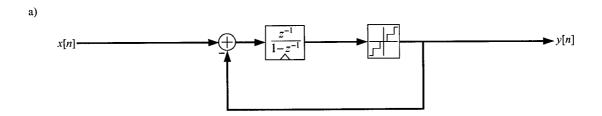

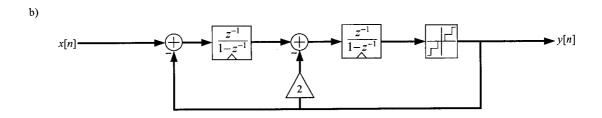

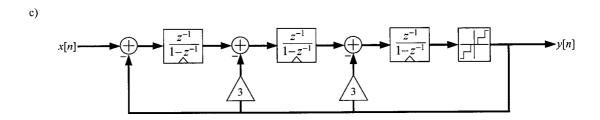

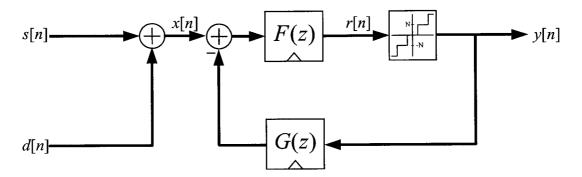

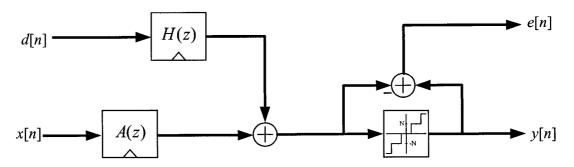

| Fig. 3.1: A generic single stage digital $\Delta\Sigma$ modulator                                                                                                                                         |

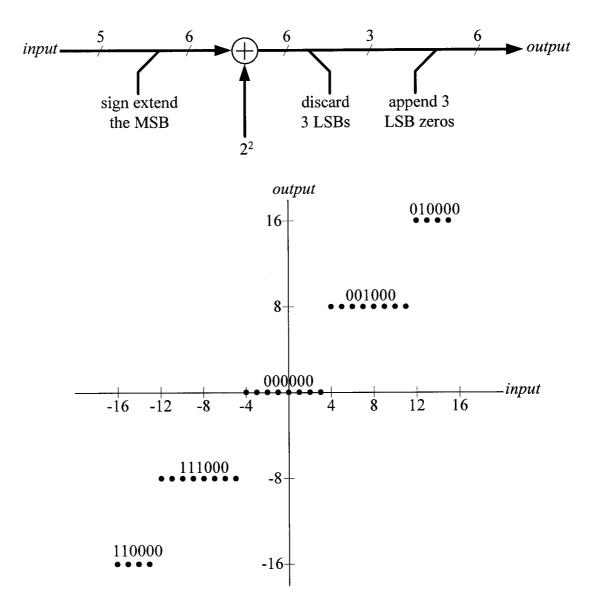

| Fig. 3.2: Sample mid-tread requantization of a binary, 2's complement sequence 78                                                                                                                         |

| Fig. 3.3: Example digital $\Delta\Sigma$ modulators – (a) The first-order $\Delta\Sigma$ modulator (b) The second-order dual-loop $\Delta\Sigma$ modulator (c) The third-order $\Delta\Sigma$ modulator79 |

| Fig. 3.4: A generic dithered digital $\Delta\Sigma$ modulator.                                                                                                                                            |

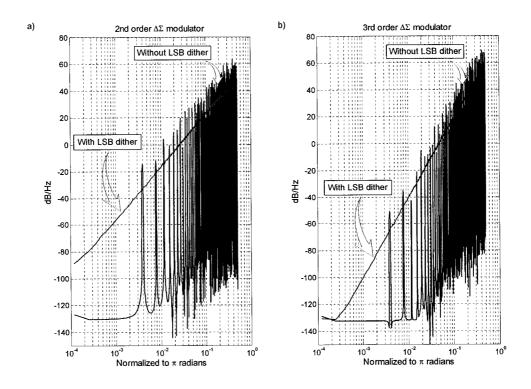

| Fig. 3.5: Elimination of spurious tones using one-bit dither in digital $\Delta\Sigma$ modulators.84                                                                                                      |

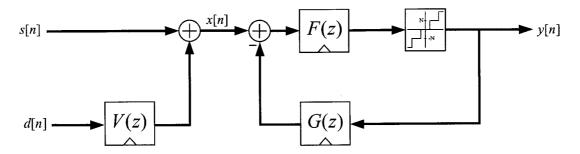

| Fig. 3.6: A scheme to introduce shaped dither into the generic $\Delta\Sigma$ modulator94                                                                                                                 |

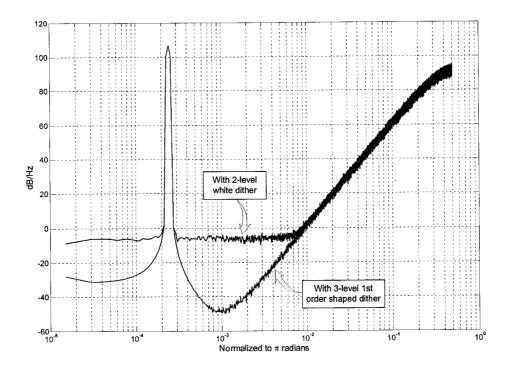

| Fig. 3.7: Illustration of increase of the in-band SNR using shaped dither     | 95  |

|-------------------------------------------------------------------------------|-----|

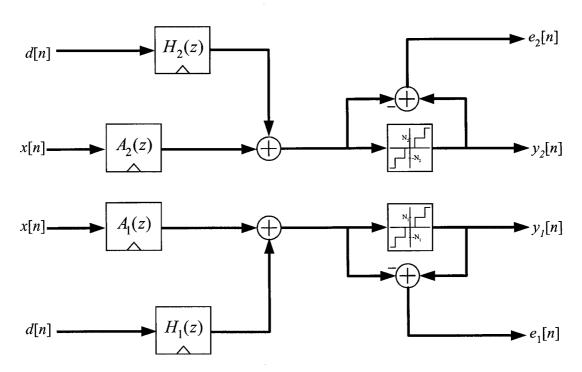

| Fig. 3.8: An example 2-1-1 MASH $\Delta\Sigma$ modulator.                     | 99  |

| Fig. 3.9: A generic MASH $\Delta\Sigma$ modulator with $K$ stages.            | 101 |

| Fig. 3.10: Framework for the theoretical analysis of dithered quantization    | 107 |

| Fig. 3.11: Framework for the theoretical analysis of multi-stage dithered qua |     |

# LIST OF TABLES

# CHAPTER 1

| Table 1.1: Simulated phase noise contributions of the various circuit block relevant PLL parameters. |     |

|------------------------------------------------------------------------------------------------------|-----|

| Table 1.2: Performance summary.                                                                      | 28  |

| CHAPTER 2                                                                                            |     |

| CHAPTER 3                                                                                            |     |

| Table 3.1: Details of the example $\Delta\Sigma$ modulators in Fig. 3.3                              | 80  |

| Table 3.2: Guidelines for dithering common digital $\Delta\Sigma$ modulators                         | 104 |

### **ACKNOWLEDGEMENTS**

Foremost, I am thankful to my advisor, Ian Galton, for his support and encouragement through out my graduate student years. I am particularly grateful for any sense of professional discipline that I might have cultivated under his guidance. I am thankful to Professors Peter Asbeck, Bhaskar Rao, Robert Bitmead, and Patrick Fitzsimmons who kindly agreed to serve on my doctoral committee, and Karol Provite, Carolyn Kuttner and Renee Gramlich for their support with the various administrative matters concerning graduate students. I am also grateful to Lars Jansson for his invaluable help and advice with my research.

I am thankful to Jim Thomas, Ian's family, and the past and the present members of Ian's research group — Henrik Jensen, Eric Fogleman, Bill Huff, Jared Welz, Sheng Ye, Eric Siragusa, Asaf Fishov, Alan Lewis, Ashok Swaminathan, Erica J. Poole, and Andrea Panigada — for making me feel welcome, and perfectly at home in San Diego. I am particularly grateful to Jared for our numerous and engrossing discussions about practically everything under the sun. These discussions have had a significant influence on my outlook, technical and otherwise, in more ways than he knows. I am also grateful to Eric Siragusa, Ashok Swaminathan, and Mani Vaidyanathan for curing me of my layout blues by introducing me to the wonderful world of Torrey Pines.

Above all, I am indebted to my dear sister, Lavanya, and my parents, Venkata Subba Rao and Sita Devi Pamarti, for their loving support and encouragement for every endeavor of mine.

### **VITA**

| May 14, 1974 | Born, Hyderabad, India                                                                                                 |

|--------------|------------------------------------------------------------------------------------------------------------------------|

| 1995         | B.Tech., Indian Institute of Technology, Kharagpur                                                                     |

| 1995-1997    | Hughes Software Systems, New Delhi                                                                                     |

| 1997-2003    | Graduate Student Researcher, Department of Electrical and<br>Computer Engineering, University of California, San Diego |

| 2003         | Ph.D., University of California, San Diego                                                                             |

### **PUBLICATIONS**

<sup>&</sup>quot;A Wideband 2.4 GHz Delta-Sigma Fractional-N PLL With 1 Mb/s In-Loop Modulation," IEEE Journal of Solid State Circuits, accepted for publication.

<sup>&</sup>quot;Phase Noise Cancellation Design Tradeoffs in Delta-Sigma Fractional-N PLLs," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, under review.

<sup>&</sup>quot;One-bit Dithering in Single Stage Digital Delta-Sigma Modulators," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, in preparation.

<sup>&</sup>quot;One-bit Dithering in Multi-stage Delta-Sigma Modulator Based Digital-Analog Conversion," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, in preparation.

### ABSTRACT OF THE DISSERTATION

Enabling Techniques for Wide Bandwidth Delta-Sigma Fractional-N Phase

Locked Loops

by

### Sudhakar Pamarti

Doctor of Philosophy in Electrical and Computer Engineering

(Electronic Circuits and Systems)

University of California, San Diego, 2003

Professor Ian Galton, Chair

Delta-sigma fractional-*N* phase locked loops are widely used for frequency synthesis in electronic communication systems. A wide bandwidth makes it possible for the delta-sigma fractional-*N* phase locked loop to perform digitally-controlled frequency modulation at high bit-rates, thereby simplifying transceiver circuitry. Wide bandwidth delta-sigma fractional-*N* phase locked loops offer a multitude of other benefits that contribute to lower costs and a reduced power consumption in the electronic communication products which use these phase locked loops. In spite of the benefits, wide bandwidth delta-sigma fractional-*N* phase locked loops have not gained general acceptance because of their poor phase noise and spurious tone performance, particularly when they are implemented in integrated circuit (IC) form.

xii

This dissertation presents two signal processing techniques – a phase noise cancellation technique and a charge pump linearization technique – that significantly reduce phase noise and spurious tones in a wide bandwidth delta-sigma fractional-N phase locked loop. Chapter 1 presents a prototype CMOS IC that demonstrates the efficacy of the two techniques – reduction of the phase noise by at least 16 dB, and reduction of spurious tones by at least 8 dB – in a 2.4 GHz delta-sigma fractional-N phase locked loop with 460 kHz wide bandwidth. Chapter 2 presents a theoretical basis for the phase noise cancellation technique and suggests design guidelines to tailor the technique to meet the target requirements of a general wide bandwidth deltasigma fractional-N phase locked loop. The effectiveness of the phase noise cancellation technique hinges on eliminating limit cycles in the digital delta-sigma modulators, which the technique employs. Chapter 3 presents conditions to theoretically guarantee that one-bit dither eliminates limit cycles in a large class of digital delta-sigma modulators. It also extends the theory to suppress spurious tones in a large class of delta-sigma modulator based digital-to-analog conversion systems.

# A Wideband 2.4 GHz Delta-Sigma Fractional-N PLL With 1 Mb/s In-Loop Modulation

Sudhakar Pamarti, Lars Jansson, and Ian Galton

Abstract—A phase noise cancellation technique and a charge pump linearization technique, both of which are insensitive to component errors, are presented and demonstrated as enabling components in a wideband CMOS  $\Delta\Sigma$  fractional-N PLL. The PLL has a loop bandwidth of 460 kHz and is capable of 1 Mb/s in-loop FSK modulation at center frequencies of 2402 + k MHz for k = 0, 1, 2, ...78. For each frequency, measured results indicate that the peak spot phase noise reduction achieved by the phase noise cancellation technique is 16 dB or better, and the minimum suppression of factional spurious tones achieved by the charge pump linearization technique is 8 dB or better. With both techniques enabled, the PLL achieves a worst-case phase noise of -121 dBc/Hz at 3 MHz offsets, and a worst-case in-band noise floor of -96 dBc/Hz. The PLL circuitry consumes 34.4 mA from 1.8–2.2V supplies. The IC is realized in a 0.18  $\mu$ m mixed-signal CMOS process, and has a die size of 2.72mm × 2.47mm.

## I. INTRODUCTION

This paper presents a phase noise cancellation technique that relaxes the fundamental tradeoff between phase noise and bandwidth in conventional delta-sigma  $(\Delta\Sigma)$  fractional-N phase-locked loops (PLLs), and a charge pump linearization technique that improves the spurious performance of wideband fractional-N PLLs. Together, the techniques make it practical to significantly increase the bandwidth of  $\Delta\Sigma$  fractional-N PLLs without degrading phase noise and spurious performance. They are demonstrated in a CMOS  $\Delta\Sigma$  fractional-N PLL that can be configured as a Bluetooth-

compliant wireless LAN transmitter and a local oscillator for a direct-conversion Bluetooth-compliant receiver. The techniques enable the PLL to achieve the required phase noise and spurious performance specifications with a bandwidth of 460 kHz, which is sufficiently wide to allow in-loop modulation of the required 1 Mb/s transmit signal. Moreover, the wide bandwidth significantly reduces the susceptibility of the voltage-controlled oscillator (VCO) to pulling, and causes the PLL phase noise arising from 1/f noise and  $1/f^3$  noise in the VCO to be largely attenuated [1, 2]. Unlike other methods of in-loop modulation for wireless transmitters, the phase noise cancellation technique is not sensitive to analog component errors, does not require calibration, and does not require a Type-1 PLL and the associated phase detector complications [3, 4, 5, 6, 7]. The benefit of the charge pump linearization technique is that it does not require dynamic bias adjustment so its bandwidth is not limited by an analog feedback circuit [8]. Although the two techniques complement each other in that they both enhance performance in wideband  $\Delta\Sigma$  fractional-N PLLs, they are independent and each can be applied in the absence of the other.

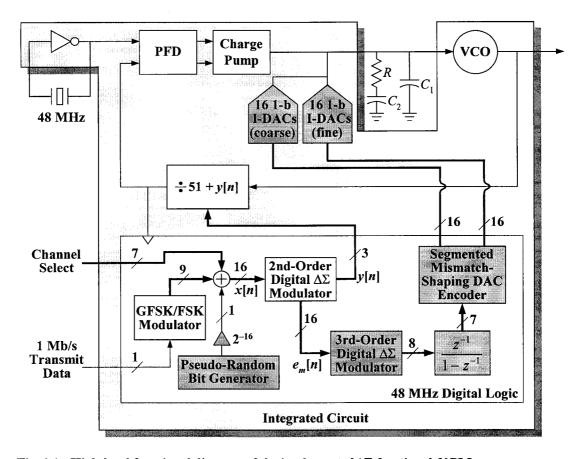

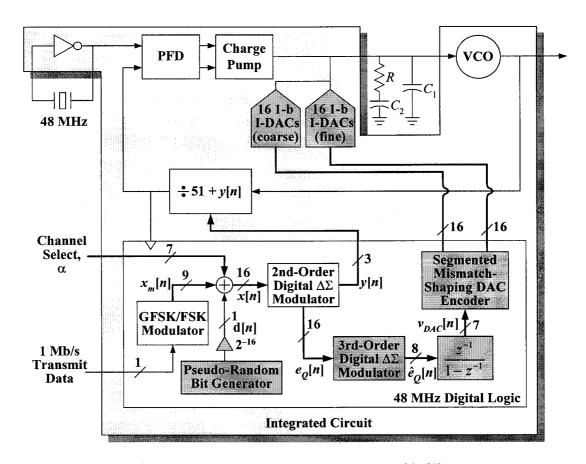

Fig. 1.1: High-level functional diagram of the implemented  $\Delta\Sigma$  fractional-N PLL.

A high-level block diagram of the implemented PLL is shown in Fig. 1.1. It differs from a conventional  $\Delta\Sigma$  fractional-N PLL in that the dark gray blocks have been added to implement the phase noise cancellation technique, and the charge pump and phase-frequency detector (PFD) blocks have been modified from their conventional forms to implement the charge pump linearization technique. The details of the PLL are described throughout the remainder of the paper. Sections II and III describe the signal processing details of the phase noise cancellation technique and the charge pump linearization technique, respectively. Section IV presents circuit details, and Section V presents measurement results.

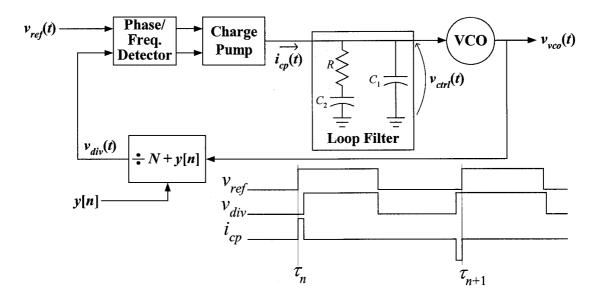

Fig. 1.2: The "core" of a typical fractional-N PLL.

## II. THE PHASE NOISE CANCELLATION TECHNIQUE

### A. Problems with Conventional Fractional-NPLLs

The core of a typical fractional-N PLL is shown in Fig. 1.2. It consists of a PFD, a charge pump, a loop filter, a VCO, and a frequency divider. The divider output,  $v_{div}(t)$ , is a two level signal in which the nth and (n+1)th rising edges are separated by N + y[n] periods of the VCO output, for n = 1, 2, 3, ..., where N is a constant integer, and y[n] is a sequence of integers generated by digital logic not shown in the figure. As indicated in the figure for the case where the PLL is locked, if the nth rising edge of the reference signal,  $v_{ref}(t)$ , occurs before that of  $v_{div}(t)$ , the charge pump generates a current pulse of nominal amplitude  $I_{CP}$  and a duration equal to the time difference between the two edges. Otherwise, the situation is similar except the polarity of the current pulse is reversed.

If y[n] could be set to any desired value between -1 and 1, say  $\alpha$ , then the output frequency of the PLL would settle to  $(N+\alpha)$   $f_{ref}$ , so it would be possible to achieve any output frequency between (N-1)  $f_{ref}$  and (N+1)  $f_{ref}$ . Unfortunately, y[n] is restricted to integer values because the divider simply counts rising VCO edges. However, y[n] can be a sequence of integer values that average to  $\alpha$ . Such a sequence can be written as  $y[n] = \alpha + e_m[n]$ , where  $e_m[n]$  is zero-mean quantization noise caused by using integer values in place of the ideal fractional value. In this case, the PLL output frequency settles to  $(N+\alpha)$   $f_{ref}$  as desired, although a price is paid in terms of added phase noise.

As shown in [9], in terms of the effect it has on the PLL phase noise, the quantization noise can be modeled as a sequence of additive charge samples,  $Q_{e_m}[n]$ , that get injected into the loop filter once every reference period. Neglecting a constant offset associated with the initial conditions of the loop filter, it can be shown that  $Q_{e_m}[n]$  is well modeled as

$$Q_{e_m}[n] = T_{VCO} I_{CP} \sum_{k=n_0}^{n-1} e_m[k],$$

(1)

where  $T_{VCO}$  is the period of the VCO output, and  $n_0 < n$  is an arbitrary initial time index. The PLL acts on this sequence as a lowpass filter in the process of converting it to output phase noise. Therefore, spectral components of  $e_m[n]$  outside the bandwidth of the PLL are suppressed, but those inside the bandwidth of the PLL are amplified through the discrete-time integration in (1) and can add significantly to the overall phase noise of the PLL.

In early fractional-N PLLs the problem of suppressing the PLL phase noise that would otherwise result from  $e_m[n]$  has been addressed using a DAC cancellation path to suppress  $Q_{e_m}[n]$  [10, 11]. Because y[n] is generated digitally,  $-Q_{e_m}[n]$  can be calculated by digital circuitry, converted by a DAC to an analog current, and added to the output of the charge pump. If the DAC has sufficient precision and the correct gain, the added signal nearly cancels the component of the charge pump output corresponding to  $Q_{e_m}[n]$ . In most fractional-N PLLs of this type, y[n] is generated using one or two digital error-accumulator structures designed to ensure that the sum of  $e_m[n]$  in (1) is bounded. The resulting  $Q_{e_m}[n]$  sequence tends to have a large dynamic range, a high spurious tone content, and significant spectral power within the PLL bandwidth. Therefore, excellent cancellation accuracy is required; if  $Q_{e_m}[n]$  is only partially cancelled because of gain errors, distortion, or insufficient dynamic range in the DAC cancellation path, the remaining portion of  $Q_{e_m}[n]$  contains in-band noise and spurious tones which can contribute significant phase noise [12, 13]. Consequently, the approach has been used mainly in high-cost applications such as test and measurement equipment wherein component trimming and calibration are practical.

A more recent technique that circumvents the DAC precision and gain matching problems uses a digital  $\Delta\Sigma$  modulator with at least second-order quantization noise shaping to generate y[n] such that  $Q_{e_m}[n]$  has at least one zero at dc with most of its power concentrated at high frequencies, outside the passband of the PLL [14, 15,

16]. Provided the bandwidth of the PLL is sufficiently narrow, most of the quantization noise is suppressed by the PLL so a DAC cancellation path is not necessary. Such PLLs have come to be known as  $\Delta\Sigma$  fractional-N PLLs, and have become widely used in consumer-oriented communication devices over the last decade. Nevertheless, the need to suppress out-of-band quantization noise imposes a fundamental bandwidth versus phase noise tradeoff in  $\Delta\Sigma$  fractional-N PLLs that causes problems in many applications.

One such problem is *VCO pulling*. For example, when a narrowband PLL is used to provide the RF local oscillator for a direct conversion transmitter, even a small amount of parasitic coupling of the transmitted signal to the VCO circuitry tends to corrupt or *pull* the VCO output which, in turn, causes the up-converted transmit signal to be distorted. However, if the bandwidth of the PLL is at least comparable to the modulation bandwidth, the PLL is much less susceptible to this problem because the feedback within the PLL tends to fight the corrupting effects of the modulated transmit signal.

Another problem with narrowband fractional-N PLLs is that they often preclude in-loop VCO modulation for direct synthesis of frequency modulated transmit signals. In principle such signals can be generated directly by a  $\Delta\Sigma$  fractional-N PLL thereby eliminating the need for conventional upconversion stages and much of the attendant analog circuitry. Specifically, if  $\alpha$  in the discussion above is replaced by  $\alpha + x_m[n]$ , where  $x_m[n]$  is a zero-mean modulation sequence, the resulting PLL output has a center frequency of  $(N + \alpha)$   $f_{ref}$  but is frequency modulated by a lowpass filtered version of  $x_m[n]f_{ref}$ . The PLL must have a sufficiently narrow bandwidth to suppress

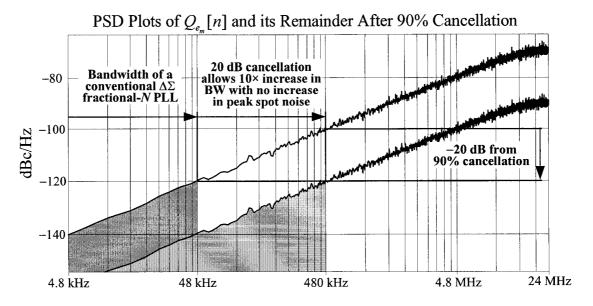

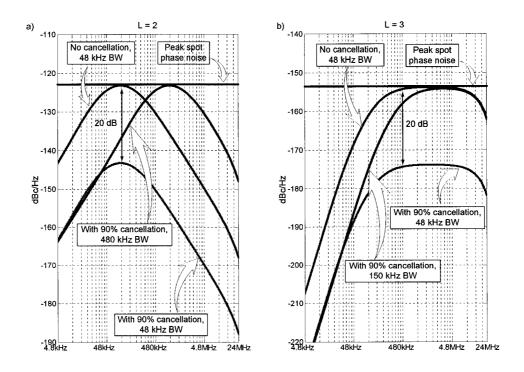

Fig. 1.3: Illustration of increase of the useable PLL bandwidth due to phase noise cancellation.

the phase noise, yet must have a sufficiently wide bandwidth to accommodate the VCO modulation. In many applications, such as the Bluetooth transmitter application used as a demonstration vehicle in this work, it is not possible to simultaneously satisfy both of these requirements using conventional techniques.

## B. Phase Noise Cancellation Technique Overview

As shown in Fig. 1.1, the phase noise cancellation technique combines the two fractional-N PLL approaches described above. A second-order digital  $\Delta\Sigma$  modulator generates y[n] as in a conventional  $\Delta\Sigma$  fractional-N PLL, and a DAC cancellation path attenuates  $Q_{e_m}[n]$ . As explained below, the combination of the two approaches in conjunction with quantization noise-shaping, mismatch noise-shaping, and 1-bit dither, greatly reduces the respective limitations suffered by each approach in isolation.

Fig. 1.3 illustrates that combining the two approaches makes it possible to

widen the PLL bandwidth relative to that of a conventional  $\Delta\Sigma$  fractional-N PLL without increasing the peak spot phase noise. The top curve in the figure represents a power spectral density (PSD) plot of  $Q_{e_m}[n]$  scaled by the dc value of the PLL phase transfer function between  $\mathcal{Q}_{e_m}[n]$  and the PLL output, so its units are dBc/Hz referred to the PLL output. The bottom curve represents the PSD, also in units of dBc/Hz referred to the PLL output, of the portion of  $Q_{e_m}[n]$  that remains after cancellation where the DAC cancellation path has a 10% gain error but is otherwise ideal. Suppose, as an example, that the peak spot phase noise resulting from quantization noise is to be limited to -120 dBc/Hz. Without the DAC cancellation path, i.e., in the case of a conventional  $\Delta\Sigma$  fractional-N PLL, it can be seen from the top curve in the figure that the bandwidth of the PLL would have to be limited to 48 kHz. In contrast, it can be seen from the bottom curve in the figure that with the DAC cancellation path the bandwidth of the PLL can be set to 480 kHz. Thus, even with a 10% gain error in the DAC cancellation path, the bandwidth of the PLL can be increased by a factor of 10 without increasing the peak spot phase noise of the PLL.

While combining the two fractional-N PLL approaches relaxes both the bandwidth versus phase noise tradeoff and the required gain-accuracy in the DAC cancellation path relative to the two approaches, respectively, in isolation, it does not reduce the dynamic range and linearity requirements of the DAC cancellation path. Furthermore,  $Q_{e_m}[n]$  must be nearly free of spurious tones, or else high gain-accuracy would again be required in the DAC cancellation path to properly cancel the spurious tones. These problems are addressed in the implemented PLL by several means. As

described in detail below, delta-sigma re-quantization and a segmented, mismatch-shaping, current pulse DAC are used to obtain high DAC cancellation path dynamic range and linearity, and 1-bit dithering is used to eliminate spurious tones.

## C. Phase Noise Cancellation Technique Signal Processing Details

As shown in Fig. 1.1, the architecture consists of a 48 MHz crystal reference source, the PLL core described above, a 48 MHz digital section, a bank of 16 coarse 1-bit current pulse DACs, and a bank of 16 fine 1-bit current pulse DACs. The 48 MHz digital section consists of digital logic in which all registers are clocked on the rising edges of the divider output. It generates y[n] and 32 1-bit sequences that control the two banks of 1-bit current pulse DACs. During each reference period, each 1-bit current pulse DAC generates a positive or negative pulse of current depending upon whether its input bit is high or low. Each pulse has a duration of 4 VCO periods. The nominal magnitudes of the current pulses are  $I_{CP}/16$  and  $I_{CP}/128$  for the coarse and fine 1-bit current pulse DACs, respectively.

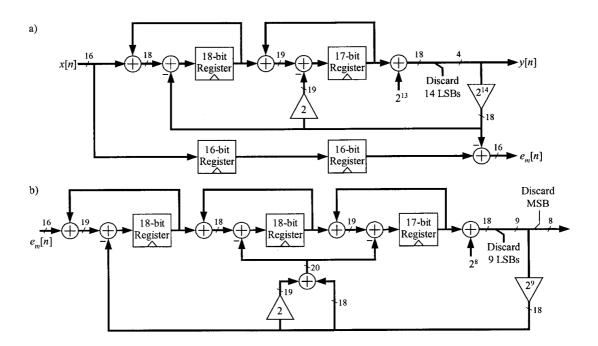

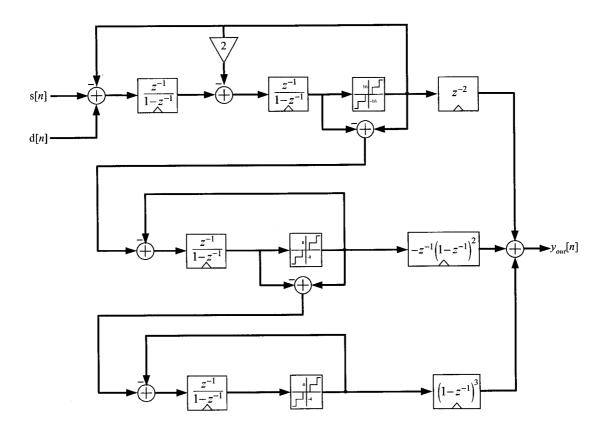

The input to the second-order  $\Delta\Sigma$  modulator, x[n], is a 16 bit two's complement number in the range -1 to 1 of the form  $x[n] = \alpha + x_m[n] + d[n]$ , where  $\alpha = (k - 46)/48$  selects the desired Bluetooth channel frequency for  $k = 0, 1, ..., 78, x_m[n]$  is optional FSK or GFSK modulation, and d[n] is a 1-bit pseudo-random dither sequence. The dither sequence is generated by an on-chip length-22 linear feedback shift register and is scaled such that it represents the least significant bit (LSB) of x[n]. The details of the second-order  $\Delta\Sigma$  modulator are shown in Fig. 1.4(a). It has unity gain and a quantization step-size of unity, so its output has the form  $y[n] = x[n-2] + e_m[n]$ , and

Fig. 1.4: Details of employed digital  $\Delta\Sigma$  modulators – (a) The second-order  $\Delta\Sigma$  modulator. (b) The third-order  $\Delta\Sigma$  modulator.

takes on values in the range: -2, -1, 0, 1, and 2. As proven in [17] and [18], the dither sequence completely eliminates spurious tones in  $e_m[n]$ , so  $e_m[n]$  has the same PSD as white noise passed through a discrete-time filter with two zeros at dc. The discrete-time integration in (1) cancels one of the zeros, so  $Q_{e_m}[n]$  has the first-order shaped PSD represented by the top curve in Fig. 1.3. Although the dither behaves as white noise, its magnitude is sufficiently small that its contribution to the PLL phase noise is negligible in the band of interest.

Ideally, the DAC cancellation path would digitally integrate  $e_m[n]$  to obtain  $Q_{e_m}[n]$  as in (1), and, for each n, inject a current pulse into the loop filter with a width equal to that of the corresponding current pulse from the charge pump and an amplitude chosen such that the total charge carried by the pulse is precisely  $Q_{e_m}[n]$ .

Fig. 1.5: Details of the mismatch-shaping digital encoder.

Unfortunately, this is difficult to accomplish in practice because the precise width of the charge pump pulse is not known a priori, and the pulse can be very narrow. Instead, a fixed-width current pulse can be used. In this case  $Q_{e_m}[n]$  is not cancelled immediately as it is added, so the cancellation process introduces a voltage transient each period at the VCO input. Most of the power associated with the voltage transient is outside of the PLL bandwidth so its contribution to the PLL phase noise tends to be small. In most conventional PLLs with DAC cancellation paths, the pulse width is equal to the reference period [19]. However, in the current work the pulse width is set to four VCO periods to better match the charge pump pulse width thereby reducing the transient at the VCO and decreasing the resulting PLL phase noise contribution.

If  $Q_{e_m}[n]$  were calculated directly using  $e_m[n]$  in (1), a 15-bit current DAC with a step size of  $0.5 \cdot I_{CP} \cdot 2^{-15}$ , e.g., 19.5 nA for the implemented PLL, would be required to generate the necessary current pulses. Such a DAC would be very difficult to implement. Instead, as indicated in Fig. 1.1,  $e_m[n]$  is re-quantized from 16 bits to 8 bits by a third-order digital  $\Delta\Sigma$  modulator, the details of which are shown in Fig.

1.4(b), and the result is digitally integrated and converted to current pulses. The output of the integrator is a 7-bit sequence proportional to  $Q_{e_m}[n-1] + e_{rq}[n]$ , where  $e_{rq}[n]$  is second-order shaped re-quantization noise resulting from digitally integrating the requantization noise from the third-order digital  $\Delta\Sigma$  modulator. Because of its second-order high-pass shape and small magnitude,  $e_{rq}[n]$  does not result in a significant increase in the PLL phase noise. Thus, re-quantization reduces the problem of designing a 15-bit DAC with a minimum step-size of 19.5 nA to that of designing a 7-bit DAC with a minimum step-size of 10  $\mu$ A. The DAC is implemented by the two banks of 1-bit current pulse DACs. During the *n*th reference period the input bits to the 1-bit DACs are chosen such that

$$v[n] = \left[ 8 \cdot \sum_{k=1}^{16} \left( v_{c_k}[n] - \frac{1}{2} \right) + \sum_{k=1}^{16} \left( v_{f_k}[n] - \frac{1}{2} \right) \right] \Delta_v$$

(2)

where v[n] is the output of the digital integrator,  $v_{c_k}[n]$  and  $v_{f_k}[n]$  are 0 or 1 input values to the kth 1-bit DACs in the coarse and fine DAC banks, respectively, and  $\Delta_v$  is the LSB weight of v[n].

For most values of v[n], there are several combinations of  $v_{c_k}[n]$  and  $v_{f_k}[n]$  that satisfy (2). For example, when  $v[n] = -63\Delta_v$ , any one of the 16 1-bit DAC inputs in each DAC bank can be set to 1 with the rest set to 0. To the extent that the 1-bit DACs in each DAC bank are perfectly matched and the ratio between coarse and fine 1-bit DACs is exactly eight, it does not matter which of the possible input selections is made. In conventional segmented DACs good matching is assumed, so for each value of v[n] only one of the combinations of  $v_{c_k}[n]$  and  $v_{f_k}[n]$  that satisfy (2) is ever used.

Unfortunately, if the conventional approach had been used in this work, even mismatches of less than 1% among the unit current sources that make up the 1-bit DACs would give rise to harmonic distortion severe enough to prevent the PLL from meeting the target specifications, and reducing the mismatches to much less than 1% in present CMOS technology can be difficult. To circumvent this problem, a segmented mismatch-shaping DAC encoder is used prior to the banks of 1-bit DACs [20, 21, 22].

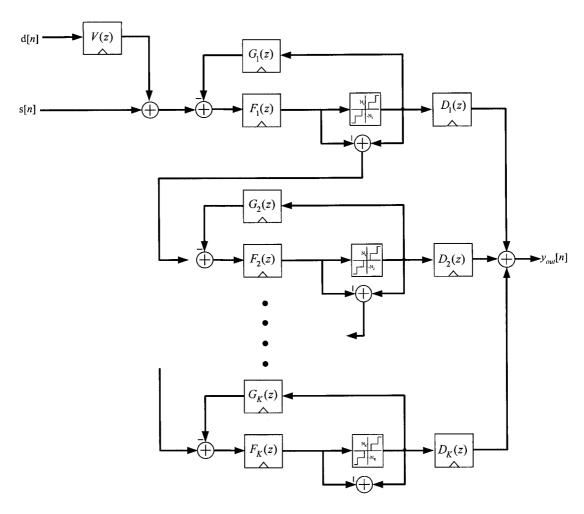

During the *n*th reference period, the encoder selects one of the combinations of  $v_{c_k}[n]$  and  $v_{f_k}[n]$  that satisfy (2) as a function of v[n] such that the error from mismatches introduced by the DAC, referred to as *mismatch-noise*, has first-order highpass spectral shaping with no spurious tones. Consequently, much of the mismatch-noise power is outside the PLL bandwidth. For the implemented PLL, simulations indicate that the target specifications can be met provided the matching of the unit current sources has a standard deviation of no more than 5% which is not difficult to achieve in practice. As shown in Fig. 1.5, the encoder consists of a first-order digital  $\Delta\Sigma$  modulator and two 17-level tree-structured mismatch-shaping encoders of the type presented in [23]. The  $\Delta\Sigma$  modulator quantizes v[n] to a 17-level sequence which drives the 17-level mismatch-shaping encoder associated with the coarse DAC bank. The quantization noise from the  $\Delta\Sigma$  modulator drives the 17-level mismatch-shaping encoder associated with the fine DAC bank.

Fig. 1.6: Simulated output phase noise PSD plots of the implemented PLL (a) without the phase noise cancellation technique, (b)-(f) with the phase noise cancellation technique, 5% unit current source errors in the 1-bit DACs, and 12%, 10%, 4%, 2%, and 0% gain mismatches, respectively, and (g) with ideal phase noise cancellation.

Fig. 1.6 shows simulated output phase noise PSD plots corresponding to quantization noise and mismatch-noise for the implemented PLL with various DAC cancellation path gain error levels. The results were generated by an event-driven simulator that accurately models both the discrete-time and continuous-time portions of the system. The unit current source values in the 1-bit current pulse DACs were chosen with random errors such that they have a 5% standard deviation from their nominal value. As indicated in the figure, even with a 12% DAC cancellation path gain error and the relatively poor current source matching (curve "b" in the figure), the

Fig. 1.7: A conventional charge pump and the associated timing diagram.

phase noise cancellation technique reduces the peak spot phase noise by 20 dB, and the spot phase noise at a 3 MHz offset from the carrier is well below the -120 dBc/Hz value required by the Bluetooth specification.

# III. THE CHARGE PUMP LINEARIZATION TECHNIQUE

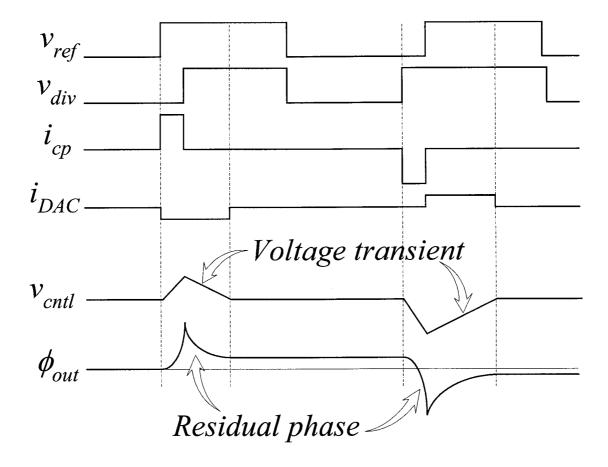

### A. The Problem

A conventional charge pump and the associated timing diagram are shown in Fig. 1.7. The rising edges of the PFD outputs, U and D, are triggered by those of  $v_{ref}(t)$  and  $v_{div}(t)$ , respectively. The falling edges of U and D both occur after a delay of  $T_D$  following the later of the rising edges of  $v_{ref}(t)$  and  $v_{div}(t)$ . The delay ensures that each current source in the charge pump is turned on for a minimum duration of  $T_D$  every reference period to solve the charge pump dead-zone problem [24].

The positive and negative current sources in the charge pump are on when U and D, respectively, are high and are off otherwise. Therefore, neglecting a constant,

the charge carried by  $i_{CP}(t)$  during the *n*th reference period is

$$Q_{CP}[n] = \Delta T_n I_{CP} + \frac{1}{2} |\Delta T_n| \Delta I_{CP}, \qquad (3)$$

where  $\Delta T_n$  is the time difference between the *n*th rising edges of  $v_{div}(t)$  and  $v_{ref}(t)$ , and  $I_{CP}$  and  $\Delta I_{CP}$  are the average of and difference between the positive and negative current source values, i.e.,  $I_{CP+}$  and  $I_{CP-}$ , respectively. Ideally,  $I_{CP+}$  and  $I_{CP-}$  are equal, but in practice they differ because of component mismatches and the different voltages across the respective current source transistors. The result is the second term in (3) which is non-linear with respect to  $\Delta T_n$ .

Unfortunately, the non-linearity induces spurious tones at multiples of  $\alpha f_{ref}$  in the PLL phase noise. The problem becomes increasingly severe as the bandwidth of the PLL is increased, because spurious tones that are well out of band and, thus, highly attenuated in a narrowband PLL are less out of band, and, thus, less attenuated in a wideband PLL. A conventional solution is to use analog feedback to equalize  $I_{CP+}$  and  $I_{CP-}$  [8]. However, in a wideband PLL the charge pump output voltage variations tend to be very abrupt which makes the design of an effective analog compensation circuit difficult.

Fig. 1.8: The modified charge pump and the associated timing diagram.

## B. The Proposed Technique

The charge pump linearization technique involves modifications to both the PFD and the charge pump. The modified PFD generates U and D signals as in the conventional case, but also generates two new signals,  $U_{ped}$  and  $D_{ped}$ . As shown in Fig. 1.8, each reference period the rising edges of  $U_{ped}$  and  $D_{ped}$  are aligned with those of U and D, respectively, but their falling edges both occur after a delay of  $T_{ped}$  following the earlier of the rising edges of  $v_{ref}(t)$  and  $v_{div}(t)$ . The charge pump is modified in that the  $I_{CP+}$  and  $I_{CP-}$  current sources are each split into two nominally identical half-sized current sources. The two halves corresponding to  $I_{CP+}$  are switched by U and  $U_{ped}$ , and the two halves corresponding to  $I_{CP-}$  are switched by U and  $U_{ped}$ , is referred to as the U pedestal time and is designed to be longer than the maximum value of U and U when the PLL is locked. This maximum value is three VCO periods plus U for the implemented PLL, so U can be made sufficiently small that its effect on

the noise introduced by the charge pump is negligible.

It can be shown that, neglecting a constant,

$$Q_{CP}[n] = \Delta T_n I_{CP} + \frac{1}{2} |\Delta T_n| (\Delta I_p - \Delta I_n), \qquad (4)$$

where  $\Delta I_p$  and  $\Delta I_n$  are differences, arising from component mismatches, between the values of the two positive and the two negative current source halves, respectively. As in the conventional charge pump, the differences give rise to a non-linear term in  $Q_{CP}[n]$ . However, in contrast to the conventional case, the non-linear term is a result of mismatches between like current courses with identical voltages across their respective transistors. Therefore, the non-linearity introduced by the proposed technique is much less than that introduced by a conventional charge pump and PFD. Although it was not necessary in this project, the non-linearity can be further suppressed by randomly interchanging the signals U and  $U_{ped}$ , and D and  $D_{ped}$  using a pseudo-random bit sequence.

Table 1.1: Simulated phase noise contributions of the various circuit blocks and the relevant PLL parameters.

| Fractional-N phase locked loop parameters                 |                 |  |  |

|-----------------------------------------------------------|-----------------|--|--|

| Reference frequency                                       | 48 MHz          |  |  |

| Loop bandwidth                                            | 460 kHz         |  |  |

| Zero location                                             | 92 kHz          |  |  |

| Pole location                                             | 2.3 MHz         |  |  |

| Charge pump current                                       | 1.28 mA         |  |  |

| Minimum PFD pulse duration, T <sub>D</sub>                | 0.5  ns - 1  ns |  |  |

| Pedestal duration, T <sub>ped</sub>                       | 3 ns – 6 ns     |  |  |

| Simulated worst case phase contributions at 3 MHz offset: |                 |  |  |

| Voltage controlled oscillator and buffers                 | -127 dBc/Hz     |  |  |

| Modified phase frequency detector                         | -132 dBc/Hz     |  |  |

| Charge pump and DACs                                      | -134 dBc/Hz     |  |  |

| Crystal reference oscillator                              | -134 dBc/Hz     |  |  |

| 1.8 Volt – 2.7 Volt converters                            | -139 dBc/Hz     |  |  |

| Loop filter resistor                                      | -147 dBc/Hz     |  |  |

| Multi-modulus frequency divider                           | -153 dBc/Hz     |  |  |

### IV. CIRCUIT ISSUES

### Overview

The circuit is implemented in the TSMC 0.18 µm 1P6M mixed-signal CMOS process with the thin top-metal option, and installed in a 5mm TQFP 32 pin package. All pads include ESD protection circuitry. The PFD, charge pump, DAC banks, and VCO are designed for a 2.7 V supply. The remaining components are designed for a 1.8 V supply. All the blocks shown in Fig. 1.1 except the crystal and the loop filter capacitors and resistor are implemented on-chip. A VCO output buffer, a VCO divider buffer, a 1.8 V to 2.7 V logic converter block, and a three-wire digital interface are also included on the chip. Separate deep N-wells under the digital logic and critical

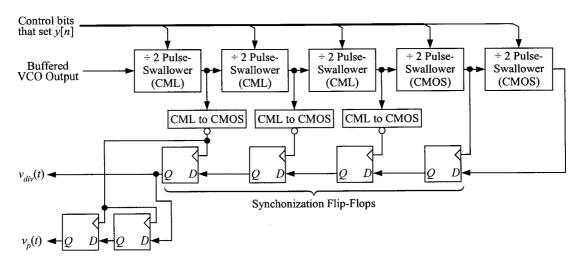

Fig. 1.9: The frequency divider circuit.

analog circuitry, and separate supply domains help prevent digital interference from disturbing analog circuit behavior. A summary of the designed loop parameters and simulated phase noise contributions of the various circuits are shown in Table 1.1.

# Frequency Divider

As shown in Fig. 1.9, the core of the divider consists of five divide-by-two, pulse swallowing blocks [25]. The three highest frequency pulse swallowing blocks consist of current-mode-logic (CML), and the other two blocks consist of static CMOS logic. The four synchronization flip-flops ensure that the rising edges of  $v_{div}(t)$  are aligned to the appropriate rising edges of the first pulse-swallowing block. Two additional flip-flops are used to derive a DAC pulse termination signal that goes high 4 VCO periods after each rising edge of  $v_{div}(t)$ .

The reason for synchronizing the rising edges of  $v_{div}(t)$  to edges of the first pulse-swallowing block is to reduce modulus-dependent delay mismatches, i.e., systematic timing errors in  $v_{div}(t)$  that depend upon y[n]. Such errors have an effect

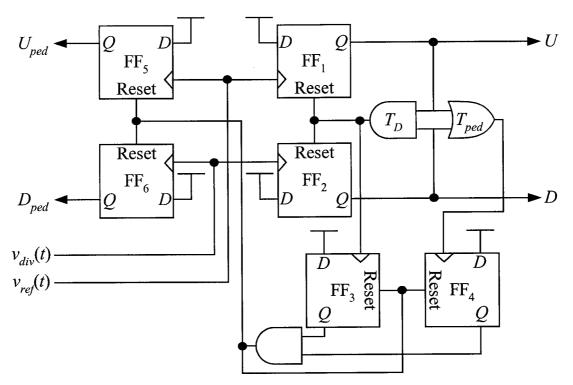

Fig. 1.10: The modified PFD circuit.

similar to charge pump non-linearity in that they induce spurious tones in the PLL phase noise at multiples of  $\alpha f_{ref}$ . Simulations of the implemented PLL indicate that modulus-dependent delay mismatches must be restricted to less than 1% of the VCO period, i.e., to less than 4 ps, to suppress the spurious tones to less than -60 dBc. This is achieved by the synchronization flip-flops which successively align the edges of the signal from the last pulse swallowing block to those of the previous pulse swallowing blocks. In principle, only the final flip-flop is necessary, but the other three are included to avoid race conditions.

# PFD, Charge Pump, and 1-bit Current Pulse DACs

The PFD is shown in Fig. 1.10. Flip-flops 1 and 2 and the associated AND gate generate the U and D signals as in a conventional PFD, and the remaining circuitry

generates the  $U_{ped}$  and  $D_{ped}$  signals. The circuit is configured such that the rising edges of  $U_{ped}$  coincide with those of U, and the rising edges of  $D_{ped}$  coincide with those of D. The AND gate and OR gate driven by U and D have built-in delays of  $T_D$  and  $T_{ped}$ , respectively. Therefore, during the nth reference period, flip-flops 1 and 2 are reset after a delay of  $\Delta T_n + T_D$  following the earlier of the times at which U and D go high, whereas flip-flops 5 and 6 are reset after a delay of the maximum of  $\Delta T_n + T_D$  and  $T_{ped}$  following the earlier of the times at which U and D go high.

As described in the previous section,  $T_{ped}$  is chosen to be longer than the maximum value of  $\Delta T_n + T_D$  expected to occur when the PLL is locked, in which case the PFD output signals are as illustrated in Fig. 1.8. When the PLL is in the process of acquiring lock,  $\Delta T_n + T_D$  is usually longer than  $T_{ped}$ . In this case U coincides with  $U_{ped}$  and D coincides with  $D_{ped}$ , so the current from the charge pump is the same as in the conventional case. Therefore, the charge pump linearization technique does not affect the behavior of the PLL during acquisition.

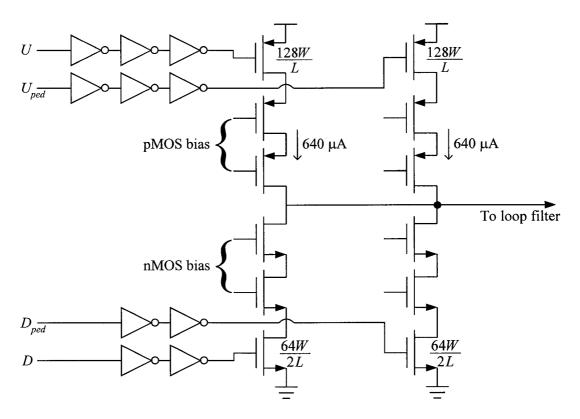

Fig. 1.11: The modified charge pump circuit.

As shown in Fig. 1.11, and explained in the previous section, the charge pump consists of two halves, one controlled by U and D, and the other controlled by  $U_{ped}$  and  $D_{ped}$ . Each half consists of positive and negative 640  $\mu$ A cascode current sources with triode MOS switches near the supply rails [26]. The pMOS transistors that make up the switches and cascode current sources have twice the width and half the length of the corresponding nMOS transistors so as to approximately match the loading on the PFD output lines and the switching speeds of the positive and negative current sources. The chains of inverters are scaled to have a common propagation delay so the inverted copies of U and  $U_{ped}$  presented to the pMOS switches are properly aligned with the non-inverted copies of D and  $D_{ped}$  presented to the nMOS switches [24].

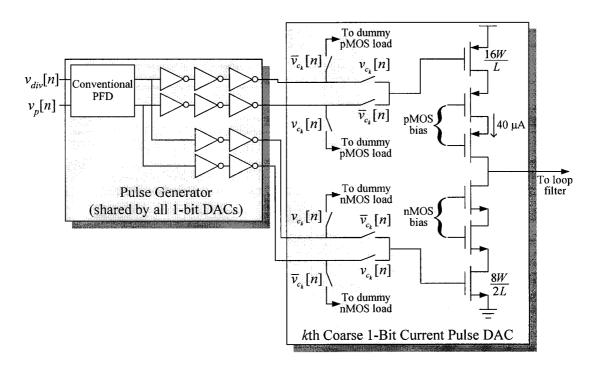

Fig. 1.12: The DAC pulse generator and the kth coarse 1-bit current pulse DAC circuits.

Figure 1.12 shows a simplified circuit diagram of the kth coarse 1-bit current pulse DAC and the pulse generator shared by all the 1-bit current pulse DACs. The switched current sources in the coarse and fine 1-bit current pulse DACs, respectively, are 40  $\mu$ A and 5  $\mu$ A scaled down versions of the those in the charge pump. The pulse generator contains a copy of the conventional portion of the PFD described above and four chains of scaled inverters similar to those that drive the charge pump switches. The PFD is driven by the two divider output signals, so each reference period its top output goes high for a duration of 4 VCO periods plus  $T_D$ , and its bottom output goes high for a duration of only  $T_D$ . Inverted and non-inverted copies of these signals are presented to each 1-bit current pulse DAC to drive the pMOS and nMOS switches, respectively. In each case, the 1-bit DAC input causes one of these signals to be presented to the MOS switch and the other to be presented to a dummy MOS switch.

The purpose of the dummy MOS switches is to maintain data-invariant loads on the pulse generator output lines.

## Voltage Controlled Oscillator

The on-chip VCO is a negative- $g_m$  CMOS LC oscillator designed to have a center frequency of 2.448 GHz. It incorporates a differential inductor implemented as a square spiral of metal layers 5 and 6 sandwiched together. A MOS varactor provides 200 MHz/V tuning over a 1 V range. The differential VCO outputs are ac-coupled to two resistively loaded differential source-coupled buffers: one to drive the divider and one to drive 50  $\Omega$  loads off the chip. A configuration option allows for the use of an off-chip VCO in place of the on-chip VCO; the on-chip VCO can be disabled and a direct connection is provided from a pin to the input of the divider buffer.

## Loop Filter

The loop filter components are:  $R = 641 \Omega$ ,  $C_I = 100 \text{ pF}$ , and  $C_2 = 2.4 \text{ nF}$ , of which R,  $C_2$ , and 60 pF of  $C_I$  are off-chip. The remaining 40 pF of  $C_I$  is on-chip to help reduce the voltage variations caused by fast charge pump current switching through the inductive bond wires. Given that the divider modulus is approximately 51, the VCO gain is 200 MHz/V, and the nominal charge pump current magnitude is  $2\times640 \mu\text{A}$ , these component values give rise to a PLL bandwidth of approximately 460 kHz.

## 48 MHz Digital Logic

The 48 MHz digital logic was implemented using a standard cell library

available to the authors in which the transistors have a minimum gate length of 0.25  $\mu m$ . While a more compact and lower power design would have been possible with a standard cell library optimized for the 0.18  $\mu m$  process, the project schedule did not permit such optimization.

#### V. MEASUREMENT RESULTS

Three copies of the IC were tested on separate circuit boards. The performance of each part was verified for all 79 Bluetooth channels with the phase noise cancellation and charge pump linearization techniques individually and simultaneously enabled and disabled with and without FSK modulation. On each Bluetooth channel and each part, the phase noise cancellation technique was found to reduce the spot phase noise by 16 dB or better, and the charge pump linearization technique was found to reduce the spurious tone floor by 8 dB or better. With both techniques enabled, each part was found to achieve a worst-case phase noise of –121 dBc/Hz at 3 MHz offsets, a worst-case spurious tone level of –54 dBc, and a worst-case in-band noise floor of –96 dBc/Hz. The measured results are summarized in Table 1.2, and a die photograph is shown in Fig. 1.13.

Table 1.2: Performance summary.

| Design Details:                                                                |                                                                    |                       |       |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|-------|

| Technology                                                                     | TSMC 0.18μm 1P6M CMOS                                              |                       |       |

| Package                                                                        | $5 \times 5 \text{ mm}^2$ , 32 pin TQFP                            |                       |       |

| Die Area                                                                       | $2.72 \times 2.47 \text{ mm}^2$ (includes pads and ESD protection) |                       |       |

| Frequency Range                                                                | 2402 + k MHz, $k = 0, 1, 2,, 78$                                   |                       |       |

| Crystal Reference                                                              | 48 MHz                                                             |                       |       |

| Loop Bandwidth                                                                 | 460 kHz                                                            |                       |       |

| Measured Current Consumption, $V_{DD}$ , and                                   | d Area by Block:                                                   |                       |       |

| VCO                                                                            | 3.0 mA @ 1.9 V                                                     | $0.4 \text{ mm}^2$    | 67 mW |

| PFD, CP & DAC                                                                  | 10.3 mA @ 1.9 V                                                    | $0.04 \text{ mm}^2$   |       |

| Divider                                                                        | 6.7 mA @ 1.8 V                                                     | $0.4 \text{ mm}^2$    |       |

| Digital Logic                                                                  | 8.8 mA @ 2.2 V                                                     | $0.68 \text{ mm}^2$   |       |

| Internal VCO Buffer                                                            | 5.6 mA @ 1.8 V                                                     | $0.013 \text{ mm}^2$  |       |

| Crystal Oscillator Buffer                                                      | 4.1 mA @ 2.2 V                                                     | $0.04 \text{ mm}^2$   | 21 mW |

| External VCO Buffer                                                            | 6.9 mA @ 1.8 V                                                     | $0.015 \text{ mm}^2$  |       |

| Measured Worst Case Performance With Both Techniques <i>Enabled</i> :          | On-chip VCO:                                                       | Off-chip VCO:         |       |

| Phase Noise @ 50 kHz                                                           | -96 dBc/Hz                                                         | –96 dBc/Hz            |       |

| Phase Noise @ 3 MHz                                                            | -121 dBc/Hz                                                        | -127 dBc/Hz           |       |

| Largest Fractional Spur @ < 2 MHz                                              | −54 dBc @ 1 MHz                                                    | -45 dBc @ 1 MHz       |       |

| Largest Fractional Spur @≥2 MHz                                                | -56 dBc @ 2 MHz                                                    | -58 dBc @ 2 MHz       |       |

| Largest Fractional Spur @≥3 MHz                                                | -57 dBc @ 3 MHz                                                    | −62 dBc @ 3 MHz       |       |

| Reference Spur                                                                 | -65 dBc                                                            | -66 dBc               |       |

| Measured Worst Case Performance With Both Techniques <i>Disabled</i> :         | On-chip VCO:                                                       | Off-chip VCO:         |       |

| Phase Noise @ 50 kHz                                                           | -96 dBc/Hz                                                         | -96 dBc/Hz            |       |

| Phase Noise @ 3 MHz                                                            | -107 dBc/Hz                                                        | -107 dBc/Hz           |       |

| Largest Fractional Spur @ < 2 MHz                                              | -40 dBc @ 1 MHz                                                    | -35 dBc @ 1 MHz       |       |

| Largest Fractional Spur @ \ge 2 MHz                                            | -44 dBc @ 2 MHz                                                    | -46 dBc @ 2 MHz       |       |

| Largest Fractional Spur @ \ge 3 MHz                                            | -49 dBc @ 3 MHz                                                    | -52 dBc @ 3 MHz       |       |

| Measured Performance With Both Techniques Disabled:                            | On-chip VCO:                                                       | Off-chip VCO:         |       |

| Effect of charge pump linearization technique on phase noise                   | None observed                                                      | None observed         |       |

| Effect of $\Delta\Sigma$ noise cancellation technique on fractional spur level | None observed                                                      | 2-9 dB spur reduction |       |

Fig. 1.13: Die photograph.

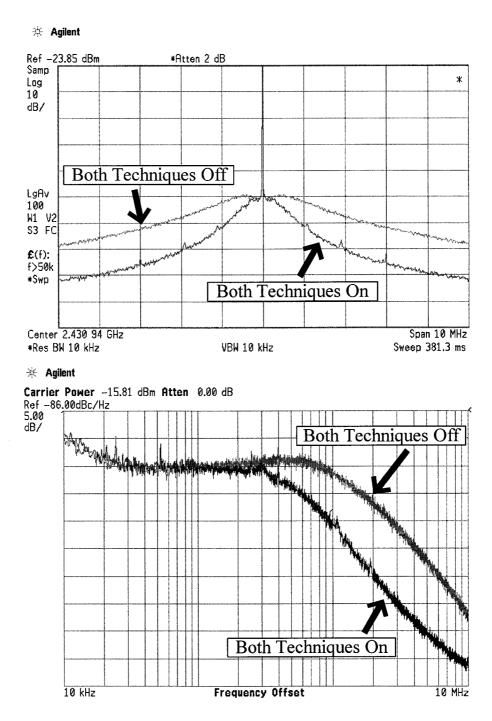

Figs. 1.14 and 1.15 show representative PSD plots measured with the PLL set to the 2.431 GHz Bluetooth channel and the phase noise cancellation and charge pump linearization techniques both enabled and both disabled. Fig. 1.14 shows PSD plots of the PLL output signal and phase noise with the PLL operating without modulation. Fig. 1.15 shows PSD plots of the PLL output signal for the PLL operating with 1 Mb/s FSK modulation. In both cases the phase noise improvement resulting from the techniques is evident. Similar results are seen for each part on every Bluetooth channel.

Fig. 1.14: Measured PSD plots of the output signal and phase noise of the PLL tuned to 2.431 GHz without modulation.

#### Agilent

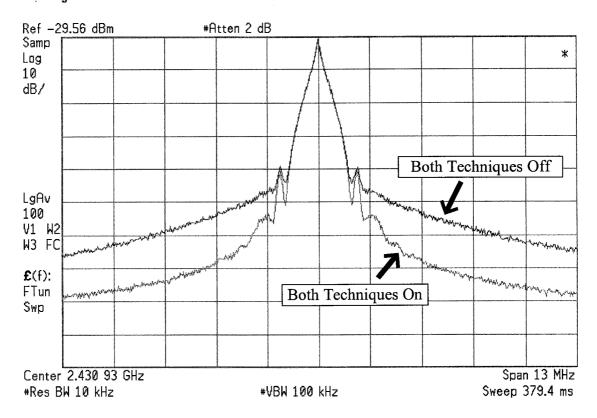

Fig. 1.15: Measured PSD plot of the output signal of the PLL tuned to 2.431 GHz with 1 Mb/s FSK modulation.

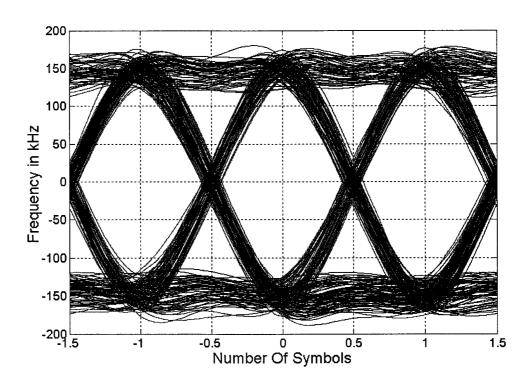

Fig. 1.16 shows an eye pattern from the PLL with 1 Mb/s FSK transmit modulation and both techniques enabled measured by down-converting the PLL output signal to an intermediate frequency through a spectrum analyzer and frequency demodulating the result using a vector analyzer. The minimum frequency deviation is approximately 120 kHz and the zero-crossing error is less than one-eighth of the symbol period as required by the application. Again, almost identical results were observed for each part on every Bluetooth channel.

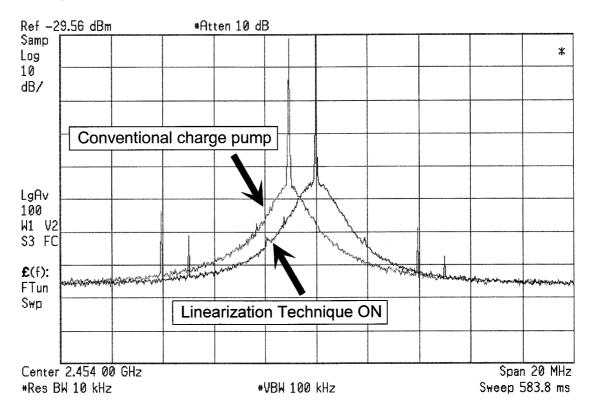

The spurious tone reduction achieved by the charge pump linearization technique is most easily observed when the PLL is tuned to Bluetooth channels that are

Fig. 1.16: Measured eye pattern corresponding to the output signal shown in Fig. 1.17.

close to integer multiples of the 48 MHz reference frequency. In such cases  $\alpha$  is small, so the spurious tones in the PLL phase noise resulting from non-linearity, which occur at multiples of  $\alpha f_{ref}$ , are not highly attenuated by the lowpass transfer function of the PLL. Fig. 1.17 shows PSD plots of the PLL output signal with and without the charge pump linearization technique enabled for such a case, i.e., for the VCO tuned to 2.453 GHz so that  $\alpha f_{ref} = 5$  MHz. The overlaid plots are intentionally displaced in frequency to make the spurious tone reduction visible.

As mentioned in the previous section, the VCO and charge pump were designed to operate from a 2.7 V supply with a VCO center frequency of 2.448 GHz, but the measured VCO center frequency turned out to be 2.25 GHz. To force the VCO

#### ★ Agilent

Fig. 1.17: Measured PSD plots of the PLL tuned to 2.453 GHz with the charge pump linearization technique enabled and disabled.

into the Bluetooth frequency range the VCO and charge pump, which share the same power supply lines, had to be run from a 1.9 V supply during testing. It is likely that this increased the phase noise by at least 3 dB and increased distortion because several critical transistors were forced into their triode regions. Nevertheless, as described above and summarized in Table 1.2 the IC performed well.

Each of the tested parts met the Bluetooth phase noise and eye pattern specifications on all channels. They also met the Bluetooth spurious tone specifications except for a small number of channels on which the spurious tones were at most 3 dB above the specification. The slightly elevated spurious tone level is a

result of having to run the VCO and charge pump from a 1.9 V supply instead of the 2.7 V supply for which it was designed. In support of this assertion, the PLL configured with an off-chip VCO and the charge pump operating from a 2.7 V supply was found to meet all required specifications on all channels (see Table 1.2).

The circuitry was designed conservatively to help ensure first-silicon success and clearly demonstrate the phase noise cancellation and charge pump linearization techniques. In particular, as tabulated in Table 1.1, large noise margins were used in the designing the circuits to ensure that the phase noise below 5 MHz would be dominated by residual  $\Delta\Sigma$  quantization noise and spurious tones resulting from nonlinearities. Consequently, the measured in-band phase noise is much lower than required to meet the Bluetooth specifications. While this design strategy has served the purpose of demonstrating the phase noise cancellation and charge pump linearization techniques, the current consumption of the PLL could be reduced significantly by optimizing the analog circuitry so that its in-band noise contribution is closer to the Bluetooth specification.

#### VI. CONCLUSION

A phase noise cancellation technique and a charge pump linearization technique have been proposed and demonstrated as enabling components in a wideband CMOS  $\Delta\Sigma$  fractional-N PLL configured as a Bluetooth wireless LAN transmitter. The phase noise cancellation technique relaxes the fundamental tradeoff between phase noise and bandwidth in conventional  $\Delta\Sigma$  fractional-N PLLs and does not require tight component matching or calibration. Theoretical and experimental

results have been presented that indicate the technique enables a ten-fold increase in PLL bandwidth without an increase in spot phase noise. The charge pump linearization technique provides a simple means of improving the spurious performance of wideband fractional-*N* PLLs that avoids the bandwidth limitations of previously presented techniques involving analog feedback circuits.

#### CHAPTER ACKNOWLEDGEMENTS

The text of Chapter 1 is set to appear as a regular paper in the *IEEE Journal of Solid State Circuits*. The dissertation author was the primary researcher. Ian Galton supervised the research which forms the basis of the chapter. Lars Jansson assisted in the partial design of the integrated circuit. The author is grateful to Eric Fogleman, Kishore Seendripu, Eric Siragusa, Andrea Spandonis, Ashok Swaminathan, Kevin Wang, Jared Welz, and Sheng Ye for their assistance with and advice regarding this project.

#### REFERENCES

- 1. F. L. Martin, et. al., "A wideband 1.3 GHz PLL for transmit remodulation suppression," *IEEE International Solid-State Circuits Conference*, Digest of Technical Papers, vol. 44, pp. 164-165, Feb. 2001.

- 2. G. Chang, et. al. "A direct-conversion single-chip radio-modem for Bluetooth," *IEEE International Solid-State Circuits Conference*, Digest of Technical Papers, vol. 45, Feb. 2002.

- 3. M. H. Perrott, T. L. Tewksbury III, C. G. Sodini, "A 27-mW CMOS fractional-N synthesizer using digital compensation for 2.5-Mb/s GFSK modulation,"

- IEEE Journal of Solid-State Circuits, vol. 32, no. 12, pp. 2048-2059, Dec. 1997.

- 4. N. Filiol, et. al., "A 22 mW Bluetooth RF transceiver with direct RF modulation and on-chip IF filtering," *IEEE International Solid-State Circuits Conference*, Digest of Technical Papers, vol. 44, pp. 202-203, Feb. 2001.

- D. R. McMahill, C. G. Sodini, "A 2.5-Mb/s GFSK 5.0-Mb/s 4-FSK Automatically Calibrated Σ-Δ Frequency Synthesizer," *IEEE Journal of Solid State Circuits*, vol. 37, no. 1, pp. 18-26, January 2002.

- 6. D. R. McMahill, C. G. Sodini, "Automatic calibration of modulated frequency synthesizers," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 49, no. 5, pp. 301-311, May 2002.

- 7. S. Willingham, et. al., "An integrated 2.5GHz ΣΔ frequency synthesizer with 5μs settling and 2Mb/s closed loop modulation," *IEEE International Solid-State Circuits Conference*, Digest of Technical Papers, vol. 43, pp. 200-201, Feb. 2000.

- 8. J. S. Lee, et. al., "Charge pump with perfect current matching characteristics in phase-locked loops," *Electronic Letters*, vol. 36, no. 23, pp. 1907-1908, November 2000.

- 9. M. H. Perrott, M. D. Trott, C. G. Sodini, "A Modeling Approach for D-S Fractional-N Frequency Synthesizers Allowing Straightforward Noise Analysis," *IEEE Journal of Solid State Circuits*, vol. 37, no. 8, pp. 1028-38, August 2002.

- 10. G. C. Gillette, "Digiphase Synthesizer," *Proc of the 23rd Annual Frequency Control Symposium*, pp. 201-210, 1969.

- 11. N. B. Braymer, "Frequency synthesizer," United States Patent no. 3,555,446, January 12, 1971.

- 12. W. F. Egan, *Frequency Synthesis by Phase Lock*, second edition, Wiley Interscience, 2000.

- 13. J. A. Crawford, *Frequecy Synthesizer Design Handbook*, Artech House Inc., 1994.

- 14. B. Miller, B. Conley, "A multiple modulator fractional divider," *Annual IEEE Symposium on Frequency Control*, vol. 44, pp. 559-568, March 1990.

- 15. B. Miller, B. Conley, "A multiple modulator fractional divider," *IEEE Transactions on Instrumentation and Measurement*, vol. 40, no. 3, pp. 578-583, June 1991.

- 16. T. A. Riley, M. A. Copeland, T. A. Kwasniewski, "Delta-sigma modulation in fractional-N frequency synthesis," *IEEE Journal of Solid-State Circuits*, vol. 28, no. 5, pp. 553-559, May, 1993.

- 17. I. Galton, "One-bit dithering in delta-sigma modulator-based D/A conversion," *Proc. of the IEEE International Symposium on Circuits and Systems*, vol. 2, pp. 1310-1313, May 1993.

- 18. I. Galton, "Granular quantization noise in a class of delta-sigma modulators," *IEEE Transactions on Information Theory*, vol. 40, no. 3, pp. 848-859, 1994.

- 19. N. King, "Phase locked loop variable frequency generator" United States Patent no. 4,204,174, May 20, 1980.

- 20. I. Galton, "Spectral shaping of circuit errors in digital-to-analog converters," *IEEE Trans. Circuits Syst. II*, vol. 44, no. 10, pp. 808-17, Oct. 1997.

- 21. R. Adams, K. Q. Nguyen, "A 113-dB SNR Oversampling DAC with Segmented Noise-Shaped Scrambling", *IEEE Journal of Solid-State CIrcuits*, vol. 33, no. 12, pp. 1871-1878, Dec. 1998.

- 22. A. Fishov, E. Siragusa, J. Welz, E. Fogleman, I. Galton, "Segmented mismatch-shaping D/A conversion," *Proc. of the IEEE International Symposium on Circuits and Systems*, May 2002.

- 23. E. Fogleman, I. Galton, W. Huff, H. T. Jensen, "A 3.3V single-poly CMOS audio ADC delta-sigma modulator with 98dB peak SINAD and 105dB peak SFDR," *IEEE Journal of Solid State Circuits*, vol. 35, no. 3, pp. 297-307, March, 2000.

- 24. B. Razavi, *Design of Analog CMOS Integrated Circuits*, first ed., McGraw Hill, 2001, pp. 562-566.

- 25. C. S. Vaucher, D. Kasperkovitz, "A Wide-Band Tuning System For Fully Integrated Satellite Receivers," *IEEE Journal of Solid State Circuits*, vol. 33, no. 7, pp. 987-997, July 1998.

- 26. W. Rhee, "Design of High-Performance CMOS Charge Pumps In Phase Locked Loops," *Proc. of the IEEE International Symposium on Circuits and Systems*, vol. 2, pp. 545-548, 1999.

# Phase Noise Cancellation Design Tradeoffs in Delta-Sigma Fractional-N PLLs

Sudhakar Pamarti and Ian Galton

Abstract—A theoretical analysis of a recently proposed phase noise cancellation technique that relaxes the fundamental tradeoff between phase noise and bandwidth in  $\Delta\Sigma$  fractional-N PLLs is presented. The limits imposed by circuit errors and PLL dynamics on the phase noise and loop bandwidth that can be achieved by PLLs incorporating the technique are quantified. Design guidelines are derived that enable customization of the technique in terms of PLL target specifications.

#### I. INTRODUCTION

A phase noise cancellation technique is presented in [1] that employs a digital-to-analog converter (DAC) cancellation path to suppress the phase noise arising from quantization error in a delta-sigma ( $\Delta\Sigma$ ) fractional-N phase locked loop (PLL). The technique has been shown to allow a ten-fold increase in the PLL bandwidth without increasing the spot phase noise arising from  $\Delta\Sigma$  modulator quantization noise for a specific PLL architecture and application: a 2.4 GHz second-order  $\Delta\Sigma$  fractional-N PLL with a 460 kHz minimum bandwidth and 1 Mb/s in-loop FSK modulation for a Bluetooth wireless LAN compliant direct conversion transceiver. This paper presents a theoretical analysis of the phase noise cancellation technique with the goal of facilitating its application to realize other wide bandwidth, low noise  $\Delta\Sigma$  fractional-N PLLs.

Fig. 2.1: A high level functional diagram of the  $\Delta\Sigma$  FNPLL presented in [1].

Circuit errors and the dynamics of the PLL impose limits on the phase noise and bandwidth achievable using the phase noise cancellation technique. The technique employs quantization noise shaping, mismatch noise shaping, and one-bit dithering to significantly reduce these limits compared to prior art [2, 3, 4, 5, 6]. The paper quantifies the effects of noise shaping and dithering on the PLL phase noise, presents guidelines to customize the phase noise cancellation technique as a function of the PLL target specifications, and presents guidelines to reduce the hardware complexity of the technique without adversely effecting the PLL phase noise.

Section II presents an overview of the phase noise cancellation technique and

describes the various ways in which it can be customized. Sections III and IV analyze the limits imposed on the effectiveness of the phase noise cancellation technique by circuit gain errors and PLL dynamics, respectively. Sections V and VI present methods for reducing the hardware complexity of the technique.

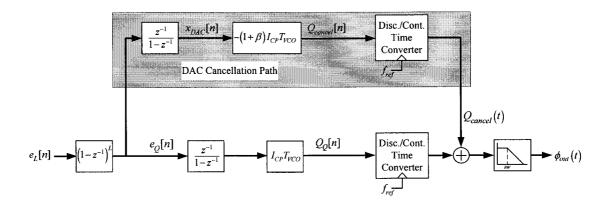

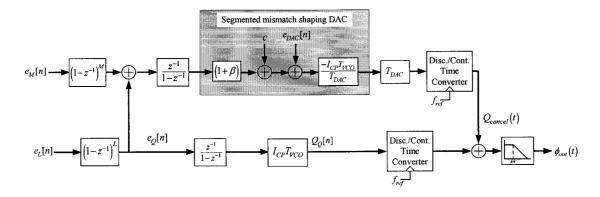

## II. OVERVIEW OF PHASE NOISE CANCELLATION TECHNIQUE

A high level functional diagram of the integrated circuit (IC) presented in [1] is reproduced in Fig. 2.1. It includes all the components of a conventional second-order  $\Delta\Sigma$  fractional-N PLL and some additional components which constitute the phase noise cancellation technique. These additional components are indicated by the shaded blocks in the figure. The segmented mismatch shaping DAC encoder and the two banks of 1-bit current DACs together constitute a DAC, which is henceforth referred to as the *cancellation DAC*. In the absence of the phase noise cancellation technique, the quantization noise,  $e_Q[n]$ , from the second-order digital  $\Delta\Sigma$  modulator effectively injects a charge sample,  $Q_Q[n]$ , into the loop filter each reference period, thereby perturbing the VCO and causing phase noise. The cancellation technique suppresses this phase noise by nominally injecting  $-Q_Q[n]$  into the loop filter. Aside from a constant offset, the sequence of charge samples is well modeled as

$$Q_{Q}[n] = I_{CP} T_{VCO} \sum_{k=n_{0}}^{n-1} e_{Q}[k],$$

(1)

where  $I_{CP}$  is the nominal charge pump current,  $T_{VCO}$  is the nominal period of the PLL output, and  $n_0 < n$  is an arbitrary starting time index. The phase noise cancellation technique generates an estimate of  $-Q_Q[n]$  by digitally computing  $e_Q[n]$ , reducing its

bit-width using the third-order digital  $\Delta\Sigma$  modulator, accumulating the result, and using the cancellation DAC to generate proportional analog charge samples. The cancellation DAC generates charge samples by injecting appropriately scaled current pulses which are four VCO periods wide. The combination of the third-order digital  $\Delta\Sigma$  modulator, the integrator, and the cancellation DAC is referred to as the DAC cancellation path. Note that while the pseudo-random bit generator is a part of some conventional  $\Delta\Sigma$  fractional-N PLLs, it is shaded in the figure to emphasize its essential role in the phase noise cancellation technique. Later sections of the paper describe the role in detail.

The goal of the phase noise cancellation technique is to remove all of  $Q_Q[n]$  without introducing other sources of error. However, gain mismatches between the charge pump and cancellation DAC cause a portion of  $Q_Q[n]$  to be left behind in the loop filter every reference period. Similarly, requantization of  $e_Q[n]$  in the cancellation path, mismatches among the 1-bit current DACs, and 1-bit dithering contribute additional error charge along with that left behind by imperfect cancellation of  $Q_Q[n]$ . In spite of these imperfections, the system in Fig. 2.1 achieves a low phase noise while maintaining a minimum bandwidth of 460 kHz. In order to achieve the same peak spot phase noise without the phase noise cancellation technique, a PLL bandwidth of no more than 50 kHz would be required. This bandwidth extension is the principal benefit of the phase noise cancellation technique. The success of the

$^{1}$  For example, at 3 MHz from the PLL center frequency the phase noise is -127 dBc/Hz.

technique results from several architectural choices:

- use of a second-order digital  $\Delta\Sigma$  modulator to choose the frequency division ratios,

- use of cancellation DAC current pulses with durations of 4 VCO periods,

- use of a third-order digital  $\Delta\Sigma$  modulator with which to requeantize  $e_Q[n]$  to 8 bits,

- use of a segmented mismatch shaping DAC encoder, and

- use of one-bit dither.

As is shown in the remainder of the paper, the first two choices determine the bandwidth and phase noise performance limits of the cancellation technique. The other choices reduce the hardware complexity of the DAC cancellation path while ensuring that phase noise due to the requantization error, dither, and mismatches among the 1-bit DACs is free of spurious tones and otherwise negligible.

The analysis offers design guidelines for how to customize the phase noise cancellation technique to  $\Delta\Sigma$  fractional-N PLLs of other specifications. For instance, one might use a second-order digital  $\Delta\Sigma$  modulator to requantize  $e_Q[n]$  instead of a third-order  $\Delta\Sigma$  modulator, or requantize  $e_Q[n]$  to 4-bits instead of 8-bits. The analysis is performed in the context of a system that uses the same general architecture as shown in Fig. 2.1 but possibly differs in the parameters of the PLL and the above mentioned choices. Expressions are derived that predict the power spectral density (PSD) of the PLL phase noise caused by errors in the DAC cancellation path. These expressions are explicit functions of most of the above mentioned choices. For

example, one of the expressions is a function of the duration of DAC current pulses. A designer can use the expressions to pick values for the above choices that ensure that the PLL phase noise is small enough to meet specific requirements. To avoid burdening the designer with too many equations, qualitative recommendations are presented to serve as design guidelines in customizing the phase noise cancellation technique.

For ease of reference, the digital  $\Delta\Sigma$  modulator used to choose the sequence of division ratios is henceforth called a *fractional modulator*, and the digital  $\Delta\Sigma$  modulator which requantizes  $e_Q[n]$  is called the *requantization modulator*.

#### III. FRACTIONAL MODULATOR ORDER

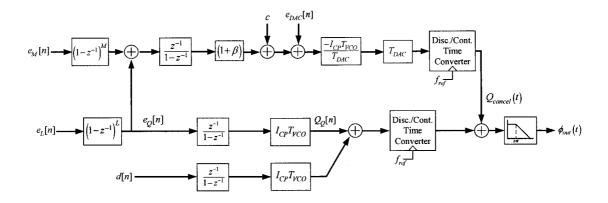

Any mismatch between the charge pump current and the cancellation DAC current causes phase noise in the PLL output. This phase noise tends to dominate the contributions of other errors in the cancellation path such as requantization and mismatches among the 1-bit DACs. This section studies the impact of the order of the fractional modulator, L, on the phase noise caused by the mismatch. The requantization of  $e_O[n]$  is ignored to simplify analysis.

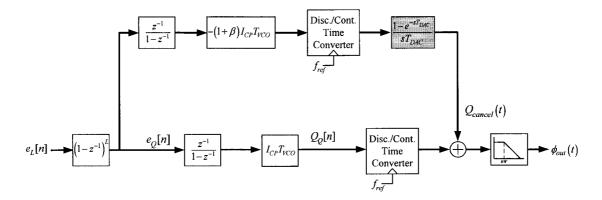

Suppose that  $I_{DAC}$  in Amperes is the nominal gain of the cancellation DAC, and  $x_{DAC}[n]$  is its (unitless) input sequence. Then, the cancellation DAC generates current pulses which have nominal current values  $i_{DAC}[n] = -I_{DAC}x_{DAC}[n]$ . Since the requantization of  $e_Q[n]$  is ignored, it follows from Fig. 2.1 that  $x_{DAC}[n]$  is just the sum of all the past values of  $e_Q[n]$ :

Fig. 2.2: A model for the cancellation technique including a gain error in the cancellation path.

$$x_{DAC}[n] = \sum_{k=n_0}^{n-1} e_Q[k].$$

Suppose that  $T_{DAC}$  is the nominal duration of the cancellation DAC current pulses. Therefore, the charge added to the loop filter by the cancellation path is

$$Q_{cancel}[n] = i_{DAC}[n] \cdot T_{DAC} = -I_{DAC}T_{DAC} \sum_{k=n_0}^{n-1} e_Q[k].$$

It follows from (1) that to cancel  $Q_Q[n]$ ,  $T_{DAC}$  and  $I_{DAC}$  must satisfy  $I_{DAC}T_{DAC} = I_{CP}T_{VCO}$ . Suppose that there is a normalized mismatch,  $\beta$ , between the charge pump current and  $I_{DAC}$  i.e., the cancellation DAC has a gain of  $(1 + \beta)I_{DAC}$  instead of  $I_{DAC}$ . Then,

$$Q_{cancel}[n] = -(1+\beta)I_{CP}T_{VCO}\sum_{k=n_0}^{n-1} e_{Q}[k].$$

(2)