# UNIVERSITY OF CALIFORNIA, SAN DIEGO

# Phase Realignment and Phase Noise Suppression

in PLLs and DLLs

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in Electrical and Computer Engineering (Electronic Circuits & Systems)

by

Sheng Ye

Committee in charge: Professor Ian Galton, Chair Professor William Coles Professor Lawrence Larson Professor Lev Tsimring Professor Daniel Wulbert

2003

UMI Number: 3091345

UMI Microform 3091345

Copyright 2003 by ProQuest Information and Learning Company. All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

> ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Copyright ©

Sheng Ye, 2003

All rights reserved

To my family...

# TABLE OF CONTENTS

|    | Signature Page                                           | iii  |

|----|----------------------------------------------------------|------|

|    | Dedication                                               | iv   |

|    | Table of Content                                         | v    |

|    | List of Figures                                          | vi   |

|    | List of Tables                                           | X    |

|    | Acknowledgements                                         | xi   |

|    | Vita                                                     | xiii |

|    | Publications                                             | xiv  |

|    | Abstract of the Dissertation                             | XV   |

| 1. | A Simple Model for the Design of Coupled Oscillator      |      |

|    | Clock Distribution Networks                              | 1    |

| 2. | A Multiple-Crystal Interface PLL with VCO Realignment to |      |

|    | Reduce Phase Noise                                       | 33   |

| 3. | Techniques for In-band Phase Noise Suppression in        |      |

|    | Re-circulating DLLs                                      | 61   |

v

# LIST OF FIGURES

Chapter 1

| 1.1 | Clock distribution using coupled oscillator networks                                                                                                                                                                                   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Each oscillator in the coupled oscillator network is modeled as a one-port device.                                                                                                                                                     |

|     |                                                                                                                                                                                                                                        |

| 1.3 | Block diagram of the proposed oscillator model7                                                                                                                                                                                        |

| 1.4 | Schematics of the resistively coupled oscillator pair                                                                                                                                                                                  |

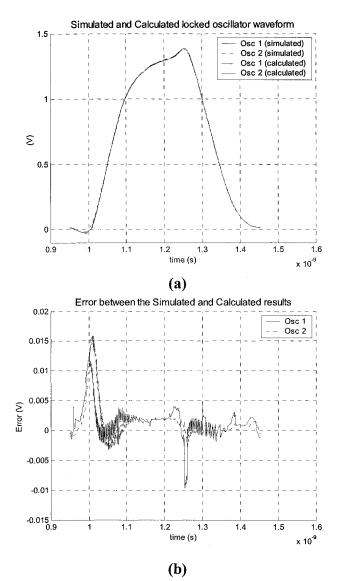

| 1.5 | Comparison between transistor level simulation and theoretical calculation of the coupled oscillator pair. (a) Waveform of one locked period. (b) Absolute error between simulation and calculation                                    |

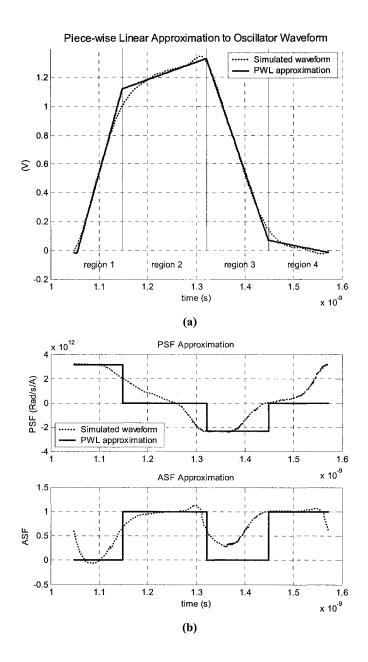

| 1.6 | (a) Piece-wise linear approximation of the waveform. (b) Piece-wise linear approximation of the PSF and ASF                                                                                                                            |

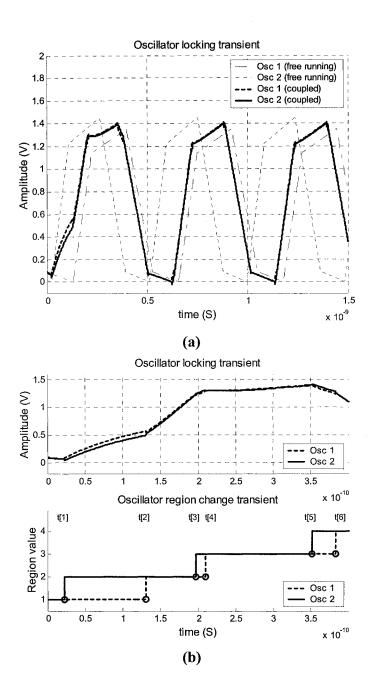

| 1.7 | <ul><li>(a) Locking transient of coupled oscillator pair using the simplified model. (b)</li><li>The first 400ps is expanded to illustrate the details of how to solve the simplified</li><li>ODEs</li></ul>                           |

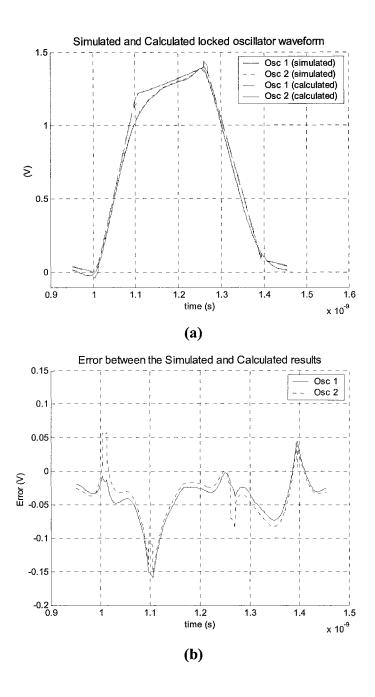

| 1.8 | Comparison between transistor level simulation and theoretical calculation using<br>the simplified model of the coupled oscillator pair. (a) Waveform of one locked<br>period. (b) Absolute error between simulation and calculation29 |

|     | Chapter 2                                                                                                                                                                                                                              |

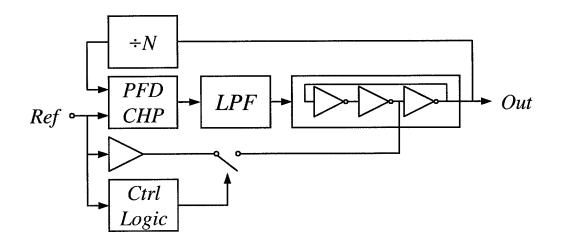

| 2.1 | Proposed top-level system block diagram                                                                                                                                                                                                |

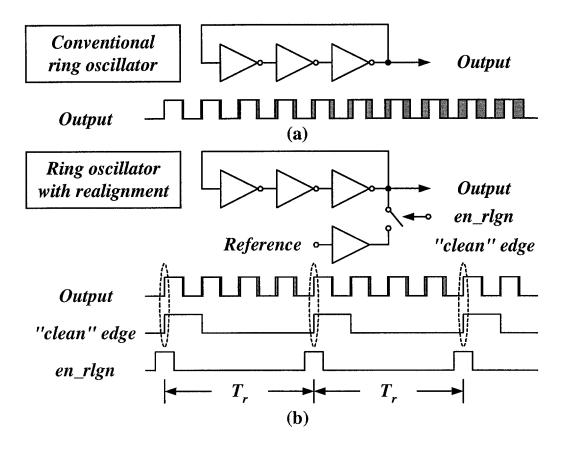

2.2 (a) Phase noise is accumulated in typical ring oscillators. (b) Periodically realigning the oscillator to a "clean" edge suppresses the phase noise

vi

|                                                 | accumulation                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

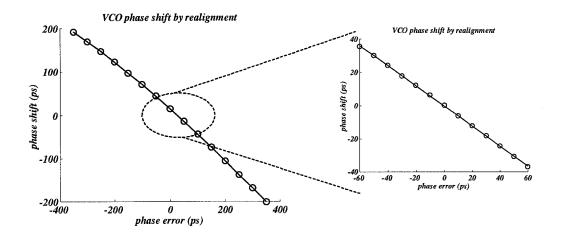

| 2.3                                             | Simulated initial phase difference versus shifted phase curve                                                                                                                                                                                                                                |

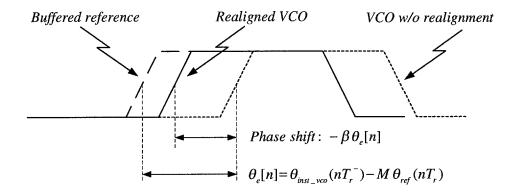

| 2.4                                             | Time domain waveform of the realignment: VCO phase shifts almost instantly and linearly to $\theta_e[n]$                                                                                                                                                                                     |

| 2.5                                             | Extra phase shift due to phase realignment42                                                                                                                                                                                                                                                 |

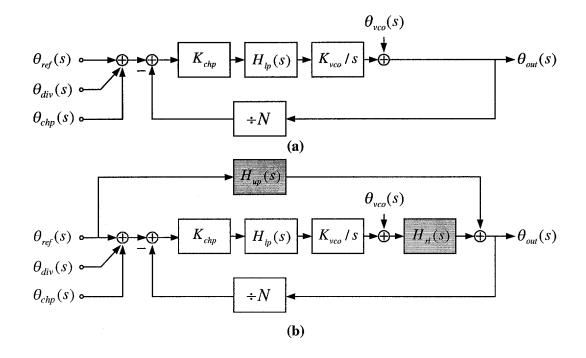

| 2.6                                             | (a) Commonly used phase noise model of a conventional integer-N PLL. (b)<br>Modified version of the phase noise model describing the RPLL                                                                                                                                                    |

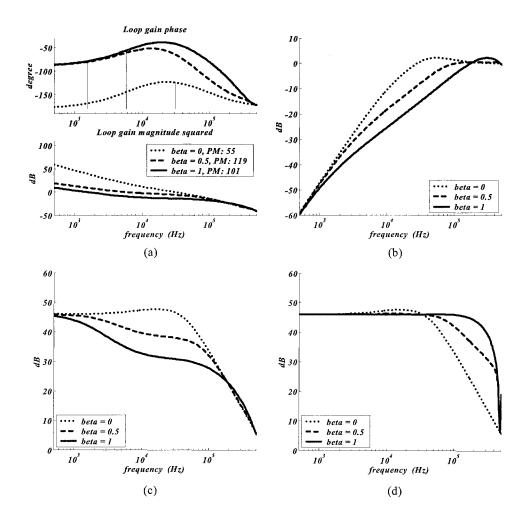

| 2.7                                             | Transfer functions of the PRPLL with different $\beta$ values. (a) Realignment increases phase margin in the loop transfer function. (b) Realignment extends the VCO noise stop band. (c) Realignment attenuates more input noise. (d) Realignment has less filtering of the reference noise |

|                                                 |                                                                                                                                                                                                                                                                                              |

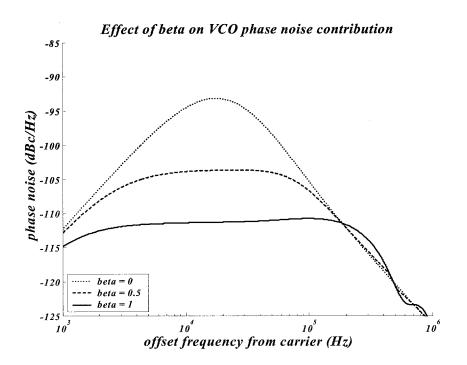

| 2.8                                             | Effect of $\beta$ on the RPLL phase noise                                                                                                                                                                                                                                                    |

| 2.8<br>2.9                                      |                                                                                                                                                                                                                                                                                              |

|                                                 | Effect of $\beta$ on the RPLL phase noise                                                                                                                                                                                                                                                    |

| 2.9                                             | Effect of $\beta$ on the RPLL phase noise                                                                                                                                                                                                                                                    |

| 2.9<br>2.10                                     | Effect of β on the RPLL phase noise                                                                                                                                                                                                                                                          |

| <ul><li>2.9</li><li>2.10</li><li>2.11</li></ul> | Effect of $\beta$ on the RPLL phase noise                                                                                                                                                                                                                                                    |

Chapter 3

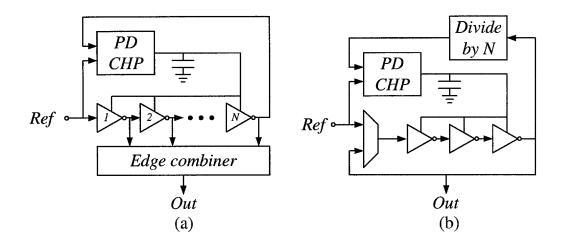

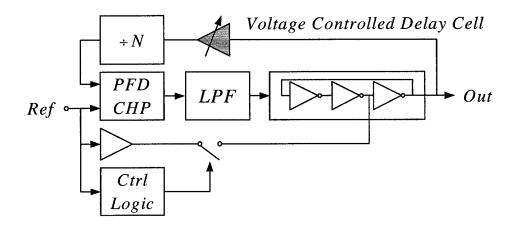

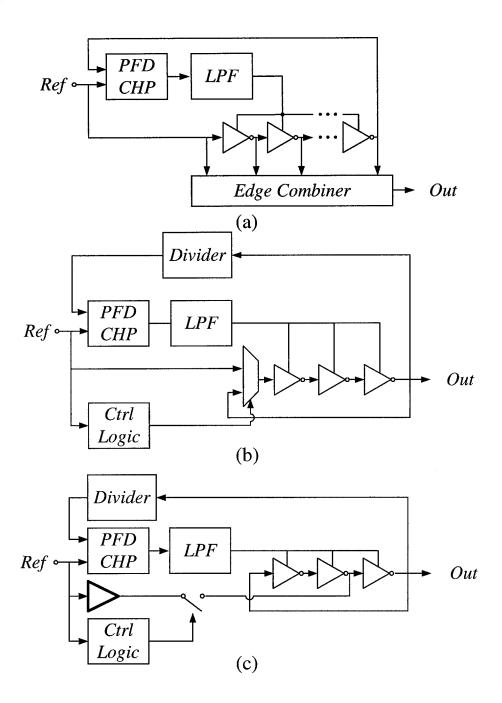

| 3.1  | Frequency synthesizers with phase realignment capability: (a) VCDL based DLL.<br>(b) Re-circulating DLL. (c) Phase realigned PLL                                                                                                                                                             |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

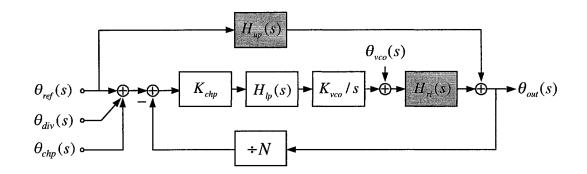

| 3.2  | Linearized model for RPLL and DLL65                                                                                                                                                                                                                                                          |

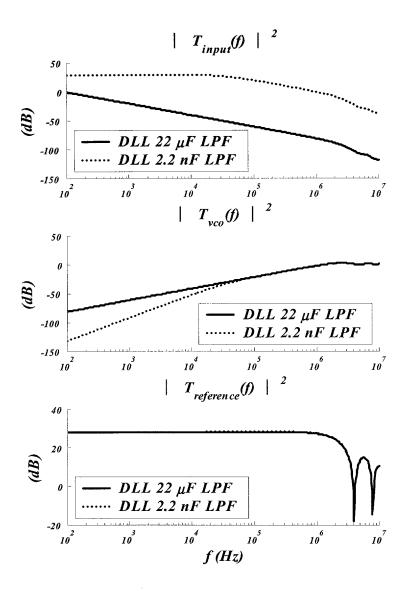

| 3.3  | Calculated noise transfer functions of the re-circulating DLL with a 1 <sup>st</sup> order loop filter using the linearized model. The bandwidth is controlled by the loop filter capacitor                                                                                                  |

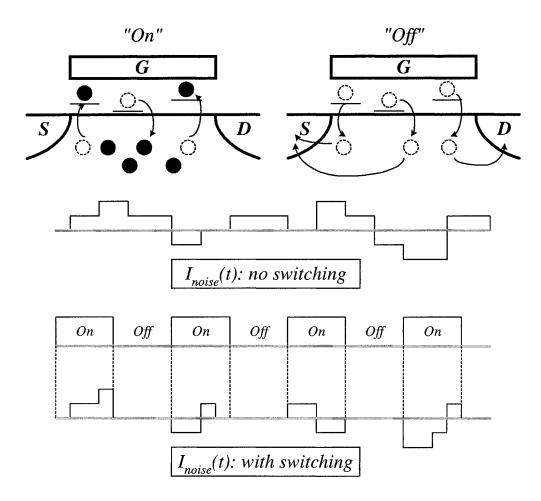

| 3.4  | Periodically switching an MOSFET between "on" and "off" resets the memory of the noise such that the long-term correlation in the noise is suppressed                                                                                                                                        |

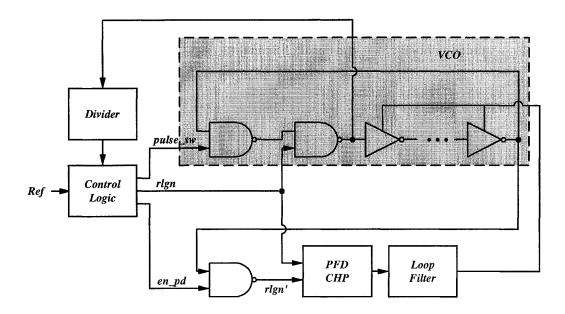

| 3.5  | Proposed re-circulating DLL block diagram. Phase realignment is implemented with two NAND gates                                                                                                                                                                                              |

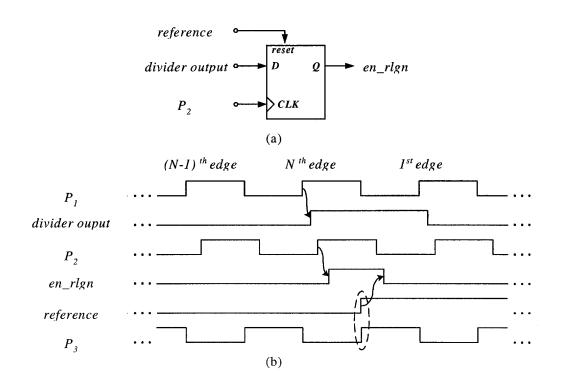

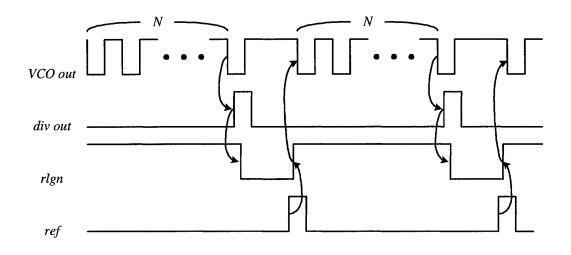

| 3.6  | Simplified timing diagram of the phase realignment control in the prototype 71                                                                                                                                                                                                               |

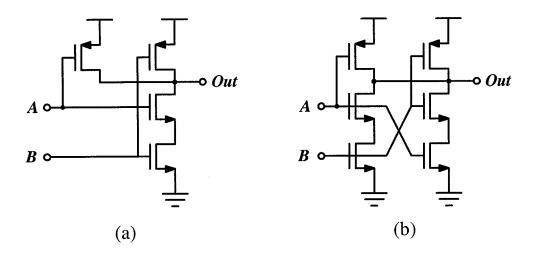

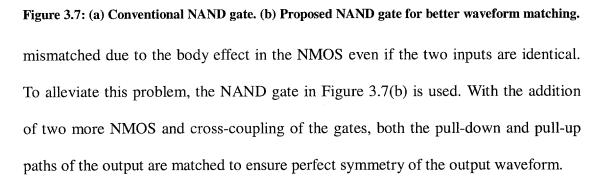

| 3.7  | (a) Conventional NAND gate. (b) Proposed NAND gate for better waveform matching                                                                                                                                                                                                              |

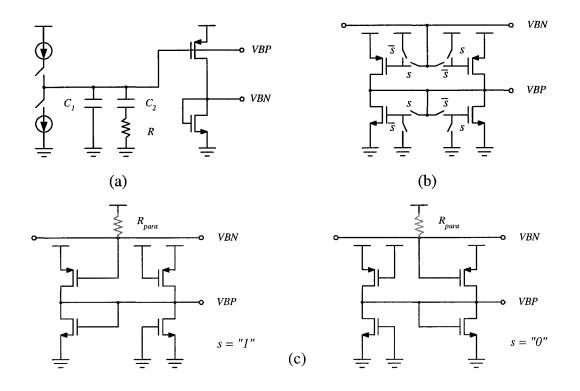

| 3.8  | (a) Typical complimentary bias generation. (b) A straightforward approach to implement switched biasing for 1/ <i>f</i> noise reduction. (c) Illustration of the detailed operation of the bias: an equivalent parasitic resistor is introduced between the loop filter and the power supply |

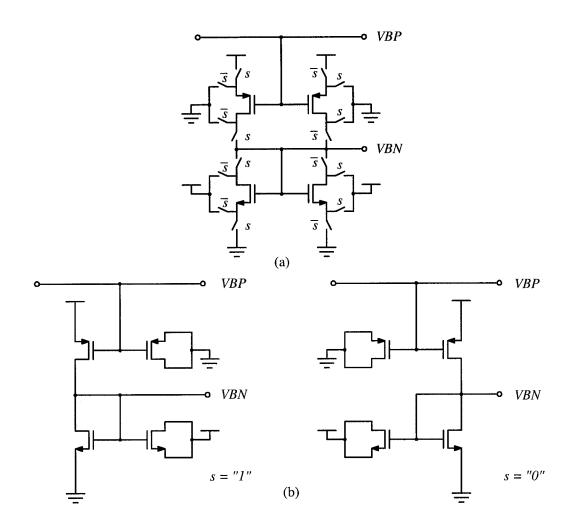

| 3.9  | Proposed bias generation with improved $1/f$ noise reduction. (a) Simplified schematic of the bias. (b) Detailed illustration of the bias operation                                                                                                                                          |

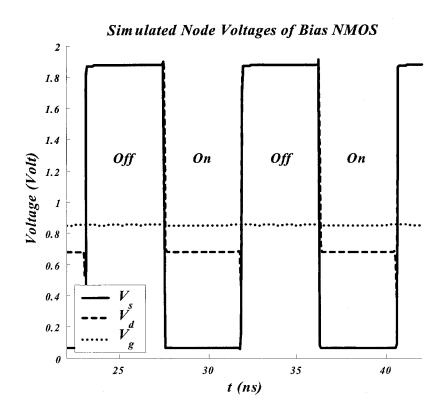

| 3.10 | Simulated node voltages of the NMOS in the bias circuitry when switched biasing is enabled                                                                                                                                                                                                   |

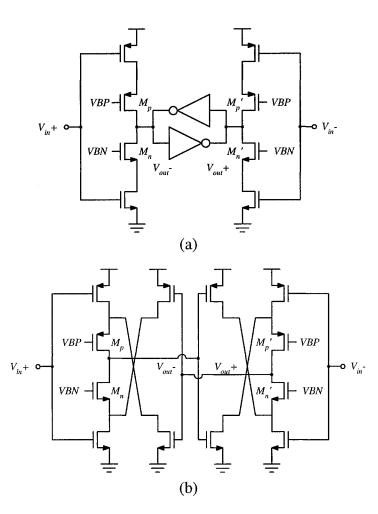

| 3.11 | Pseudo-differential voltage controlled delay cell design: (a) Conventional latch using two back-to-back inverters. (b) Improved latch for better $1/f$ noise                                                                                                                                 |

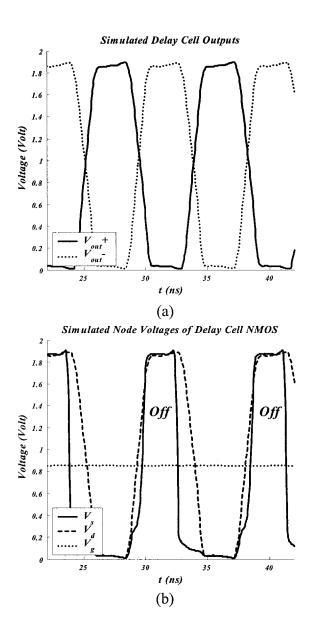

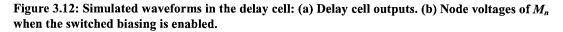

| 3.12 | Simulated waveforms in the delay cell: (a) Delay cell outputs. (b) Node voltages |

|------|----------------------------------------------------------------------------------|

|      | of $M_n$ when the switched biasing is enabled                                    |

# LIST OF TABLES

|     | Chapter 2            |    |

|-----|----------------------|----|

| 2.1 | Performance summary. | 58 |

|     |                      |    |

|     |                      |    |

|     | Chapter 3            |    |

| 3.1 | Performance summary. | 84 |

# ACKNOWLEDGEMENTS

First, I would like to thank my advisor, Ian Galton, for his friendship, guidance, support and encouragement during the course of my graduate study. His command of technical topics, engineering ingenuity, passion for new ideas and drive for perfection have always been inspiring. I have been truly fortunate to work with him. His guidance has helped me to grow as an engineer and has made my training at the ISPG group an invaluable experience.

I am grateful to Professor Daniel Wulbert of the Mathematics Department, Professor Lev Tsimring of the Institute for Nonlinear Science, Professor Bill Coles and Professor Larry Larson of the Department of Electrical and Computer Engineering, UCSD, for serving on my doctoral committee. In particular, I would like to thank Professor Bill Coles, who is my advisor during my first year at UCSD, for his guidance and encouragement. I would also like to thank Karol Previte, Carolyn Kuttner, Jim Thomas and the staff of the Department of Electrical and Computer Engineering for their help during my time at UCSD.

This work has been supported in part by the Center for Wireless Communication of UCSD.

I would like to thank the members of the ISPG group, Eric Fogleman, Sudhakar Pamarti, Jared Welz, Eric Siragusa, Ashok Swaminathan, Bill Huff, Henrik Jensen, Safy Fishov and Alan Lewis. I have been very fortunate to work with such a talented research group. Their friendship, support and wisdom have made my time at UCSD an invaluable experience.

I wish to thank my colleagues at Silicon Wave, Fari Assaderaghi, Glenn Chang,

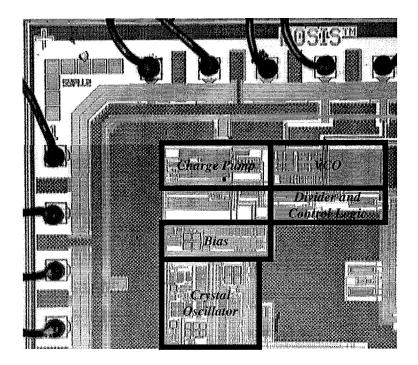

Alberto Cicalini, Matt Deig, Jean-Sebastien Gagne, Jorge Grilo, Kimihiko Imura, Lars Jansson, Curtis Ling, David Lyon, Giancarlo Milanesi, Ray Montemayor, Eric Noguchi, Kishore Seendripu and Kevin Wang. Their encouragement and support have been truly valuable to me. I would also like to thank Silicon Wave for IC fabrication and testing support.

Finally, I would like to thank my family, my father Ye Zili, my mother Tian Baoning and my wife Zhang Mai for their love and support.

This dissertation includes three chapters in which the last two chapters are intended for separate publication. Chapter 2 appeared in the December 2002 issue of the *IEEE Journal of Solid State Circuits*. The research covered in Chapter 2 was presented at the *IEEE International Solid State Circuits Conference*, February, San Francisco, California. Chapter 3 is in preparation for submission to the *IEEE Journal of Solid State Circuits*. The research covered in Chapter 3 has been submitted to the *IEEE Custom Integrated Circuits Conference* and is accepted for publication.

# VITA

| 1996           | Bachelor of Science, Bejing University, P. R. China                                                                       |

|----------------|---------------------------------------------------------------------------------------------------------------------------|

| 1996 — 1999    | Graduate Student Researcher,<br>Department of Electrical and Computer Engineering,<br>University of California, San Diego |

| 1999           | Master of Science, University of California, San Diego                                                                    |

| 1999 2003      | Graduate Student Researcher,<br>Department of Electrical and Computer Engineering,<br>University of California, San Diego |

| 2003           | Doctor of Philosophy, University of California, San Diego                                                                 |

| 2000 — Present | IC Designer,<br>Silicon Wave Inc., San Diego                                                                              |

# PUBLICATIONS

S. Ye, L. Jansson and I. Galton, "Techniques for In-band Phase Noise Suppression in Recirculating DLLs," *IEEE Journal of Solid State Circuits*, in preparation.

S. Ye, L. Jansson and I. Galton, "Techniques for In-band Phase Noise Suppression in Recirculating DLLs," *IEEE Custom Integrated Circuits Conference*, 2003, accepted for publication.

S. Ye, L. Jansson and I. Galton, "A Multiple-Crystal Interface PLL with VCO Realignment to Reduce Phase Noise", *IEEE Journal of Solid State Circuits*, Vol. 37, No. 12, pp. 1795-1803, Dec. 2002.

S. Ye, L. Jansson and I. Galton, "A Multiple-Crystal Interface PLL with VCO Realignment to Reduce Phase Noise", *IEEE International Solid State Circuits Conference, Digest of Technical Papers*, pp. 78-79, Feb. 2002.

# ABSTRACT OF THE DISSERTATION

# Phase Realignment and Phase Noise Suppression

in PLLs and DLLs

by

Sheng Ye

Doctor of Philosophy in Electrical and Computer Engineering (Electronic Circuits & Systems)

University of California, San Diego, 2003

Professor Ian Galton, Chair

Ring oscillators are widely used in clock generation for digital systems and lowperformance communication applications due to their simplicity, wide tuning range and ease of integration. However, the excessive noise in ring oscillators makes them less desirable for high-performance communication systems. This dissertation presents two applications where the advantages of ring oscillators are exploited while their disadvantages are addressed using novel system topologies. In Chapter 1, a simple, yet accurate model is presented to describe the injection locking behavior in a novel clock distribution scheme using a network of strongly coupled oscillators. The model parameters are conceptually simple and can be easily obtained through transistor-level simulation. The proposed model is capable of accurately describing the injection-locking behavior among strongly coupled ring oscillators.

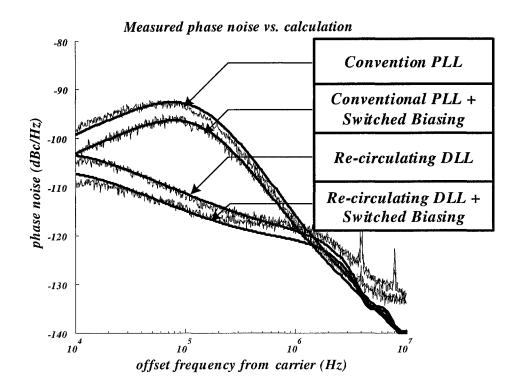

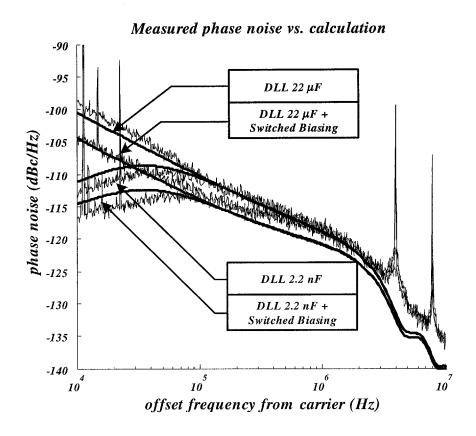

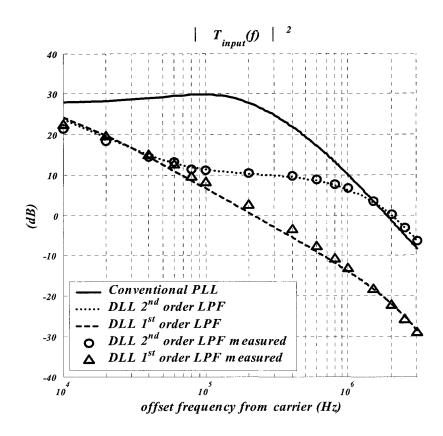

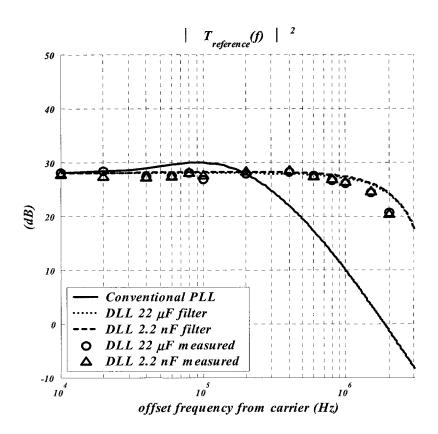

In conventional integer-N Phase-Locked Loops (PLL), the attenuation to the Voltage Controlled Oscillator (VCO) phase noise is limited by the system stability requirement, which prevents the use of ring oscillator based VCOs due to their excessive close-in phase noise. To overcome this conventional barrier, a clean reference pulse can be injected periodically into the VCO so as to reset the phase error and thereby suppress the noise memory. This technique, referred to as "phase realignment", can result in significant attenuation of the in-band phase noise. Chapter 2 presents the prototype of such a scheme and, when it is enabled, a peak spot phase noise reduction of 10 dB is observed compared with the conventional approach. In addition, a theoretical model is developed and used to improve the performance of the next-generation version of the prototype as presented in Chapter 3. Specifically, a novel ring VCO topology is developed which is not only optimized for the best phase realignment, but also designed to attenuate the 1/f noise using the switched biasing technique. A peak spot phase noise of 21.5 dB is observed when both noise attenuation schemes are enabled. Design guidelines for optimization of the loop parameters are derived from the theory and are closely supported by the measurement.

# A Simple Model for the Design of Coupled Oscillator

## **Clock Distribution Networks**

Sheng Ye, Ashok Swaminathan and Ian Galton

Abstract — This paper presents a simple, yet accurate, model to describe the injectionlocking behavior among strongly coupled oscillators applied to clock distribution in digital circuits. The model parameters are conceptually simple and, for a given transistor-level oscillator circuit, can be quickly deduced from circuit-level, e.g., SPICE, simulations. Once the model parameters are obtained, the model can be used to accurately predict the injection-locking behavior of strongly coupled copies of the oscillator with component mismatches. In addition to deriving the general model, the paper derives a simplified version of the model applicable to ring oscillators. Good agreement with transistor level simulation is observed.

## I. INTRODUCTION

In many synchronous digital circuits, copies of a periodic clock signal must be distributed to different physical locations with the same nominal phase. In practice, component mismatches in the clock distribution network cause these clock signals to exhibit relative *phase skew*, and, if sufficiently large, the phase skew can result in circuit failure. In general, as the clock rate of a digital circuit is increased, the amount of phase skew that can be tolerated without causing circuit failure decreases.

Conventional clock distribution networks distribute clock signals as propagating

waves. Each network consists of buffers and interconnect lines that distribute copies of the signal generated by a single clock source such as a PLL or crystal oscillator. The clock distribution network is designed such that the propagation delays between the clock source and the various locations to which copies of the clock signals are delivered are nominally equal. However, variations among the fabricated interconnect lines and buffer components give rise to variations among these propagation delays and, hence, relative phase skew among the distributed clock signals. The magnitude of the phase skew tends to increase with clock frequency because the period of the clock signal decreases with clock frequency while the variance of the propagation delays introduced by the clock distribution network generally does not decrease with clock frequency. Unfortunately, the primary techniques with which to reduce the variance of the propagation delays are to use wider interconnect lines and larger buffers, both of which increase circuit area and power consumption.

An alternative method to overcome this problem is to distribute clock signals in the form of standing waves instead of propagating waves. This can be done with a network of spatially distributed, strongly coupled oscillators. When the outputs of certain types of electronic oscillators with similar free-running frequencies and amplitudes are connected, they tend to lock to a common frequency through a phenomenon known as *injection locking*. Furthermore, if the oscillators are approximately matched in freerunning frequency and amplitude, they tend to lock nearly in phase thereby setting up a nearly standing wave along the interconnect lines that join the oscillators. The feasibility of this approach has been demonstrated for both discrete and integrated circuits and it has been shown that the approach can achieve significant savings in power and area

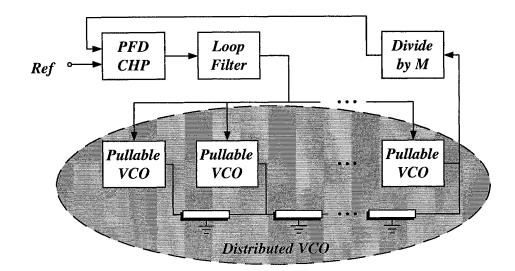

#### Figure 1.1: Clock distribution using coupled oscillator networks.

consumption relative to conventional clock distribution networks [1], [2].

Each oscillator can be implemented as a voltage controlled oscillator (VCO). When their inputs and outputs, respectively, are connected via metal interconnect lines, multiple spatially distributed, nominally matched VCOs tend to behave as a single VCO; the outputs of the individual VCOs achieve the same frequency and nearly the same phase, and the frequency can be locked to a reference frequency using a conventional PLL as shown in Figure 1.1. An added benefit of this approach is that it naturally aligns the distributed clock signals not only with each other, but also with the reference frequency signal, which makes it possible for different integrated circuits to generate internal high-speed clocks that are synchronized with each other through an externally supplied reference frequency signal. This is difficult to accomplish with conventional clock distribution networks because the average propagation delay though a given clock distribution network generally depends upon the details of the integrated circuit in which

it resides [3].

The injection-locking behavior among coupled oscillators is widely observed and, in particular, is easily obtained both in physical measurement and transistor level SPICE simulation for electrical oscillators. Research in this area remains active to exploit this phenomenon such as [1], [2] and [4]. In order to precisely characterize the behavior of the injection locking, it is critical to have an accurate model that is capable of predicting both the phase and amplitude response of the oscillator when it is coupled to other oscillators. The linear and time-varying (LTV) oscillator model presented by Hajimiri and Lee [5] [6] provides a very good framework for the construction of such a model. However, although the Hajimiri-Lee model is sufficiently accurate in phase noise prediction, it needs to be extended to describe the injection-locking behavior, which is inherently nonlinear. In recent findings by Tanaka et al. [7], the Hajimiri-Lee model is extended to describe the excess phase response of weakly coupled oscillators where the amplitude response of the oscillator is ignored. Averaging method is used in the analysis of the weak coupling and design guidelines are derived. However, when the coupling strength increases in the case of a practical IC, the averaging method fails to apply. In addition, as demonstrated below, both the phase and amplitude response of the oscillator affect its injection-locking behavior in strongly coupled oscillators.

This paper presents a simple, yet accurate, model that is capable of analyzing strongly coupled oscillators. The proposed model is nonlinear and is an extension to the Hajimiri-Lee model with characterization of both the phase and amplitude response of the oscillator. In particular, the phase response model is equivalent to the model presented in [7], although it was developed by the authors independently. On the other hand, the

4

amplitude response model is an extension to that presented in [6]. Specifically, the underlying relationship between the phase and amplitude response is analyzed quantitatively in the special case of ring oscillators. As presented in section II, the model parameters are conceptually simple and, for a given transistor-level oscillator circuit, can be quickly deduced from circuit simulations. In section III, a simplified version of the model applicable to ring oscillators, which are widely used for to generate clock signals for digital circuits, is presented. Analysis of the coupled ring oscillators using the proposed model is presented in section IV, where the model accurately predicts the injection-locking behavior of strongly coupled copies of the oscillator with component mismatches. In section V, the oscillator model is simplified even further. Despite its simplicity, the salient property of the coupled oscillator is still retained.

## II. THE GENERAL OSCILLATOR MODEL

This section presents the most general form of the oscillator model. The model is an extension of that originally proposed by Hajimiri and Lee as well as the model presented in [7]. In particular, although the phase response model is equivalent to the model presented in [7], it is rigorously derived here to be consistent with the amplitude response model presented later.

### A. Description of the General Oscillator Model

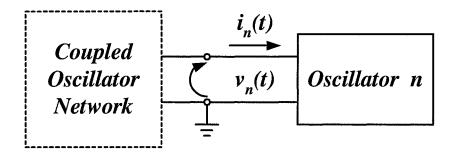

The  $n^{\text{th}}$  oscillator in a network of coupled oscillators can be viewed as a nonlinear one-port device with a voltage,  $v_n(t)$ , and a current,  $i_n(t)$ , as shown in. If the oscillator is removed from the network, it is said to be *free-running*. In this case  $i_n(t)$

5

Figure 1.2: Each oscillator in the coupled oscillator network is modeled as a one-port device.

becomes zero, and  $v_n(t)$  settles into a *free-running oscillation*. In practice, even nominally identical oscillators have significantly different free running oscillations because of component variations introduced during fabrication. However, under a surprisingly wide range of conditions, coupled oscillators exchange current in such a fashion that they *lock in frequency*. That is, they settle to a state wherein the oscillator voltages,  $v_n(t)$ , for all *n* become periodic with a common minimum period.

A general representation of the voltage waveform of the  $n^{\text{th}}$  oscillator is

$$v_n(t) = f_n(\omega_n t + \phi_n(t)) + \Delta A_n(t), \tag{1}$$

where  $f_n(\cdot)$  is a  $2\pi$ —periodic function that represents the free-running oscillation amplitude,  $\omega_n$  is the free-running oscillation frequency, and  $\phi_n(t)$  and  $\Delta A_n(t)$  are timevarying functions referred to as the *excess phase* and *excess amplitude*, respectively.<sup>†</sup>

<sup>&</sup>lt;sup>†</sup> Note that (1) is equivalent to the commonly used expression  $v_n(t) = A_n(t) f_n(\omega_n t + \phi_n(t))$  where  $A_n(t)$  is a time-varying amplitude function, but the form of (1) is more convenient for the purposes of this paper.

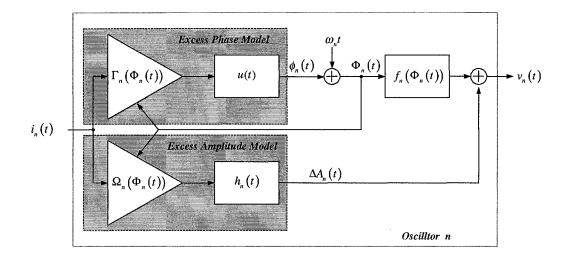

#### Figure 1.3: Block diagram of the proposed oscillator model.

Coupled oscillators lock in frequency by exchanging current. For each oscillator it follows that the oscillation waveform must depend upon the current sourced or sunk by the oscillator. In (1) this occurs most generally when the excess phase,  $\phi_n(t)$ , and the excess amplitude,  $\Delta A_n(t)$ , depend upon  $i_n(t)$ . Therefore, in order to characterize the frequency locking behavior of an oscillator, it is sufficient to quantify how the excess phase and excess amplitude depend upon the current. In principle, this could be done by analyzing each oscillator at the circuit level. However, the analysis would be prohibitively complicated to perform by hand, and, therefore, would most likely involve extensive circuit simulation.

Despite the accuracy of circuit simulations, it is still desirable to have a simple signal processing level model that describes the salient properties of both the excess phase and excess amplitude in terms of the oscillator current for a wide range of oscillator configurations. As shown below, the oscillator model proposed herein is such a model. Figure 1.3 shows the signal processing equivalent block diagram of the proposed single oscillator model. The model contains two sub-models: the *excess phase model* and the *excess amplitude model*. Both contain a variable gain element followed by a linear time invariant (LTI) signal processing block. In the excess phase model, the input current is multiplied by a function,  $\Gamma_n(\cdot)$ , called the *phase sensitivity function* (PSF), and the result is integrated to produce the excess phase. The PSF is evaluated at the *absolute oscillator phase*:  $\Phi_n(t) = \omega_n t + \phi_n(t)$ . In the excess amplitude model, the input current is multiplied by a function,  $\Omega_n(\cdot)$ , called the *amplitude sensitivity function* (ASF), and the result is passed through an LTI filter with impulse response  $h_n(t)$ , i.e. transfer function  $H_n(s)$ , to produce the excess amplitude. As in the case of the PSF, the ASF is evaluated at the absolute at the absolute oscillator phase. Both the PSF and the ASF are periodic with  $2\pi$ .

For a given oscillator circuit, the oscillator model completely specifies the oscillator voltage as a function of the oscillator current once the *model parameters*,  $f_n(\cdot)$ ,  $\omega_n$ ,  $\Gamma_n(\cdot)$ ,  $\Omega_n(\cdot)$ , and  $H_n(s)$  are known. As demonstrated in Section III for the case of ring oscillators, the model parameters can be extracted from relatively simple transistor-level SPICE simulations on individual oscillators.

### B. Motivation Behind the General Oscillator Model

As mentioned above, the model presented in this paper is an extension of the Hajimiri-Lee model presented in [5]. The Hajimiri-Lee model is based on the observation that for a large variety of oscillators the excess phase and excess amplitude depend not only on the oscillator's input current,  $i_n(t)$ , but also on the absolute oscillator phase. Therefore, the model allows for these dependencies to be time varying. However,

it makes the approximation that the excess phase depends linearly on the oscillator's input current. In [5] the model is used to predict oscillator phase noise by representing all the circuit noise sources in a given oscillator circuit as an equivalent input current source driving a noiseless version of the oscillator. In such cases, the input current is usually modeled as a small-amplitude, zero-mean, random process for which the linearity approximation turns out to be reasonable. However, in networks of coupled oscillators the oscillator input currents tend to be deterministic periodic functions with frequencies that differ from the free-running periods of the individual oscillators, and in such cases it turns out that the linearity approximation is not valid. The extension of the Hajimiri-Lee model presented herein overcomes this problem. In the following, the assumptions that underlie the new model and the relationship between the new model and the Hajimiri-Lee model are explained in detail.

If a narrow pulse of current is applied to the terminals of an otherwise freerunning oscillator, an excess phase change can be observed several cycles later when the oscillator settles back to a free-running oscillation. Provided the current pulse has a sufficiently small magnitude and duration, the excess phase change tends to be proportional to the delivered charge where the proportionality factor is a periodic function of the absolute oscillator phase. This behavior is represented in both the Hajimiri-Lee model and the new model by assuming the excess phase abruptly steps to and remains at the value determined by the proportionality factor corresponding to the absolute oscillator phase at the time the current pulse is applied. Therefore, if a rectangular current pulse of magnitude  $I_p$  with a duration of  $\Delta t$  occurs at time t, in the limit as  $\Delta t \rightarrow 0$  the excess phase change can be written as

$$\phi_n(t+\Delta t) - \phi_n(t) = \Gamma_n(\omega_n t + \phi_n(t)) I_\nu \Delta t, \qquad (2)$$

where  $\Gamma_n(\cdot)$ , denoted as the PSF in the model, is the proportionality factor.

Given that any physically realizable input current waveform can be approximated with arbitrary precision as a sum of weighted and time-shifted sufficiently narrow rectangular current pulses, the behavior described by (2) can be generalized to arbitrary physically realizable input current waveforms as

$$\phi_n(t) - \phi_n(t_0) = \int_{t_0}^t \Gamma_n\left(\omega_n \tau + \phi_n(\tau)\right) i_n(\tau) d\tau, \qquad (3)$$

where  $\phi_n(t_0)$  is the initial excess phase at time  $t_0$ . The excess phase model shown in Figure 1.3 is a block diagram representation of (3). Throughout the remainder of this paper, it is assumed that  $i_n(t)$  and  $\Gamma_n(t)$  are both piecewise continuous with at most a finite number of discontinuities, so it follows from (3) that  $\phi_n(t)$  is continuous. The presence of  $\phi_n(\tau)$  in the integrand of (3) gives rise to the nonlinear relationship between the excess phase and the input current mentioned above. This term is approximated as zero in the Hajimiri-Lee model so as to eliminate the nonlinearity. It should be noted that (3) is equivalent to the excess phase model as reported in [7].

In general, the excess amplitude of the oscillator also responds to an applied narrow current pulse in a fashion that depends upon the absolute phase of the oscillator. However, unlike the excess phase response where the phase change persists indefinitely, the excess amplitude tends to exhibit a transient response that settles back to zero in time due to the amplitude control mechanisms present in practical oscillators. This behavior is idealized as follows: the input current pulse is scaled by the ASF evaluated at the oscillator phase, i.e.,  $\Omega_n(\Phi_n(t))$ , and the result is passed though an LTI filter. Generalizing this to arbitrary input current waveforms gives

$$\Delta A_n(t) = \int_{-\infty}^{\infty} \Omega_n(\omega_n \tau + \phi_n(\tau)) i_n(\tau) h_n(t-\tau) d\tau$$

(4)

where  $h_n(t)$  is the impulse response as shown in Figure 1.3. The excess amplitude model shown in Figure 1.3 is a block diagram representation of (4). As in the case of the PSF, the ASF is assumed to be piecewise continuous with at most a finite number of discontinuities. In the Hajimiri-Lee model in [6], the amplitude response of both high-Q oscillators such as a LC oscillator and low-Q oscillators such as a ring oscillator are presented and an *amplitude impulse sensitivity function*, which is similar to the *phase impulse sensitivity function*, is introduced. Unlike the extensive discussion on how to obtain the *phase impulse sensitivity function*, the procedure to obtain the *amplitude impulse sensitivity function* is not discussed because the AM noise is not the dominant source of phase noise in most cases. More importantly, the amplitude response model in [6] is still LTV, making it unsuitable for injection-locking analysis.

In weakly coupled oscillators, ignoring the amplitude response seems reasonable to simplify the calculation as demonstrated in [7]. However, when the oscillators are strongly coupled, an accurate amplitude response model is critical in describing the oscillators' behavior as illustrated by the following example. Suppose the outputs of two oscillators with different voltage swing are coupled together by a zero-Ohm resistor and they lock in frequency, the output voltages of the two oscillators are identical because they are shorted. However, in the absence of the amplitude response model, the calculated waveforms of the oscillators can only warp using the phase response model, making it impossible to match the physical results.

## III. RING OSCILLATOR MODEL

In this section, two additional assumptions are made regarding the behavior of oscillators so as to simplify the problems of extracting the model parameters from circuit simulations and applying the oscillator model to predict the behavior of networks of coupled oscillators. Circuit simulations indicate that the assumptions are valid at least for the case of ring oscillators, which are widely used to generate clock signals in digital circuits. Although the assumptions restrict the oscillator model somewhat, the resulting simplifications greatly ease the application of the model to the analysis of coupled oscillator circuits. Furthermore, as demonstrated in Section IV the model is remarkably accurate in predicting the behavior of coupled ring oscillators.

#### A. Ring Oscillator Assumptions

The first assumption is that if a narrow pulse of current is applied to the terminals of an otherwise free-running oscillator, then the oscillator voltage,  $v_n(t)$ , abruptly changes from its free-running value by  $\Delta Q/C_n$  where  $\Delta Q$  is the total charge in the current pulse, and  $C_n$  is a constant capacitance value. The only significant restriction imposed by this assumption is that  $C_n$  is assumed to be constant regardless of the absolute phase of the oscillator. In practice, the capacitance will have some time-varying components arising from the non-linear capacitances presented by the transistors within the oscillator circuit, but as demonstrated in Section IV the model produces extremely accurate results despite the approximation that the capacitance is constant. The second assumption is that the LTI system in the excess amplitude model is well approximated by a single-pole system. Thus, its impulse response is

$$h_n(t) = u(t) \frac{1}{C_n} e^{-t/\tau_n},$$

(5)

where u(t) is the unit step function, and  $\tau_n$  is a constant referred to as the *excess amplitude time-constant*. The assumption is analogous to the dominant pole assumption often made in amplifier circuit analysis. In general, the assumption is valid to the extent that one pole of  $H_n(s)$ , i.e., the pole at  $s = -1/(2\pi\tau_n)$ , has a magnitude much smaller than that of every zero and every other pole of  $H_n(s)$ . This assumption is consistent with the assumption in the Hajimiri-Lee model [6]. However, the dependence on the absolute phase allows the proposed model to characterize the injection-locking behavior.

There are two significant benefits that arise from making these assumptions in terms of simplifying the extraction of the model parameters from circuit simulations. One is that the problem of determining a function, namely  $H_n(s)$  in the excess amplitude model, reduces to that of determining a single number, namely  $\tau_n$ . The other is that the assumptions cause the ASF to be a function of the PSF, the free-running oscillation amplitude, and  $C_n$ , so once these model parameters are known there is no need to separately extract the ASF.

### B. Derivation of the ASF Expression

As presented above, the oscillator model describes the relationship between the oscillator voltage and current. At any given time, this relationship depends upon the absolute oscillator phase, the excess phase, and the excess amplitude. The ring oscillator

assumptions made above provide further relationships between the oscillator voltage and current that are used below in conjunction with the general model structure to derive the ASF as a function of the PSF, the free-running oscillation amplitude, and  $C_n$ .

Suppose a rectangular current pulse of magnitude  $I_p$  with a duration of  $\Delta t$  is applied to an otherwise free-running oscillator at time  $t = t_1$ . Prior to the time of the current pulse,  $\phi_n(t)$  and  $\Delta A_n(t)$  are both zero, so (1) reduces to  $v_n(t) = f_n(\omega_n t)$ . Therefore, the first ring oscillator assumption implies that

$$v_n(t_1 + \Delta t) - v_n(t_1) \approx f_n\left(\omega_n(t_1 + \Delta t)\right) - f_n(t_1) + \frac{I_p \Delta t}{C_n},\tag{6}$$

where the approximation becomes an equality as  $\Delta t \rightarrow 0$ . Dividing (6) by  $\Delta t$  and taking the limit as  $\Delta t \rightarrow 0$  results in

$$v'_{n}(t_{1}^{+}) = \omega_{n} f'_{n}(\omega_{n} t_{1}^{+}) + \frac{I}{C_{n}},$$

(7)

where  $t_1^+$  is the instant immediately following the current pulse.

This result is a direct consequence of the first ring oscillator assumption, but is not a consequence of the general oscillator model presented in Section II. However, the general oscillator model can also be used to obtain an expression for the derivative of the oscillator voltage at the instant immediately following the current pulse, and this expression must equate to (7).

Differentiating (3) with respect to time gives

$$\phi'_n(t) = \Gamma_n \left( \omega_n t + \phi_n(t) \right) i_n(t).$$

(8)

Substituting (5) into the derivative of (4) gives

$$\Delta A'_n(t) = \Omega_n \left( \omega_n t + \phi_n(t) \right) \frac{i_n(t)}{C_n} - \frac{\Delta A_n(t)}{\tau_n}.$$

(9)

15

Differentiating (1), substituting (8) and (9) into the result, and evaluating at time  $t = t_1^+$  yields

$$v'_{n}(t_{1}^{+}) = \left(\omega_{n} + \Gamma_{n}\left(\omega_{n}t_{1}^{+}\right)I\right)f'_{n}(\omega_{n}t_{1}^{+}) + \Omega_{n}\left(\omega_{n}t_{1}^{+}\right)\frac{I}{C_{n}}.$$

(10)

Equating (7) and (10), and solving for  $\Omega_n(\omega_n t_1^+)$  gives

$$\Omega_n(\omega_n t_1^+) = 1 - C_n \Gamma_n(\omega_n t_1^+) f_n'(\omega_n t_1^+).$$

(11)

The choice of  $t_1$ , the time of the current step in the derivation leading to (11), was arbitrary, so (11) must be valid for any value of  $\theta = \omega_n t_1$ . This implies the following general expression for the ASF

$$\Omega_n(\theta) = 1 - C_n \Gamma_n(\theta) f'_n(\theta).$$

(12)

It is interesting to compare  $\Gamma_n(\cdot)$  and  $\Omega_n(\cdot)$  quantitatively. When the magnitude of  $\Gamma_n(\cdot)$  peaks, usually the magnitude of  $f'_n(\cdot)$  peaks as well, so the magnitude of  $\Omega_n(\cdot)$  is minimized. When the magnitude of  $\Gamma_n(\cdot)$  approaches zero,  $\Omega_n(\cdot)$  approaches one. This result is consistent with the observations in [5]: when a current impulse is applied to a node of an oscillator when the node voltage is at its peak, the impulse has most impact on the amplitude change. Conversely, if the impulse is applied at the zero crossing of the node voltage, it has the most impact on the phase shift.

## C. Model Parameter Extraction from SPICE Simulations

As described in Section II, the model parameters  $f_n(\cdot)$ ,  $\omega_n$ ,  $\Gamma_n(\cdot)$ ,  $\Omega_n(\cdot)$ , and  $H_n(s)$ must be determined in order to apply the model to a specific oscillator circuit. Although all these parameters can be extracted directly from transistor-level simulations of the oscillator circuit in question, the two ring oscillator assumptions made above make it necessary only to extract  $f_n(\cdot)$ ,  $\omega_n$ ,  $\Gamma_n(\cdot)$ ,  $C_n$ , and  $\tau_n$  from transistor-level simulations. Once these parameters are known, the transfer function,  $H_n(s)$ , can be calculated using the Laplace Transform of (5), and  $\Omega_n(\cdot)$  can be calculated using (12).

Closed form expressions for  $f_n(\cdot)$  and  $\Gamma_n(\cdot)$  can not be easily determined from circuit simulations. Fortunately, for the purposes of this paper it is sufficient to represent them each by a vector of their samples taken at uniformly spaced sampling instants over one oscillation period, and such vectors are relatively easy to obtain via circuit simulations. Issues associated with the choice of the sampling interval are presented in the next section.

The model parameters  $f_n(\cdot)$  and  $\omega_n$  can be determined by direct simulation of a single free-running instance of the oscillator circuit in question. Once the initial simulation startup transients have settled out, the free-running oscillation period, and hence its reciprocal,  $\omega_n$ , can be observed from the oscillator voltage waveform, and  $f_n(\cdot)$  is given by the oscillator waveform over one period. Similarly, the derivative of  $f_n(\cdot)$ , which is subsequently used to calculate  $\Omega_n(\cdot)$ , can be determined by direct simulation of a single free-running instance of the oscillator circuit.

A simple method with which to obtain  $\Gamma_n(\cdot)$  is to simulate two identical copies of

the oscillator with the same initial conditions as follows. One of the oscillators is left free-running, and a narrow rectangular current pulse is applied to the other oscillator, so a phase difference,  $\Delta \phi$ , between the two oscillators is induced. After several oscillator periods following the applied pulse, the excess amplitude of the pulsed oscillator settles back to zero at which time the phase difference can be observed from the simulated oscillator output voltages. Just prior to the current pulse, the excess phase,  $\phi_n(t)$ , of the about-to-be-pulsed oscillator is zero, because at that point the oscillator is still free running, so it follows from (2) that

$$\Gamma_n(\omega_n t_1) \cong \frac{\Delta \phi}{I \Delta t},\tag{13}$$

where  $t_1$  is the time at which the current pulse is applied, *I* is the amplitude of the current pulse, and  $\Delta t$  is the duration of the current pulse. The accuracy of (13) increases as the pulse width,  $\Delta t$ , decreases (provided the pulse width is not so small compared to the stepsize of the circuit simulator that significant simulation errors occur). Thus, a sample of the PSF at any point  $\theta = \omega_n t_1$  can be accurately estimated from a simulation of two identical copies of the oscillator in question by applying the pulse at time  $t_1$ , measuring the resulting  $\Delta \phi$ , and applying (13).

A similar simulation can be used to obtain the excess amplitude time constant,  $\tau_n$ . Again starting with two identical copies of the oscillator circuit with the same initial conditions, a narrow rectangular current pulse can be applied to one of the oscillators at a point in time where the PSF is zero. The difference between the simulated waveforms of the two oscillators immediately following the applied pulse can be approximated as an exponentially decaying function from which the time constant can be measured.

To obtain  $C_n$ , a small rectangular current pulse of magnitude  $I_p$  with a duration of  $\Delta t$  can be applied to the simulated oscillator circuit, and the difference between the oscillator voltage just after the pulse,  $v_n(t_1 + \Delta t)$ , and the oscillator voltage just prior to the pulse,  $v_n(t_1)$ , can be observed. With these observed values, it follows from (6) that  $C_n$  can be calculated using

$$C_n \approx \frac{I_p \Delta t}{\nu_n(t_1 + \Delta t) - \nu_n(t_1) - f_n(\omega_n(t_1 + \Delta t)) + f_n(t_1)}.$$

(14)

## IV. COUPLED RING OSCILLATORS

To determine how coupled oscillators interact, it is necessary to derive expressions for the currents exchanged by the coupled oscillators as a function of the oscillator model parameters. Once these expressions are known, they can be combined with the differential forms of the model equations, i.e., (8) and (9), to generate a system of ordinary differential equations (ODEs) that describe the excess phase and excess amplitude of each oscillator. As demonstrated in this section, the ODEs can be solved numerically to obtain results that closely match direct circuit simulations, or they can be simplified via approximations to facilitate hand analysis.

For illustration purposes, a pair of coupled oscillators is considered throughout this section. In practice, coupled oscillators are connected through metal interconnect lines on integrated circuits. The interconnect lines present resistance, and at high frequencies can be modeled as lossy transmission lines. Although the voltage and current

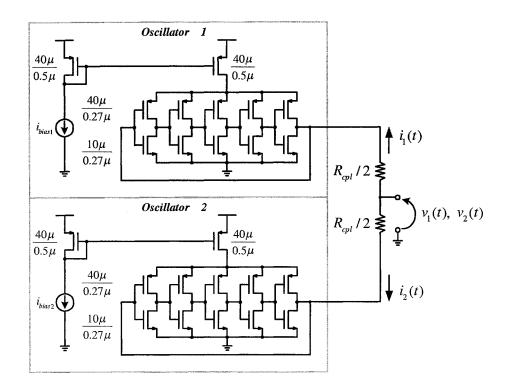

Figure 1.4: Schematics of the resistively coupled oscillator pair.

relationship between the two ends of the transmission line can be easily obtained using known techniques, the interconnect line is modeled as a resistor to simplify the derivation in the following analysis.

## A. Derivation of the Differential Equations

A circuit diagram of the pair of coupled oscillators analyzed below is shown in Figure 1.4. Each oscillator is a five-stage ring oscillator with transistor sizes as noted in the figure. The tail currents are intentionally mismatched to represent rather extreme process variations. The oscillators are designed for the TSMC 0.18-µm CMOS process. Circuit simulations using BSIM3V3 models for this process indicate that the free running frequencies of the two oscillators are 1.908 GHz and 2.053 GHz, respectively.

In practice, the resistance of a several hundreds microns long, minimum width interconnect line is usually in the tens of Ohms. In this particular simulation, the oscillators are connected to each other though a 20- $\Omega$  resistor to model a 200- $\mu$ m long, minimum width interconnect. They are also connected (implicitly) through a low impedance ground line. In practice, ground connections are implemented with wide metal lines so they tend to have low resistance. Therefore in this case the ground connections are approximated as zero. Transistor level simulation indicates the two oscillators lock to a common frequency of 1.986 GHz.

Since the coupling resistor is small, it is convenient to approximate the resistance as zero so the outputs of the two oscillators are shorted. As shown in Figure 1.4, the top and bottom oscillators are denoted as Oscillator 1 and Oscillator 2, respectively. Because of the above approximation, Oscillator 1 and Oscillator 2 are directly connected, which implies that their voltages are equal and their currents have equal magnitude but opposite signs. That is,  $v_1(t) = v_2(t)$  and  $i_1(t) = -i_2(t)$ . Once the values of  $v_1(t)$ ,  $v_2(t)$ ,  $i_1(t)$  and  $i_2(t)$  are calculated as shown below, it follows that the voltages at the actual outputs of the top and bottom ring oscillators in Figure 1.4 are  $v_2(t)+i_2(t)\cdot(10\Omega)$  and  $v_2(t)-i_2(t)\cdot(10\Omega)$ , respectively. Since the coupling resistor is very small, the error due to the above approximation is neglected.

Differentiating (1) and substituting (8), (9), and (12) into the result yields

$$v'_n(t) = \omega_n f'_n(\omega_n t + \phi_n(t)) + \frac{i_n(t)}{C_n} - \frac{\Delta A_n(t)}{\tau_n}.$$

(15)

Figure 1.5: Comparison between transistor level simulation and theoretical calculation of the coupled oscillator pair. (a) Waveform of one locked period. (b) Absolute error between simulation and calculation.

Given that  $v_1(t)$  and  $v_2(t)$  are equal, it follows that their derivatives are also equal. Thus, the right sides of the two equations given by (15) with n = 1,2 are equal. Solving for  $i_1(t) = -i_2(t)$  gives

$$i_{1}(t) = -i_{2}(t) = \frac{C_{1}C_{2}}{C_{1} + C_{2}} \left[ \omega_{2}f_{2}'(\omega_{2}t + \phi_{2}(t)) - \omega_{1}f_{1}'(\omega_{1}t + \phi_{1}(t)) - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}} \right]$$

(16)

Substituting (16) into (8) and (9) yields

$$\Phi_{1}'(t) = \frac{C_{1}C_{2}}{C_{1}+C_{2}}\Gamma_{1}(\Phi_{1}(t))\left[\omega_{2}f_{2}'(\Phi_{2}(t)) - \omega_{1}f_{1}'(\Phi_{1}(t)) - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}}\right] + \omega_{1}, \quad (17)$$

$$\Phi_{2}'(t) = -\frac{C_{1}C_{2}}{C_{1}+C_{2}}\Gamma_{2}\left(\Phi_{2}(t)\right)\left[\omega_{2}f_{2}'\left(\Phi_{2}(t)\right) - \omega_{1}f_{1}'\left(\Phi_{1}(t)\right) - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}}\right] + \omega_{2}, \quad (18)$$

$$\Delta A_{1}'(t) = -\frac{\Delta A_{1}(t)}{\tau_{1}} + \frac{C_{2}}{C_{1} + C_{2}} \Omega_{1}(\Phi_{1}(t)) \bigg[ \omega_{2} f_{2}'(\Phi_{2}(t)) - \omega_{1} f_{1}'(\Phi_{1}(t)) - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}} \bigg],$$

(19)

and

$$\Delta A_{2}'(t) = -\frac{\Delta A_{2}(t)}{\tau_{2}} - \frac{C_{1}}{C_{1} + C_{2}} \Omega_{2} \left( \Phi_{2}(t) \right) \left[ \omega_{2} f_{2}' \left( \Phi_{2}(t) \right) - \omega_{1} f_{1}' \left( \Phi_{1}(t) \right) - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}} \right], (20)$$

where  $\Phi_n(t) = \omega_n t + \phi_n(t)$ , n = 1, 2, are the absolute phases of the two oscillators.

For demonstration purposes, equations (17) to (20) are numerically solved using Euler's method [8] and compared with transistor-level SPICE simulation. A uniform step size of 0.2 ps is used in the numerical solution. Figure 1.5(a) shows the calculated waveform in one locked period of oscillator 1 and 2 in comparison with the simulation. Figure 1.5(b) shows the error between the calculation and the simulation. The calculated locked frequency is 1.987 GHz, which is within 0.1% error of the transistor-level simulation result. In this particular example, the choice of the oscillator is for demonstration purpose only. Although not shown in this paper, pair coupled oscillators implemented using other processes that are running at 1 GHz and 300 MHz have also

been simulated. When the theoretical model is applied to compare with the transistorlevel simulation, similar accuracy has been observed.

## V. SIMPLIFIED OSCILLATOR MODEL

The accuracy of the numerical solution in the previous section confirms the validity of the proposed model. Unfortunately, the interaction between the pair coupled oscillators is concealed by the complicated calculations. Therefore it is desirable to have a further simplified model to gain more understanding into the behavior of coupled oscillators. Such a simplified model is presented in this section.

Since the modeling parameters  $f_n(\cdot)$ ,  $\Gamma_n(\cdot)$  and  $\Omega_n(\cdot)$  are derived from simulations, they have no analytical forms. In the following analysis, these parameters are approximated as piece-wise linear curves for simplicity. As shown in Figure 1.6(a), one period of the function  $f_n(\cdot)$  is divided into four regions. Within each region, the waveform is approximated as a straight line. For ease of notation, these four regions are expressed as region 1 (the rising edge), region 2, region 3 (the falling edge) and region 4, respectively. The slope in region 1 of the approximation is chosen to be equal to the slope in the middle of the simulated waveform's rising edge, while the slope in region 3 of the approximation is chosen to be equal to the slope in the middle of the simulated waveform's falling edge. The boundaries between regions are chosen to minimize the difference between the simulated waveform and the approximation. In the following analysis, a new term  $\varphi_n(j,k)$  is introduced to express the phase of the boundary between region j and k of oscillator n, where the value of  $\varphi_n(j,k)$  is kept between 0 and  $2\pi$ .

Figure 1.6: (a) Piece-wise linear approximation of the waveform. (b) Piece-wise linear approximation of the PSF and ASF.

In general the region boundary is expressed as  $\varphi_n(j,k) + 2m\pi$ , where m = 0, 1, 2...

Similarly, the PSF  $\Gamma_n(\cdot)$  and the ASF  $\Omega_n(\cdot)$  are divided into the same four regions as  $f_n(\cdot)$  is divided. The values of both  $\Gamma_n(\cdot)$  and  $\Omega_n(\cdot)$  are approximated as constant within each region as shown in Figure 1.6(b). As mentioned previously, when the oscillator is in either region 2 or 4, the magnitude of the ASF peaks and the magnitude of the PSF is at its minimum. Conversely, when the oscillator is either in region 1 or 3, the PSF's magnitude peaks and the magnitude of the ASF is at its minimum. Therefore, in regions 2 and 4, the PSF is approximated as zero and the ASF is set to its maximum value, 1. On the other hand, in region 1 and 3, the ASF is approximated as zero and the PSF is approximated as a constant. It follows from (12) that the value of the PSF in region 1 and 3 is given by

$$\Gamma_n(\Phi_n(t)) = \frac{1}{C_n f'_n(\Phi_n(t))}, \quad (n = 1, 2).$$

(21)

The above approximation greatly simplified the non-linear terms in the ODEs from (17) to (20) as follows:

$$\Phi_{1}'(t) = \omega_{1} + \gamma_{1,j} \frac{C_{1}C_{2}}{C_{1} + C_{2}} \left[ s_{2,k} - s_{1,j} - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}} \right],$$

(22)

$$\Phi_{2}'(t) = \omega_{2} - \gamma_{2,k} \frac{C_{1}C_{2}}{C_{1} + C_{2}} \left[ s_{2,k} - s_{1,j} - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}} \right],$$

(23)

$$\Delta A_{1}'(t) = \alpha_{1,j} \frac{C_{2}}{C_{1} + C_{2}} \left[ s_{2,k} - s_{1,j} - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}} \right] - \frac{\Delta A_{1}(t)}{\tau_{1}}, \quad (24)$$

$$\Delta A_{2}'(t) = -\alpha_{2,k} \frac{C_{1}}{C_{1} + C_{2}} \left[ s_{2,k} - s_{1,j} - \frac{\Delta A_{2}(t)}{\tau_{2}} + \frac{\Delta A_{1}(t)}{\tau_{1}} \right] - \frac{\Delta A_{2}(t)}{\tau_{2}}, \quad (25)$$

where  $s_{1,j}$  and  $s_{2,k}$  represent the waveform slope of oscillator 1 and 2, respectively. The subscripts *j* and *k* range from 1 to 4, representing the region that oscillator 1 and 2 are in. Similarly,  $\alpha_{1,j}$  and  $\alpha_{2,k}$  represent the ASF values and the terms  $\gamma_{1,j}$  and  $\gamma_{2,k}$  represent the PSF values. At any given time instant, each oscillator is in one of the four regions, which leads to 16 possible realizations of the ODEs from (22) to (25). However, the previous simplification of the ASF and PSF values results in only four unique forms of the ODEs. Specifically, when both ASFs are 1, the ODEs are reduced to second-order nonhomogeneous differential equations. When either of the ASF is 0, the ODEs are reduced to first-order homogeneous differential equations. For each of the four cases, the ODEs have closed form solutions.

For demonstration purposes, Figure 1.7(a) shows the calculated locking transient of both oscillators using the simplified model. The free running waveforms of both oscillators are also plotted for comparison. In order to explain how to solve the simplified ODEs, the first 400 ps of the locking transient waveform is shown in the top plot of Figure 1.7(b). The detailed procedure of how the solution is obtained is presented as follows. The first step is to set the initial condition at time t = 0 for the ODEs, i.e.,  $\Phi_1(0)$ ,  $\Phi_2(0)$ ,  $\Delta A_1(0)$  and  $\Delta A_2(0)$ . Because of the approximation that the two oscillators are shorted, the initial condition must be chosen such that  $v_1(0) = v_2(0)$ . In this particular example, the initial phases are chosen as  $\Phi_1(0) = 0$  and  $\Phi_2(0) = 0.4\pi$  for illustration purposes only. For simplicity, the initial extra amplitudes are chosen as  $\Delta A_1(0) = 0$  and  $\Delta A_2(0) = f_1(\Phi_1(0)) - f_2(\Phi_2(0))$ . As a result, both oscillators start from region 1. Solving the ODEs yields the following closed form solutions:

Figure 1.7: (a) Locking transient of coupled oscillator pair using the simplified model. (b) The first 400ps is expanded to illustrate the details of how to solve the simplified ODEs.

$$\Phi_{1}(t) = \left[\omega_{1} + \gamma_{1,1} \frac{C_{1}C_{2}}{C_{1} + C_{2}} (s_{2,1} - s_{1,1})\right] t + \gamma_{1,1} \frac{C_{1}C_{2}}{C_{1} + C_{2}} \Delta A_{2}(0) \left(e^{-t/\tau_{2}} - 1\right) + \Phi_{1}(0), \qquad (26)$$

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

$$\Phi_{2}(t) = \left[\omega_{2} - \gamma_{2,1} \frac{C_{1}C_{2}}{C_{1} + C_{2}} (s_{2,1} - s_{1,1})\right] t - \gamma_{2,1} \frac{C_{1}C_{2}}{C_{1} + C_{2}} \Delta A_{2}(0) \left(e^{-t/\tau_{2}} - 1\right) + \Phi_{2}(0), \qquad (27)$$

$$\Delta A_1(t) = 0, \qquad (28)$$

$$\Delta A_2(t) = \Delta A_2(0)e^{-t/\tau_2}.$$

(29)

As time progresses, each oscillator will reach the boundary between region 1 and 2. The region transition is illustrated in the bottom plot in Figure 1.7(b), where the region values of both oscillators are plotted as functions of time. In addition, a time sequence t[n], (n = 1, 2, 3...) is used to express each time a region transition occurs, which is shown as circles in the figure. The following analysis shows how to calculate the time sequence t[n] using the closed form solutions. The first region transition time, expressed as t[1], is obtained in two steps. The first step is to numerically solve the following two equations,  $\Phi_1(t) = \varphi_1(1,2) + 2m\pi$  and  $\Phi_2(t) = \varphi_2(1,2) + 2m\pi$ , where m = 0. The solutions to the equations are called  $t_1[1]$  and  $t_2[1]$ , respectively. Then the region transition time is given by the smaller of the two solutions, i.e.,  $t[1] = \min(t_1[1], t_2[1])$ . The greater of the two solutions is discarded. In this particular example, oscillator 2 has the first transition. At t = t[1], oscillator 1 remains in region 1 while oscillator 2 advances to region 2. The form of the solutions is changed accordingly but remains closed form for  $t \ge t[1]$  (the detailed expression of the solutions is not shown here for brevity). In addition, the solutions are uniquely determined by the initial condition at t = t[1]. Because of the continuity of the solutions, the initial condition is given by evaluating (26) to (29) at t = t[1], i.e.,  $\Phi_1(t[1])$ ,

Figure 1.8: Comparison between transistor level simulation and theoretical calculation using the simplified model of the coupled oscillator pair. (a) Waveform of one locked period. (b) Absolute error between simulation and calculation.

$\Phi_2(t[1])$ ,  $\Delta A_1(t[1])$  and  $\Delta A_2(t[1])$ . The next step is to calculate the second region transition time t[2]. Similar to the procedure by which t[1] is obtained, t[2] is given by

the smaller solution to the following equations,  $\Phi_1(t) = \varphi_1(1,2) + 2m\pi$  and  $\Phi_2(t) = \varphi_2(2,3) + 2m\pi$ , where m = 0. The rest of the solution is obtained by repeating the procedure described above.

As mentioned before, the above analysis is based on the approximation that the oscillators are shorted together. As a result, the solutions satisfy  $v_1(t) = v_2(t)$ . In order to obtain the voltage at the oscillator output node, the effect of the 20- $\Omega$  coupling resistor should be taken into account. First the oscillator current  $i_1(t)$  and  $i_2(t)$  are given by (16). Then the node voltages of oscillator 1 and 2 are given by  $v_2(t)+i_2(t)\cdot(10\Omega)$  and  $v_2(t)-i_2(t)\cdot(10\Omega)$ , respectively. Similar to the previous section, the error due to this approximation is neglected. The calculated locked frequency is 1.955 GHz, which is within 1.5% error of the value obtained from transistor-level simulation. The locked waveforms of oscillator 1 and 2 are shown in Figure 1.8(a) to compare with the results obtained from transistor-level simulation and simulation is shown in Figure 1.8(b).

The choice of the initial conditions deserves further discussion. In principle, there are infinite possibilities for the initial condition at t = 0 to satisfy  $v_1(0) = v_2(0)$ . Therefore, it is impractical to exhaustively calculate all possible initial conditions. For all the different initial conditions tested, the two oscillators obtain frequency lock within several oscillator cycles.

Compared with the more accurate model presented in the previous section, the simplified model greatly reduces the amount of calculation. Instead of calculating at every time step, the simplified model allows numerical calculation to be performed only

four times in one period for each oscillator. More importantly, despite the gross error introduced by the approximation, the simplified model can still predict the locking behavior with moderate accuracy as shown in Figure 1.8. This is a good indication that the salient property of the oscillator is still preserved by the simplified model even in complicated phenomenon like the injection locking.

## VI. CONCLUSION

A conceptually simple, yet accurate, oscillator model is presented in this paper. The model parameters can be quickly deduced from circuit-level simulations. Once the parameters are obtained, the model is capable of accurately predicting the injectionlocking behavior of strongly coupled oscillators with component mismatches. In addition to deriving the general model, the paper derives a simplified version of the model applicable to ring oscillators. Good agreement between the simulation and theoretical calculation has been observed. A piece-wise linear model is developed to further simplify the calculation. Despite its simplicity, the further simplified model still retains the salient property of the injection-locking behavior between strongly coupled oscillators.

### REFERENCES

I. Galton, D. A. Towne, J. J. Rosenberg, H. T. Jensen, "Clock Distribution Using Coupled Oscillators", 1996 *IEEE International Symposium on Circuits and Systems*, vol. 3.4 pp. 217–220, May 1996.

- H. Mizuno, K. Ishibashi, "A Noise-immune GHz-Clock Distribution Scheme using Synchronous Distributed Oscillator," 1998 *IEEE International Solid-State Circuits Conference*, pp. 404—405, Feb. 1998.

- 3. T. Takahashi, et. al., "110-GB/s Simultaneous Bidirectional Transceiver Logic Synchronized with a System Clock," *IEEE Journal of Solid-State Circuits*, vol. 34, no. 11, pp. 1526—1533, Nov. 1999.

- 4. P. Liao and R. A. York, "A New Phase-shifterless Beam Scanning Technique Using Arrays of Coupled Oscillators," *IEEE Transaction on Microwave Theory and Techniques*, vol. 41, no. 10, pp. 1810–1815, Oct. 1993.

- 5. A. Hajimiri, T. H. Lee, "A General Theory of Phase Noise in Electrical Oscillators," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 2, pp. 179–194, Feb.1998.

- 6. A. Hajimiri, T. H. Lee, "The Design of Low Noise Oscillators," Kluwer Academic Publishers, 1999.

- H. Tanaka, et. al., "Synchronizability of Distributed Clock Oscillators", IEEE Transaction on Circuits and Systems – I: Fundamental Theory and Applications, vol. 49, no. 9, pp. 1271–1278, Sep. 2002.

- 8. J. H. Mathews. *Numerical Methods for Mathematics, Science, and Engineering*. Prentice- Hall, 1992.

# A Multiple-Crystal Interface PLL with VCO Realignment to

## **Reduce Phase Noise**

Sheng Ye, Lars Jansson and Ian Galton

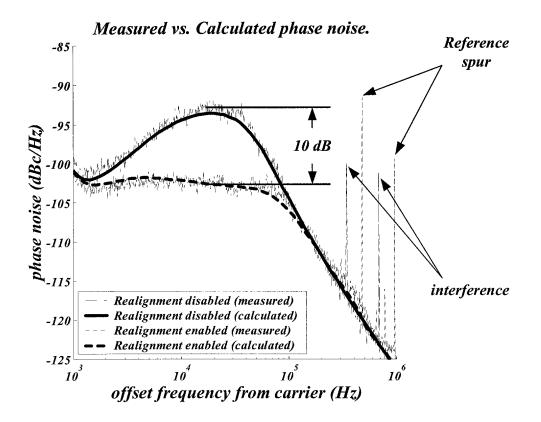

*Abstract* — An enhancement to a conventional integer-*N* PLL is introduced, analyzed, and demonstrated experimentally to significantly reduce VCO phase noise. The enhancement, which involves periodically injection locking the VCO to a buffered version of the reference, has the effect of widening the PLL bandwidth and reducing the overall phase noise. It is demonstrated in a 3 V 6.8 mW CMOS reference PLL with a ring VCO capable of converting most of the popular crystal reference frequencies to a 96 MHz RF PLL reference and baseband clock for a direct conversion Bluetooth wireless LAN. The peak in-band phase noise at an offset of 20 kHz is –102 dBc/Hz with the technique enabled and –92 dBc/Hz with the technique disabled. A theoretical analysis is presented and shown to be in close agreement with the measured results.

### I. INTRODUCTION

This paper presents a new enhancement to a conventional PLL in which a CMOS ring voltage controlled oscillator (VCO) is periodically realigned by the PLL reference signal to reduce phase noise. The enhancement is applied to a VHF reference PLL capable of operation with a wide range of crystal frequencies for a Bluetooth transceiver. A peak phase noise reduction of 10 dB and an integrated phase

noise reduction of 8.3 dB relative to the conventional PLL alone are demonstrated via measured results that closely match theoretical predictions.

The eventual market penetration of low-end local area networks such as Bluetooth will depend largely on the extent to which transceiver prices can be reduced. With Bluetooth unit prices approaching the five dollar level, the cost of the external crystal has become significant. Since the transceivers generally are placed in host devices with their own crystal references, such as cellular telephones, computers, and PDAs, a cost reduction can be achieved by sharing the same reference as the host device. This is particularly advantageous in wireless host devices such as cellular telephones which tend to be sensitive to interference at the circuit board level from oscillator signals outside of their frequency plans. Therefore, for maximum flexibility it is desirable to have a Bluetooth transceiver capable of operating from all of the popular crystal reference frequencies.

The most critical local oscillator in a wireless transceiver typically is that used to drive the RF mixers. In a direct conversion Bluetooth transceiver such as [1], inphase and quadrature local oscillator signals are required with frequencies selectable from 2.402 GHz to 2.480 GHz in steps of 1 MHz. In principle, these signals can be generated from any of the popular crystal frequencies by a fractional-*N RF PLL*, but the flexibility required to accommodate all the crystal frequencies would translate into significant added circuit area and power consumption [2], [3]. Alternatively, an integer-*N* RF PLL with a 1 MHz reference signal can be used. The primary difficulty with this approach is that a *reference PLL* capable of generating the 1 MHz reference signal with very little phase noise from any of the crystal frequencies is required. This paper presents such a PLL designed for a next generation version of the Bluetooth transceiver in [1]. The PLL generates a 96 MHz signal from which the 1 MHz RF PLL reference is derived along with a 32 MHz clock used to drive the baseband circuitry and data converters in the transceiver.

The reference PLL design was challenging because of the requirements that it be implemented with only CMOS transistors, that it use an on-chip ring VCO to avoid external components, and that its phase noise between 1 kHz and 50 kHz from the carrier be below -100 dBc/Hz (the loop bandwidth of the RF PLL is 50 kHz). Unfortunately, CMOS ring oscillators are noisy. For example, the measured phase noise from the ring VCO implemented within the reference PLL at an offset from the carrier of 100 kHz is -107 dBc/Hz, so the loop bandwidth of a conventional PLL would have to be approximately 100 kHz to sufficiently suppress the VCO noise with enough margin to allow for the phase noise contributed by the other PLL components. The large loop bandwidth ruled out the use of a conventional integer-N PLL. In such a PLL, the reference frequency is obtained by dividing the crystal frequency to its greatest common divisor with 96 MHz, but to maintain stability over process and temperature extremes the PLL reference frequency must be approximately 20 times the loop bandwidth [4]. Among the commonly used crystal references, this implies that the target phase noise could not be met for 19.68 and 19.8 MHz crystals using a conventional integer-N PLL. For example, the greatest common divisor of 19.68 MHz and 96 MHz is 480 kHz, which implies a reference frequency of 480 kHz and a maximum practical loop bandwidth of only 24 kHz.

To solve this problem, a VCO realignment technique has been developed and

applied to a conventional narrow band integer-*N* PLL. The new topology is referred to as a realigned PLL (RPLL). The idea is to perform VCO realignment by injection locking the VCO to a buffered version of the PLL reference once every reference period. As explained in Section II, the realignment has the effect of significantly reducing the phase noise introduced by the VCO at frequencies below the reference frequency. A theoretical model of the RPLL is derived in Section III, and measurement results are presented in Section IV that are very close to those predicted by the theoretical model. It is shown that the RPLL has similarities to a delay-locked loop (DLL) in the way it suppresses phase noise below the reference frequency, and that the theoretical model derived in this paper for the RPLL is also applicable to the DLL. Nevertheless, along with the usual benefits offered by PLLs, the RPLL offers the potential advantage that it is not restricted to oscillators based on delay lines; the injection locking principle on which the RPLL is based is known to be applicable to various types of VCOs [5], [6].

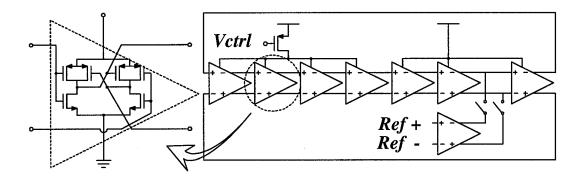

## II. REALIGNED PLL SYSTEM OVERVIEW

#### A. The Idea

A simplified block diagram of the RPLL is shown in Figure 2.1. The idea is to use a buffered version of the PLL reference to correct the VCO once every reference period. As shown in the figure, the new PLL is based on a conventional integer-*N* PLL with the addition of a buffer and a control logic block. The motivation for this new topology is described below.

Figure 2.1: Proposed top-level system block diagram.

If the oscillator were noiseless, its zero-crossings would be uniformly spaced in time. However, noise inside the oscillator causes phase fluctuations which give rise to errors in the zero-crossing times. As shown in [7], noise induced phase fluctuations persist indefinitely in oscillators. This phenomenon is illustrated in Figure 2.2(a), where the phase fluctuations "build up" in a 3-stage ring VCO over time because the zero-crossing error introduced by each inverter adds to all the previous zero-crossing errors [8]. Therefore the VCO can be modeled as a phase fluctuation integrator. In the frequency domain, this integration has the effect of multiplying the power spectral density (PSD) of the zero-crossing time errors by a transfer function proportional to  $1/f^2$  which results in high in-band phase noise.

As shown in Figure 2.2(b), assuming the VCO frequency is an integer multiple of the reference frequency, the realignment technique shorts a buffered version of the clean reference signal to the VCO output during windows surrounding the time instants where VCO edges ideally coincide with reference signal edges. This causes each VCO edge to be "pulled" toward the correct position thereby suppressing the

Figure 2.2: (a) Phase noise is accumulated in typical ring oscillators. (b) Periodically realigning the oscillator to a "clean" edge suppresses the phase noise accumulation.

memory of past errors. In the frequency domain, the suppression of noise memory attenuates the  $1/f^2$  transfer function mentioned above at frequencies below the reference frequency which greatly reduces the in-band phase noise power introduced by the VCO.

B. The Realigning Factor

During each phase realignment, the buffered reference edge is connected to the VCO clock edge. Ideally, if both the reference and the VCO were noiseless, a VCO edge would line up with an edge of the buffered reference once every reference period.

Figure 2.3: Simulated initial phase difference versus shifted phase curve.