INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films

the text directly from the original or copy submitted. Thus, some thesis and

dissertation copies are in typewriter face, while others may be from any type of

computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality illustrations

and photographs, print bleedthrough, substandard margins, and improper

alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript

and there are missing pages, these will be noted. Also, if unauthorized

copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and continuing

from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations appearing

in this copy for an additional charge. Contact UMI directly to order.

ProQuest Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

**UMI**®

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

# The Analysis and Design of Mismatch-Shaping Digital-to-Analog Converters

A dissertation submitted in partial satisfaction of the requirements for the degree

**Doctor of Philosophy**

in Electrical and Computer Engineering

by

Jared Eugene Welz

### Committee in charge:

Professor Ian Galton. Chair Professor William Hodgkiss Professor Bhaskar Rao Professor Paul Siegel Professor Patrick Fitzsimmons

2002

UMI Number: 3055804

### UMI Microform 3055804

Copyright 2002 by ProQuest Information and Learning Company.

All rights reserved. This microform edition is protected against unauthorized copying under Title 17, United States Code.

ProQuest Information and Learning Company 300 North Zeeb Road P.O. Box 1346 Ann Arbor, MI 48106-1346

Copyright ©

Jared Eugene Welz. 2002

All rights reserved.

To Shirlene Miyake

### TABLE OF CONTENTS

|    | Signature Page                                                                                                   | iii  |

|----|------------------------------------------------------------------------------------------------------------------|------|

|    | Dedication                                                                                                       | iv   |

|    | Table of Contents                                                                                                | v    |

|    | List of Figures                                                                                                  | vi   |

|    | List of Tables                                                                                                   | viii |

|    | Acknowledgments                                                                                                  | ix   |

|    | Vita                                                                                                             | xii  |

|    | Abstract of the Dissertation                                                                                     | xiii |

| 1. | Necessary and Sufficient Conditions for Mismatch-Shaping in Multi-Bit Digital-to-Analog Converters               | l    |

| 2. | Simplified Logic for First-Order and Second-Order Mismatch-Shaping Digital-to-Analog Converters                  | 30   |

| 3. | The PSD of the DAC Noise in the Dithered First-Order Tree-Structured Digital-to-Analog Converter                 | 66   |

| 4. | The PSD of the First-Order Tree-Structured DAC in a Second-Order ADC Delta-Sigma Modulator with a Midscale Input | 106  |

### LIST OF FIGURES

|      | hapter I 1 The general multi-bit DAC                                                                                                                 | ;  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.   | 2 A first-order, lowpass vector feedback DAC                                                                                                         | 11 |

| 1.3  | 3 The DWA DAC                                                                                                                                        | 14 |

| 1    | 4 The butterfly shuffler DAC                                                                                                                         | 16 |

| 1.   | 5 The tree structured DAC                                                                                                                            | 18 |

| 1.0  | 5 The partitioned DWA DAC                                                                                                                            | 23 |

| 1.   | 7 Output noise PSD from a simulation of a 2nd-order, analog $\Delta\Sigma$ modulator using the partitioned DWA DAC                                   | 24 |

|      | hapter 2 i. An example second-order, 33-level, lowpass analog $\Delta\Sigma$ modulator realized with switched capacitors                             | 33 |

| 2.5  | 2 A 33-level MS DAC with switched capacitor DAC elements                                                                                             | 33 |

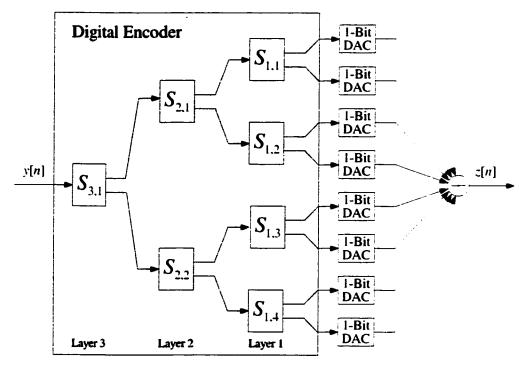

| 2.3  | 3 The 33-level tree-structured digital encoder                                                                                                       | 35 |

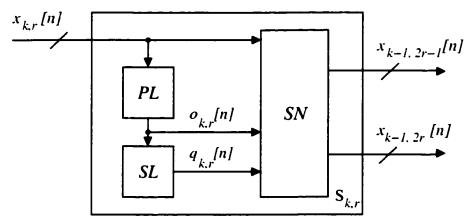

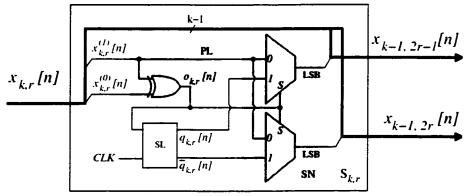

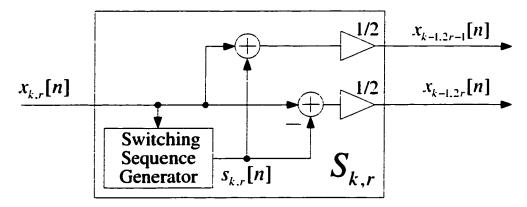

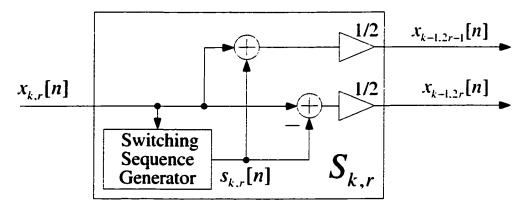

| 2    | 4 The switching block $S_{k,r}$                                                                                                                      | 35 |

| 2.3  | 5 The signal processing performed in the switching block                                                                                             | 37 |

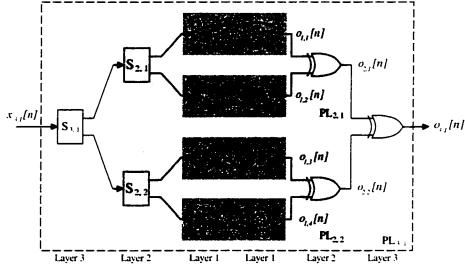

| 2.6  | 5 A functional partitioning of the switching block                                                                                                   | 39 |

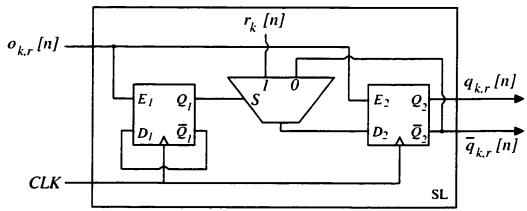

| 2.7  | 7 The first-order lowpass sequencing logic with dither                                                                                               | 43 |

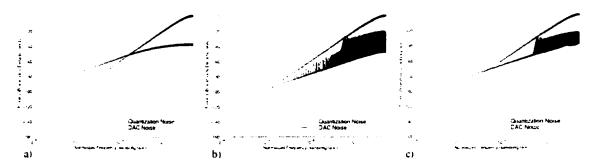

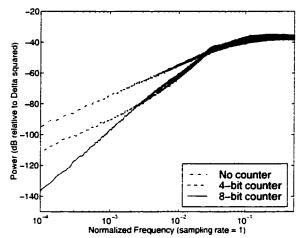

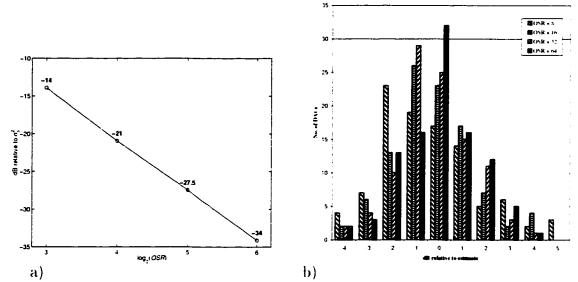

| 2.8  | B DAC and quantization noises from a simulation of a 5-bit $\Delta\Sigma$ modulator with the first-order lowpass sequencing logic and varying dither | 44 |

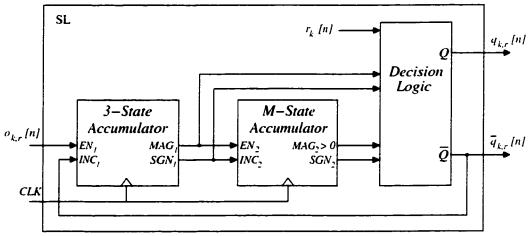

| 2.9  | The second-order, lowpass sequencing logic with dither                                                                                               | 48 |

| 2.10 | DAC noise from a simulation of an ADC $\Delta\Sigma$ modulator with the second-order, lowpass sequencing logic with dither                           | 50 |

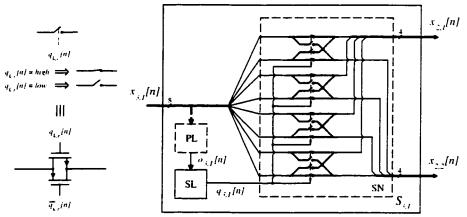

| 2.11 | The medium-speed switching block                                                                                                                     | 52 |

| 2.12 | The splitting network for a high-speed switching block and the CMOS implementation of a transmission gate                                             | <b>5</b> 4 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2.13 | The parity logic for the high-speed switching block                                                                                                   | 55         |

|      | apter 3 A 9-level tree-structured DAC                                                                                                                 | <b>6</b> 9 |

| 3.2  | The signal processing performed by the switching block                                                                                                | 71         |

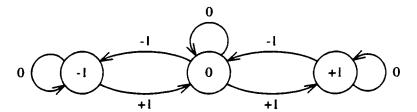

| 3.3  | The FSTD for the switching sequence code where the state corresponds to the value of $RDS_{k,r}(m)$                                                   | 74         |

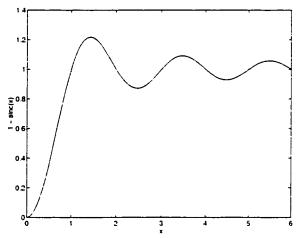

| 3.4  | The function $1 - \operatorname{sinc}(x)$                                                                                                             | 77         |

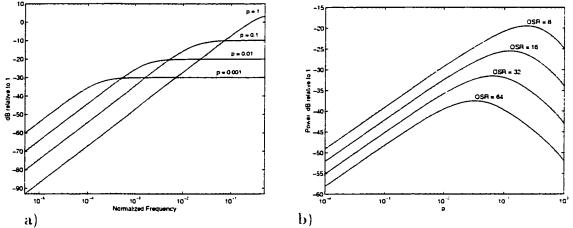

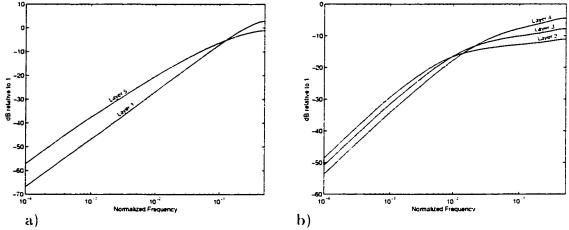

| 3.5  | The PSD and signal-band power of $s_{k,r}[n]$ given its input parity sequence is an i.i.d. Bernoulli sequence with $p = P\left(o_{k,r}[n] = 1\right)$ | 78         |

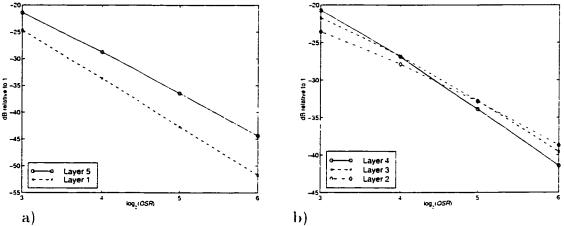

| 3.6  | DAC noise power bound as a function percent mismatch and oversampling ratio for both dither schemes                                                   | 83         |

|      | apter 4 A 5-bit, second-order, ADC $\Delta\Sigma$ modulator                                                                                           | 109        |

| 4.2  | A 9-level tree-structured DAC                                                                                                                         | 111        |

| 4.3  | The signal processing performed by the switching block                                                                                                | 112        |

| 4.4  | The switching sequence PSDs obtained with the $\Delta\Sigma$ modulator model .                                                                        | 115        |

| 4.5  | The switching sequence signal-band powers obtained with the $\Delta\Sigma$ modulator model                                                            | 115        |

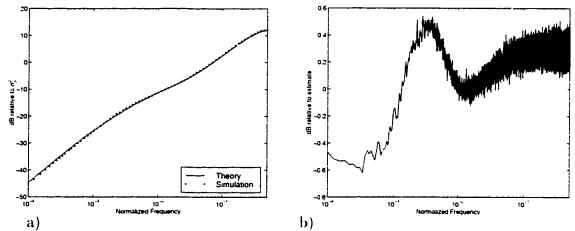

| 4.6  | The average DAC noise PSDs from simulation and theory and their dB difference                                                                         | 117        |

| 4.7  | The average DAC noise signal-band powers from theory and histograms of the DAC noise signal-band powers from 100 simulations                          | 117        |

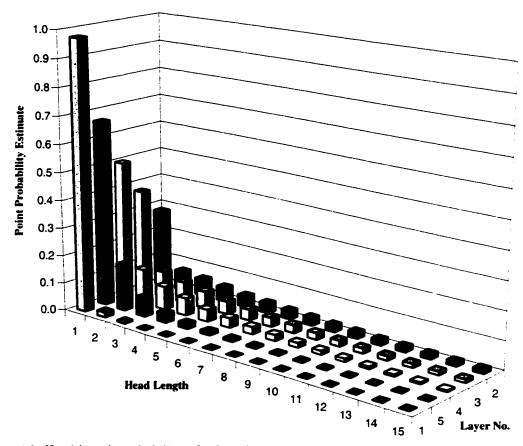

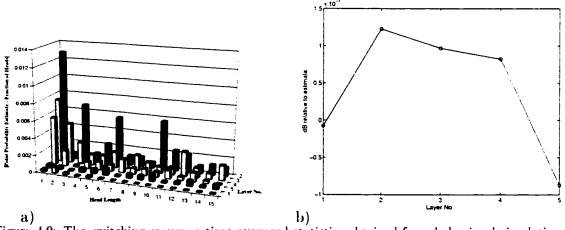

| 4.8  | Head-length probabilities for lengths 1 to 15 estimated using the $\Delta\Sigma$ modulator model                                                      | 122        |

| 4.9  | The switching sequence time-averaged statistics obtained from behavioral simulations                                                                  | 122        |

### LIST OF TABLES

| Ch  | apter $2$                                                                                                                                   |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Estimated hardware requirements for undithered mismatch-shaping DAC encoders for use within a 5-bit $\Delta\Sigma$ ADC                      | 58 |

| 2.2 | Estimated hardware requirements for mismatch-shaping DAC encoders with harmonic distortion compensation for use within a $\Delta\Sigma$ ADC | 58 |

### ACKNOWLEDGMENTS

First, I would like to thank my advisor, Ian Galton, for his guidance, support, patience, and most importantly, friendship throughout this whole Ph.D odyssey. As his "Padawan learner". I was able to realize a potential that, at the onset of the journey, was apparent only in my midichlorian count. I'll always remember the wisdom of his Jedi lessons, including: "try not! Do or do not...there is no try!" I'd also like to thank his family—Kerry, Riley, and Mitchell—for "bringing balance to the Force."

I would like to thank Professor William Hodgkiss. Professor Paul Siegel. Professor Patrick Fitzsimmons, and Professor Bhaskar Rao for serving on my doctoral committee. I would also like to thank Karol Previte. Carolyn Kuttner. Jim Thomas, and the rest of the rebel alliance in the ECE Department for their support.

I'd like to thank my biological parents. Mary Joan and Ed Welz, for believing in their little Gungan. Specifically, I thank my pa for filling out my undergraduate college applications and providing me with the opportunities that made this degree possible and yet were never accessible to him.

I'd also like to thank my parents-in-law. Lois and Richard Miyake, for their love, friendship, and support during my years at UCSD. I am grateful for how they took care of me and my babies and for providing me the much-needed refuge from the dark side of graduate school.

I would like to thank my friends in the rebel alliance, many of which I consider family, for being there for me when I have needed them and for understanding my struggles with the dark side as a Padawan learner at UCSD. This collection of friends includes the Balloonheads: Brian "Luke Skywalker" Ehler, John "Chewbacca" Guest, and Leland "Yoda" Jay. This collection also includes Shelly Ehler.

Michelle Guest, GiGi Carrano, Alison and Jeff Toda, Stephanie and Peter Wu, Ashley and Thomas Sohn, Hena Borneo, Shirley Wang, Diane Wong, Joey and Bill Malohn...May the Force be with you, always.

I wish to thank the current and former members of the ISPiG Jedi Council for their friendship and wisdom—Eric "EZ-E" Fogleman. Asaf "Saf-dogg" Fishov. Sheng "The Man" Ye. Sudhakar "Monsoon" Pamarti. Ash "The Swami Salami" Swaminathan. Eric "The Goose" Siragusa. Alan "Fish Boy" Lewis. Bill Huff. and Henrik Jensen. Particularly. I'd to like express my gratitude to the Monsoon: much of this work was inspired by our conversations that ranged from the meaning of statistical independence to yo-yo tricks. Also, I'd like to thank the venerable Jedi Master EZ-E for mentoring me during the toughest times of my graduate school experience. His support during these times enabled me to overcome my struggles with the dark side that nearly thwarted the completion of this dissertation.

I would like to thank my babies on the moon of Endor—Pooka (the Wampa). Noodle (my bestest buddy in the whole wide world). Jumar. Cricket. Pumpkin. Zippity. Kiwi. Lima. Mila. Mochi. and Chia—whose love is more powerful then any Death Star.

Finally, I'd like to thank my R2 unit, Shirlene Miyake, for helping me make "the Kessel run in less than twelve parsecs." Her love inspired every result in this dissertation while her brilliance helped guide me through each obstacle in my Jedi training. More importantly, she showed me that there is so much more to life then going "into Toshi Station to pick up some power converters."

The four chapters that compose this dissertation are intended to be published as separate papers. Chapter 1 has been submitted for review with the *IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing* and covers

material presented at the International Symposium on Circuits and Systems in May 2002. Chapter 2 appeared in the November 2001 issue of the IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing. Chapter 3 and 4 are in preparation for submission to the IEEE Transactions on Information Theory. Chapter 4 includes material that was presented at the International Conference on Acoustics. Speech. and Signal Processing in May 2001. This work was supported by the Office of Naval Research under Grant N00014-98-1-0830.

### VITA

| 1993      | Bachelor of Science. University of California. Irvine                                                               |

|-----------|---------------------------------------------------------------------------------------------------------------------|

| 1994      | Master of Science, University of California, Los Angeles                                                            |

| 1994-1995 | Assistant Network Engineer<br>AirTouch International (now Vodafone AirTouch)                                        |

| 1995-1996 | RF Engineer<br>Pacific Bell Wireless (now Cingular Wireless)                                                        |

| 1996-1997 | Advanced Technologies Engineer<br>Los Angeles Cellular (now AT&T Wireless)                                          |

| 1997-2002 | Graduate Student Researcher  Department of Electrical and Computer Engineering. University of California. San Diego |

| 2002      | Doctor of Philosophy. University of California, San Diego                                                           |

### ABSTRACT OF DISSERTATION

The Analysis and Design of

Mismatch-Shaping Digital-to-Analog Converters

by

Jared Eugene Welz

Doctor of Philosophy in Electrical and Computer Engineering (Communications Theory and Systems)

University of California. San Diego. 2002

Professor Ian Galton. Chair

Multi-bit digital-to-analog converters (DACs) are often constructed by combining several 1-bit DACs in parallel. In such a DAC, mismatches among the 1-bit DACs cause its output to be a nonlinear function of its input. This error is modeled as an additive noise source called the DAC noise. The DAC noise limits the attainable resolution of the multi-bit DAC and, if not addressed, prohibits its use in high-performance applications. Mismatch-shaping DACs mitigate this problem by suppressing the DAC noise power in the data signal's frequency band so that most of it can be removed by frequency-selective filters. These DACs facilitate multi-bit delta-sigma ( $\Delta\Sigma$ ) modulation and have thus become widely used in high-performance  $\Delta\Sigma$  data converters.

However, the theoretical analyses of mismatch-shaping DACs have been limited. For most architectures, the analysis is limited to proving that the DAC noise power spectral density (PSD) is zero at some frequency. Typically, this analysis pertains only to the specific architecture and does not provide a reasonable estimate of the signal-band power of the DAC noise. Consequently, engineers usually rely on simulations to predict their DAC's performance, which can be misleading.

This dissertation provides a unifying theory for mismatch-shaping DACs and furthers the development and analysis of an architecture called the *tree-structured DAC*. The unifying theory, which is given in Chapter 1, is in the form of necessary and sufficient conditions for a multi-bit DAC to be a mismatch-shaping DAC. These conditions are used to analyze and compare several well-known mismatch-shaping DACs. Chapter 2 presents different implementations of the tree-structured DAC that give rise to performance and complexity trade-offs. One such implementation, the dithered first-order low-pass tree-structured DAC, is analyzed in Chapter 3. In this chapter, expressions for the DAC noise PSD and signal-band power are derived and used to obtain an achievable power bound for the DAC noise. In Chapter 4, the DAC noise PSD expression from Chapter 3 is used to develop the theoretical DAC noise PSD for the tree-structured DAC in a  $\Delta\Sigma$  modulator application.

## Necessary and Sufficient Conditions for Mismatch Shaping in Multi-Bit Digital-to-Analog Converters

Jared Welz, Ian Galton

Abstract—Multi-bit DACs are often constructed by combining several 1-bit DACs of equal or different weights in parallel. In such DACs, component mismatches give rise to signal dependent error that can be viewed as additive DAC noise. In some cases these DACs use dynamic element matching techniques to decorrelate the DAC mismatch noise from the input sequence and suppress its power in certain frequency bands. Such DACs are referred to as mismatch-shaping DACs and have been used widely as enabling components in state-of-the-art delta-sigma data converters. Several different mismatch-shaping DAC topologies have been presented, but theoretical analyses have been scarce and no general unifying theory has been presented in the previously published literature. This paper presents such a unifying theory in the form of necessary and sufficient conditions for a multi-bit DAC to be a mismatch-shaping DAC, and applies the conditions to evaluate the DAC noise generated by several of the previously published mismatch-shaping DACs, and qualitatively compare their behavior.

#### I. INTRODUCTION

OST multi-bit digital-to-analog converters (DACs) consist of multiple 1-bit DACs. In each case, the digital input sequence is decomposed into multiple 1-bit sequences each of which drives a 1-bit DAC. Each 1-bit DAC generates one of two analog output levels depending upon whether its input bit is high or low. The

outputs of the 1-bit DACs are summed to form the output of the multi-bit DAC. The primary differences among the various multi-bit DAC architectures reside in how the multi-bit input sequence is mapped to the multiple 1-bit DAC input sequences, and how the output levels of the 1-bit DACs are scaled relative to each other.

In practice, component mismatches inevitably introduced during circuit fabrication, most notably mismatches among nominally identical unit capacitors or current sources, cause the 1-bit DAC output levels to deviate from their ideal values. The resulting error can be modeled, without approximation, as additive error and is referred to as *DAC noise*. In present VLSI technology, the values of nominally identical components can rarely be matched to better than a standard deviation of 0.1%. In Nyquist-rate DACs, i.e., DACs that convert digital signals with a pass-band from zero up to half their sample-rate, this translates into DAC noise that limits the achievable signal-to-noise-and-distortion ratio (SINAD) to less than 70 dB. Moreover, without some form of dither or other randomization technique, the DAC noise is a deterministic, nonlinear function of the input sequence so it contains harmonic distortion which can be problematic in many applications.

Dynamic element matching (DEM) techniques can be applied to multi-bit DACs both to suppress the power of the DAC mismatch noise in specific frequency bands and to eliminate the harmonic distortion. Such multi-bit DACs are referred to as mismatch-shaping DACs. They are particularly useful in applications that require high precision within relatively narrow frequency bands. As such, in recent years they have become widely used in high-performance delta-sigma ( $\Delta\Sigma$ ) data converters.

Although numerous mismatch-shaping DAC architectures have been developed, published mathematical analyses of these DACs have been limited and disjoint to

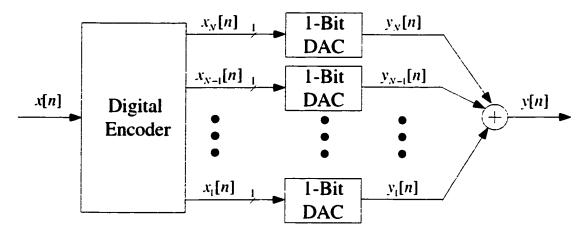

Figure 1.1: The general multi-bit DAC.

date. Most analyses have been individually tailored to specific architectures, and in most cases simulations have been relied upon to determine the characteristics of the DAC noise, which can be misleading. Consequently, there is no unifying theory that applies to multi-bit DACs in general. This lack of theory has made it difficult to compare the merits of the different mismatch-shaping DAC architectures, and likely has impeded the development of new mismatch-shaping DAC architectures.

This paper provides a unifying theory in the form of necessary and sufficient conditions for a general multi-bit DAC to be a mismatch-shaping DAC. Unlike previous analyses [1] the conditions do not rely on properties of the component mismatches. The utility of the conditions is demonstrated by using them to analyze and qualitatively compare most of the widely used mismatch-shaping DAC architectures published to date: first-order, lowpass implementations of the vector feedback [2], data-weighted averaging (DWA) [3],[4], butterfly shuffler [5], tree structured [6], and partitioned DWA [7] DACs.

### II. THE GENERAL MULTI-BIT DAC

The general multi-bit DAC shown in Figure 1.1 consists of a digital encoder and a

bank of N 1-bit DACs. The output of the *i*th 1-bit DAC is given by

$$y_i[n] = \begin{cases} \frac{\Delta_i}{2} + e_{h_i}, & \text{if } x_i[n] \text{ is high:} \\ -\frac{\Delta_i}{2} + e_{l_i}, & \text{if } x_i[n] \text{ is low:} \end{cases}$$

(1)

where  $\Delta_i$  is the nominal step size of the *i*th 1-bit DAC, and  $e_{h_i}$  and  $e_{l_i}$  are its high and low errors, respectively. In many applications, the 1-bit DAC errors result from component mismatches introduced during fabrication of the 1-bit DACs. As such, they are modeled here as arbitrary constants. The digital encoder output is a vector,  $\vec{x}[n]$ , of N 1-bit sequences,  $x_1[n], \ldots, x_N[n]$ . The value of each 1-bit sequence is taken to be 1/2 when it is high and -1/2 when it is low. Ideally, a DAC's output is a scaled version of its input. To ensure that the multi-bit DAC approaches this ideal behavior when the 1-bit DAC errors approach zero, the digital encoder determines its output sequences under the following restriction:

$$\sum_{i=1}^{N} \Delta_i \cdot x_i[n] = \Delta_D \cdot x[n], \tag{2}$$

where  $\Delta_D$  is the nominal smallest step size of the multi-bit DAC. Thus, if the 1-bit DAC errors were all zero, (1) and (2) imply that the DAC output would be given by

$$y[n] = \Delta_D x[n]. \tag{3}$$

However, in practice the 1-bit DAC errors are nonzero, and, as a result, the multi-bit DAC output is a nonlinear function of the multi-bit DAC input. The error from this nonlinearity can be written as additive error:

$$y[n] = \Delta_D x[n] + \tilde{e}[n]. \tag{4}$$

The error sequence  $\tilde{e}[n]$  often contains a constant offset and scaled version of the input: therefore, it is convenient to write (4) as

$$y[n] = \alpha x[n] + \beta + e[n], \tag{5}$$

where  $\alpha$  and  $\beta$  are constants, and e[n] is called the *DAC noise*. In a well-designed system, the DAC noise is a zero mean sequence that is uncorrelated from the multibit DAC input, and the constants  $\alpha$  and  $\beta$  depend only on the 1-bit DAC errors.

Mismatch-shaping DACs are designed such that the digital encoder has several possible output vector values,  $\vec{x}[n]$ , that satisfy (2) for most DAC input values. For example, in a multi-bit DAC in which all the 1-bit DACs have the same nominal step size, a nominal output value of zero is obtained for any output vector with an equal number of high and low bit values. By exploiting this flexibility, the DAC noise can be tailored so that its PSD has desired properties regardless of the values of the 1-bit DAC errors. Therefore, a multi-bit DAC is said to produce DAC noise with a given set of PSD properties if, for any collection of 1-bit DAC errors, there exist constants  $\alpha$  and  $\beta$ , and a sequence e[n] with the given set of PSD properties such that  $y[n] = \alpha x[n] + \beta + e[n]$ .

Various DAC noise PSD properties can be obtained by mismatch-shaping DACs. In some DACs, the digital encoder operates such that the DAC noise is white: *i.e.*, its PSD is constant with respect to frequency. In such DACs, the power of the white noise depends upon the 1-bit DAC errors (*e.g.*, larger 1-bit DAC errors tend to increase the power of the DAC noise), but the DAC noise is white for any choice of the 1-bit DAC errors. In other DACs, the digital encoder operates such that the DAC noise PSD is continuous with a value of zero at zero frequency:  $\omega = 0$ . In such cases, the power of the DAC noise tends to reside predominantly at high frequencies. Again, the overall power of the DAC noise depends upon the 1-bit DAC errors, but the zero at  $\omega = 0$  and the weighting of the PSD toward high frequencies occurs for any choice of 1-bit DAC errors. Various other DACs are possible that achieve different DAC noise properties. In each case, specific properties (*e.g.*, zero

location) of the DAC noise PSD are preserved regardless of the 1-bit DAC errors.

### III. THE CONDITION FOR MISMATCH SHAPING

The theorem below presents a necessary and sufficient condition for the general multi-bit DAC to produce DAC noise with a given set of PSD properties.

**Theorem:** The multi-bit DAC in Figure 1.1 produces DAC noise with a given set of PSD properties if and only if there exist N-1 sequences  $\phi_1[n], \ldots, \phi_{N-1}[n]$  such that:

(a) each digital encoder output is given by

$$x_i[n] = m_i x[n] + \sum_{j=1}^{N-1} d_{i,j} \cdot \phi_j[n].$$

(6)

where  $d_{i,j}$  and  $m_i$  are constants, and

(b) for any selection of the N-1 constants  $c_1, \ldots, c_{N-1}$ , there exist two constants a and b, and a sequence  $\varepsilon[n]$  with the given set of PSD properties such that

$$\sum_{j=1}^{N-1} c_j \cdot \phi_j[n] = ax[n] + b + \varepsilon[n]. \tag{7}$$

**Proof:** Because  $x_i[n]$  is interpreted as 1/2 when high and -1/2 when low. (1) can be written as

$$y_i[n] = \xi_i x_i[n] + \gamma_i. \tag{8}$$

where  $\xi_i \equiv \Delta_i - (e_{h_i} - e_{l_i})$  and  $\gamma_i \equiv (e_{h_i} + e_{l_i})/2$ . Given  $y[n] = \sum_{i=1}^N y_i[n]$ . (8) implies that

$$y[n] = \sum_{i=1}^{N} \xi_i x_i[n] + \beta_o,$$

(9)

where  $\beta_o \equiv \sum_{i=1}^N \gamma_i$ .

**Sufficiency**: Assume that the N-1 sequences,  $\phi_1[n], \ldots, \phi_{N-1}[n]$ , exist and satisfy (a) and (b) in the theorem. Substituting (6) into (9) gives

$$y[n] = \underbrace{\left(\sum_{i=1}^{N} \xi_i m_i\right)}_{\equiv \alpha_o} x[n] + \sum_{j=1}^{N-1} \underbrace{\left(\sum_{k=1}^{N} \xi_k d_{k,j}\right)}_{\equiv c_j} \phi_j[n] + \beta_o. \tag{10}$$

Condition (b) implies that the second summation in (10) can be decomposed as in (7). Thus, substituting (7) into (10) gives

$$y[n] = \underbrace{(a + \alpha_o)}_{\equiv \alpha} x[n] + \underbrace{b + \beta_o}_{\equiv \beta} + \varepsilon[n]. \tag{11}$$

where  $\varepsilon[n]$  has the given set of PSD properties, so the multi-bit DAC produces DAC noise with the given set of PSD properties.

Necessity: To reduce wordiness, all "linear combinations" discussed hereafter are assumed to have constant coefficients. Let  $\phi_N[n] = \sum_{i=1}^N (\Delta_i/\Delta_D) \, x_i[n]$ , which, by (2), implies that  $\phi_N[n] = x[n]$ , and let  $\phi_1[n], \ldots, \phi_{N-1}[n]$  be any collection of N-1 linear combinations of the digital encoder outputs subject to the constraint that these linear combinations and the one that generates  $\phi_N[n]$  are linearly independent. Then there exists an invertible  $N \times N$  matrix A with values  $a_{j,k}$ , where j is the row number and k is the column number, with  $a_{N,k} \equiv \Delta_k/\Delta_D$  such that  $\vec{\phi}[n] = A\vec{x}[n]$ , and, for each j,

$$\phi_j[n] = \sum_{k=1}^{N} a_{j,k} \cdot x_k[n].$$

(12)

Let D, whose value in its ith row and jth column is denoted  $d_{i,j}$ , be the inverse matrix of A. This implies that  $\vec{x}[n] = D\vec{\phi}[n]$  and, for each i.

$$x_{i}[n] = \sum_{j=1}^{N} d_{i,j} \cdot \phi_{j}[n]. \tag{13}$$

With  $m_i \equiv d_{i,N}$ . (13) is identical to (6) because  $\phi_N[n] = x[n]$ . Therefore, the N-1 sequences  $\phi_1[n], \ldots, \phi_{N-1}[n]$  satisfy condition (a) in the theorem.

To show that the N-1 sequences satisfy condition (b) in the theorem, assume the multi-bit DAC produces DAC noise with the given set of PSD properties. In (9),  $\xi_i$  and  $\beta_o$  are arbitrary constants because each DAC error is an arbitrary constant. Thus, by assumption, for any selection of the constants  $\xi_1, \ldots, \xi_N$ , and  $\beta_o$ , there exist constants a and b, and a sequence  $\varepsilon[n]$  with the given set of PSD properties such that

$$\sum_{i=1}^{N} \xi_i x_i[n] + \beta_0 = ax[n] + b + \varepsilon[n]. \tag{14}$$

It follows from (12) that

$$\sum_{j=1}^{N-1} c_j \cdot \phi_j[n] = \sum_{i=1}^{N} \underbrace{\left(\sum_{j=1}^{N-1} c_j \cdot a_{j,i}\right)}_{\equiv d_i} x_i[n]. \tag{15}$$

for any selection of N-1 constants,  $c_1, \ldots, c_{N-1}$ . Since (14) is satisfied for any selection of  $\xi_i$  and  $\beta_o$ , suppose  $\xi_i = d_i$  for each i, and  $\beta_o = 0$ . In this case, the left-hand side of (14) is the same as the right-hand side of (15), which implies (7). Thus, the N-1 sequences satisfy condition (b) in the theorem.

Therefore, in mismatch-shaping DACs, there are N-1 underlying sequences that, given the DAC input, determine the digital encoder outputs and, when linearly combined, produce a sequence that has the same form as the DAC output, *i.e.*,  $ax[n] + b + \varepsilon[n]$ , where the gain and offset depend on the coefficients in this linear combination, and the sequence  $\varepsilon[n]$  has the same PSD properties as the DAC noise.

In efficient mismatch-shaping DACs, none of the N-1 underlying sequences are constant for all DAC input sequences. To verify this assertion, suppose one of the digital encoder outputs were a linear combination of the other digital encoder outputs plus an offset: *i.e.*, for some j.

$$x_j[n] = \sum_{\substack{i=1\\i\neq j}}^{N} d_i \cdot x_i[n] + d_0.$$

(16)

where each  $d_i$  is a constant. As a consequence of this linear dependence, an equivalent multi-bit DAC could be implemented using fewer than N 1-bit DACs: the only difference between the original and equivalent implementations would result from the 1-bit DAC errors in each. For example, if  $x_j[n]$  were given by (16), then the jth 1-bit DAC could be removed by changing the nominal step sizes of the other 1-bit DACs according to the following: for  $i \neq j$ ,  $\Delta_i^{new} = \Delta_i^{old} + d_i \Delta_j^{old}$ .

The theorem can be used to show that the DAC noise from a given architecture has certain PSD properties. However, the corollary presented next is more convenient for this application.

Corollary 1: Given the multi-bit DAC in Figure 1.1, let  $\phi_1[n], \ldots, \phi_{N-1}[n]$ , and  $\psi[n]$  be sequences formed by taking N linearly independent, linear combinations of the digital encoder outputs with  $\psi[n] = \sum_{i=1}^{N} (\Delta_i/\Delta_D) x_i[n]$ . Then, the multi-bit DAC in Figure 1.1 produces DAC noise with a given set of PSD properties if and only if, for any selection of the N-1 constants  $c_1, \ldots, c_{N-1}$ , there exist two constants a and b, and a sequence  $\varepsilon[n]$  with the given set of PSD properties such that

$$\sum_{j=1}^{N-1} c_j \cdot \phi_j[n] = ax[n] + b + \varepsilon[n]. \tag{17}$$

**Proof:** The proof follows directly from that of the theorem as the N-1 sequences in the corollary are formed the same way as in the proof of the theorem.

Therefore, to show that the DAC noise PSD from a given multi-bit DAC has a certain property, derive the N-1 sequences,  $\phi_1[n], \ldots, \phi_{N-1}[n]$ , as described in the corollary and show that any linear combination of these sequences can be written as in (17). The N-1 sequences in the corollary result from linear combinations of the digital encoder outputs, and there are many possible choices for these sequences. However, for a given multi-bit DAC, these sequences can often be chosen to minimize the effort required to show they satisfy (17). Several examples of this application are presented in the following section.

The following corollary is more convenient than the theorem or the first corollary for proving that the DAC noise from a given architecture *does not* have certain PSD properties.

Corollary 2: The multi-bit DAC in Figure 1.1 produces DAC noise with a given set of PSD properties if and only if, for any selection of N constants,  $d_1, \ldots, d_N$ , there exist constants a and b, and a sequence  $\varepsilon[n]$  with the given set of PSD properties such that

$$\sum_{i=1}^{N} d_i \cdot x_i[n] = ax[n] + b + \varepsilon[n]. \tag{18}$$

**Proof:** By definition, the multi-bit DAC produces DAC noise with the given set of PSD properties, if and only if, for any selection of the 1-bit DAC errors, there exist two constants  $\alpha$  and  $\beta$ , and a sequence e[n] with the given set of PSD properties such that  $y[n] = \alpha x[n] + \beta + e[n]$ . The relationship between y[n] and the 1-bit DAC errors is manifest in (9) as each constant  $\xi_i$  and  $\beta_o$  are functions of the 1-bit DAC errors. Because any value of  $\xi_i$  and  $\beta_o$  can be obtained by an appropriate choice of the 1-bit DAC errors, the multi-bit DAC produces DAC noise with the given set of

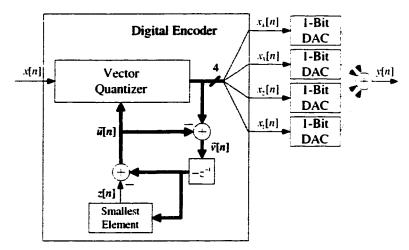

Figure 1.2: A first-order, lowpass vector feedback DAC.

PSD properties if and only if, for any selection of the constants  $\xi_1, \ldots, \xi_N$ , and  $\beta_o$ , there exist two constants  $\alpha$  and  $\beta$ , and a sequence e[n] with the given set of PSD properties such that

$$\sum_{i=1}^{N} \xi_{i} x_{i}[n] + \beta_{o} = \alpha x[n] + \beta + e[n].$$

(19)

With  $d_i \equiv \xi_i$ ,  $b \equiv \beta - \beta_o$ ,  $a \equiv \alpha$ , and  $\varepsilon[n] \equiv e[n]$ , (19) is equivalent to (18).

.

Therefore, to show that the DAC noise does not have the given PSD properties, it is sufficient to find a linear combination of the digital encoder outputs that cannot be expressed as in (18). An example of this application is also shown in the following section.

### IV. ARCHITECTURE ANALYSIS

The theorem and corollaries presented in the previous section are used in this section to analyze and compare several of the previously published multi-bit DAC architectures. Specifically, vector feedback, data weighted averaging, butterfly shuffler, tree structured, and partitioned data weighted averaging DAC architectures are considered.

### VECTOR FEEDBACK

A 5-level (i.e., N=4) example of the vector feedback DAC is shown in Figure 1.2 [2]. Its input range is  $\{-N/2, -N/2 + 1, \dots, N/2\}$ . Its 1-bit DACs all have the same nominal step size (i.e.,  $\Delta_i = \Delta_D$  for each i). The digital encoder consists of a vector quantizer, a smallest-element block, two vector adders, and a vector unit delay. The vector  $\vec{u}[n]$  consists of N elements, the ith of which is associated with the ith output bit of the digital encoder. At each sample time, n, the vector quantizer determines the x[n] + N/2 largest elements of  $\vec{u}[n]$ , and sets the associated output bits of the digital encoder high. It sets the remaining output bits low. The digital encoder calculates each element of  $\vec{u}[n]$  as

$$u_i[n] = -v_i[n-1] - z[n]. (20)$$

where

$$v_i[n] = x_i[n] - u_i[n]. (21)$$

and  $z[n] = \min_i \{-v_i[n-1]\}$ , *i.e.*, it is equal to the smallest element of  $-\vec{v}[n-1]$ .

To show that the feedback system within the digital encoder is stable, it is sufficient to show that  $u_i[n]$  and  $v_i[n]$  are bounded sequences for each value of i. Suppose that at some sample time,  $n_0$ , the largest element of  $\vec{u}[n_0]$  has a value of  $P \geq 1$ . It follows from (20) that  $u_i[n] \geq 0$  for each i and one element of  $\vec{u}[n]$  equals zero for each n. The operation of the vector quantizer implies that  $x_j[n_0] - x_i[n_0] = 1$  only when  $u_j[n_0] \geq u_i[n_0]$ . So (21) implies that

$$|v_i[n_0] - v_j[n_0]| \le \max\{|u_i[n_0] - u_j[n_0]|, 1\} \le P.$$

(22)

It follows from (20) that  $u_j[n_0+1]-u_i[n_0+1]=v_i[n_0]-v_j[n_0]$ , and since one element of  $\vec{u}[n_0+1]$  is zero. (22) implies that  $u_i[n_0+1] \leq P$  for each i. By induction,  $u_i[n]$  must be a bounded sequence for each i, and, therefore, (21) implies that  $v_i[n]$  must also be a bounded sequence for each i.

To apply Corollary 1. let

$$\phi_j[n] \equiv x_{j+1}[n] - x_j[n] \tag{23}$$

for j = 1, ..., N-1. Because all the 1-bit DACs have the same nominal step size.  $\psi[n]$ , as defined in the statement of Corollary 1, is given by

$$\psi[n] = x_1[n] + \dots + x_N[n]. \tag{24}$$

To show that (23) and (24) are linearly independent combinations of the digital encoder output sequences as required by the corollary, it is sufficient to show that, when  $x_1[n], \ldots, x_N[n]$  are linearly independent sequences, the expression

$$\sum_{j=1}^{N-1} c_j \cdot \phi_j[n] + c_N \cdot \psi[n] = 0.$$

(25)

where  $c_1, \ldots, c_N$  are constants, is only satisfied with  $c_j = 0$  for each j. Substituting (23) and (24) into (25) gives

$$\sum_{j=1}^{N} (c_{j-1} + c_j + c_N) x_j[n] + c_N \cdot x_N[n] = 0.$$

(26)

where  $c_0$  is defined to be zero. With linearly independent digital encoder outputs. (26) implies that  $c_j - c_{j-1} = c_N$  for j = 1, ..., N-1, and  $c_{N-1} = -c_N$ . Solving this difference equation gives  $c_j = j \cdot c_N$  for j = 1, ..., N-1. Since  $c_{N-1} = (N-1) c_N$  and  $c_{N-1} = -c_N$  both hold, it follows that  $c_N = 0$ . Therefore,  $c_j = 0$  for each j.

It is next shown that the choice of  $\phi_j[n]$  given by (23) satisfies (17) with a=0. b=0, and an  $\varepsilon[n]$  whose PSD is zero at  $\omega=0$ . By virtue of Corollary 1, this implies that the PSD of the DAC noise also has a zero at  $\omega=0$ , and, therefore, that the vector feedback DAC shown in Figure 1.2 is a first-order mismatch-shaping DAC.

Substituting (20) into (21) gives  $x_i[n] = v_i[n] - v_i[n-1] - z[n]$ . With (23) this implies

$$\phi_i[n] = v_{i+1}[n] - v_{i+1}[n-1] - v_i[n] + v_i[n-1].$$

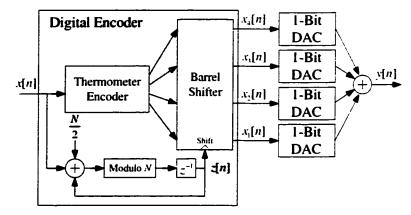

Figure 1.3: The DWA DAC.

Therefore.

$$\left| \sum_{m=0}^{n} \phi_j[m] \right| = |v_{j+1}[n] - v_j[n] - v_{j+1}[0] + v_j[0]|. \tag{27}$$

The partial sum in (27) is bounded for all n because  $v_i[n]$  is a bounded sequence for each value of i. As shown in the Appendix, this implies that the PSD of  $\phi_j[n]$  is zero at  $\omega = 0$ . It is also shown in the Appendix that any linear combination of such sequences has a PSD equal to zero at  $\omega = 0$ . Therefore, by Corollary 1, the DAC noise has this property too.

### **DWA**

A 5-level example of the DWA DAC is shown in Figure 1.3 [3], [4]. Like the vector feedback DAC, its input range is  $\{-N/2, -N/2 + 1, \dots, N/2\}$ , and all of its 1-bit DACs have the same nominal step size. The digital encoder consists of a thermometer encoder and a barrel shifter. Additionally, it consists of a modulo-N block, a unit delay, and an adder that constitute a modulo-N accumulator. At each sample time, n, the thermometer encoder, whose N outputs are binary sequences, selects its bottom x[n] + N/2 outputs high and its remaining outputs low. The modulo-N accumulator output, z[n], controls the operation of the barrel shifter as follows: with its inputs and outputs labeled 1 to N from bottom to top, the barrel

shifter, at sample time n, routes input i to output  $1 + (z[n] + i - 1) \mod N$ . Thus, the digital encoder outputs are generated by performing a modulo-N shift of the thermometer encoder outputs.

The values of z[n] and x[n] determine the digital encoder outputs at sample time n, and  $z[n+1] = (x[n] + z[n] + N/2) \mod N$ . If z[n] < z[n+1], then the high digital encoder outputs at time n are those numbered z[n] + 1, z[n] + 2, ..., z[n+1], and the remaining outputs are low. However, if z[n] > z[n+1], then the low digital encoder outputs at time n are those numbered z[n+1] + 1, z[n+1] + 2, ..., z[n], and the remaining outputs are high. If z[n+1] = z[n], then  $x[n] = \pm N/2$ , and all of the digital encoder outputs are either high or low at time n. Therefore, at each sample time, n, there is a contiguous segment of either high or low outputs of the digital encoder, and z[n] and z[n+1] determine the segment's starting and ending points.

To analyze the DAC noise using Corollary 1. let  $\phi_j[n] \equiv x_{j+1}[n] - x_j[n]$  for  $j = 1, \ldots, N-1$ . As previously shown,  $\psi[n]$ , as defined in the corollary, is given by (24), and the N linear combinations that generate  $\phi_1[n], \ldots, \phi_{N-1}[n]$ , and  $\psi[n]$  are linearly independent as required by the corollary.

As in the previous analysis, to show that the DAC noise PSD is zero at  $\omega=0$ , it is sufficient to show that the partial sum of  $\phi_j[n]$  is a bounded sequence. To show this, note that the N-1 sequences  $\phi_1[n], \ldots, \phi_{N-1}[n]$  detect the edges -i.e., starting and ending points—of the contiguous segment of high or low digital encoder outputs. If  $x[n] = \pm N/2$ , there are no edges to detect and  $\phi_j[n] = 0$  for each j. However, if  $x[n] \neq \pm N/2$ ,  $\phi_j[n]$  is nonzero only when j corresponds to an edge of the contiguous segment:

$$\phi_{j}[n] = \begin{cases} -1, & \text{if } j = z[n]; \\ 1, & \text{if } j = z[n+1]; \\ 0, & \text{otherwise.} \end{cases}$$

(28)

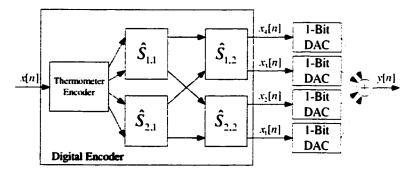

Figure 1.4: The butterfly shuffler DAC.

This implies that the nonzero samples of  $\phi_j[n]$  alternate between -1 and 1, and the partial sum of  $\phi_j[n]$  is a bounded sequence:

$$\left|\sum_{m=0}^{n} \phi_j[m]\right| \le 1. \tag{29}$$

Therefore, the DAC noise PSD is also zero at  $\omega = 0$ .

### **BUTTERFLY SHUFFLER**

An example 5-level butterfly shuffler DAC is shown in Figure 1.4 [5]. Like the previously analyzed DACs, its input range is  $\{-N/2, -N/2 + 1, \dots, N/2\}$ , and all of its 1-bit DACs have the same nominal step size. Unlike the previously analyzed DACs, the butterfly shuffler DAC requires that N be a power of 2: i.e.,  $N = 2^b$ , where b is a positive integer. The digital encoder consists of a thermometer encoder and N swapper cells, which are labeled  $\hat{S}_{l,m}$  and positioned in a matrix with  $l = 1, \dots, 2^{b-1}$ , and  $m = 1, \dots, b$ , corresponding to the row and column numbers, respectively. The input and output sequences of each swapper cell are 1-bit sequences: the values of each are taken to be 1/2 and -1/2 at sample times when the sequence is high and low, respectively. At each sample time, n, each swapper cell determines its outputs by routing its inputs either straight through or swapped. The thermometer encoder, whose operation is described in the previous sub-section, is not a necessary component as it can be replaced by any encoder that

has N 1-bit outputs and ensures that exactly x[n] + N/2 of its outputs are high at each sample time, n.

Let  $\hat{x}_{2l-1,m}[n]$  and  $\hat{x}_{2l,m}[n]$  denote the top and bottom inputs of  $\hat{S}_{l,m}$ , respectively. Using  $\hat{S}_{1,1}$  in Figure 1.4 as an example.

$$\dot{x}_{1,2}[n] = \frac{1}{2} \left( \hat{x}_{1,1}[n] + \hat{x}_{2,1}[n] + \hat{s}_{1,1}[n] \right). \tag{30}$$

and

$$\hat{x}_{3,2}[n] = \frac{1}{2} \left( \hat{x}_{1,1}[n] + \hat{x}_{2,1}[n] - \hat{s}_{1,1}[n] \right). \tag{31}$$

where  $\hat{s}_{1,1}[n]$  is called a swapper sequence. It is generated within  $\hat{S}_{1,1}$  and is restricted to the values  $\{-1,0,1\}$ . Thus, each swapper cell  $\hat{S}_{l,m}$  uses its swapper sequence,  $\hat{s}_{l,m}[n]$ , as in (30) and (31) to determine its outputs. In the first-order butterfly shuffler DAC, each swapper cell alternates between swapping and not swapping so that

$$\left| \sum_{k=0}^{n} \hat{s}_{l,m}[k] \right| \le 1. \tag{32}$$

which, as shown in the Appendix, implies that the PSD of each swapper sequence is zero at  $\omega = 0$ .

Generalizing (30) and (31) to the other swapper cells in Figure 1.4. the top digital encoder output in the figure can be written as

$$x_4[n] = \frac{1}{4} \left( \sum_{k=1}^4 \hat{x}_{k,1}[n] + \hat{s}_{1,1}[n] + \hat{s}_{2,1}[n] \right) + \frac{1}{2} \hat{s}_{1,2}[n]. \tag{33}$$

Since x[n] + N/2 of the thermometer encoder outputs are high at time n, it follows that  $\sum_{k=1}^{4} \hat{x}_{k,1}[n] = x[n]$ . This and (33) imply

$$x_4[n] = \frac{1}{4} (x[n] + \hat{s}_{1,1}[n] + \hat{s}_{2,1}[n]) + \frac{1}{2} \hat{s}_{1,2}[n]. \tag{34}$$

Therefore, the top digital encoder output is a linear combination of x[n] and the swapper sequences. It follows by similar reasoning that this holds for every digital

Figure 1.5: The tree structured DAC.

encoder output, and in general with  $N=2^b$ .

$$x_{i}[n] = x[n]/N + \sum_{l=1}^{2^{b-1}} \sum_{m=1}^{b} c_{l,m}^{(i)} \cdot \hat{s}_{l,m}[n].$$

(35)

where each  $c_{l,m}^{(i)}$  is a constant that is either  $\pm 1/2^{b-m+1}$  or 0.

To apply Corollary 1, once again let  $\phi_j[n] \equiv x_{j+1}[n] - x_j[n]$  for  $j = 1, \ldots, N-1$ . As previously shown, because all the 1-bit DACs have the same nominal step size, these N-1 sequences satisfy the linear independence condition of the corollary. It follows from (32) and (35) that, for each j,  $\phi_j[n]$  is a linear combination of swapper sequences whose PSDs are zero at  $\omega = 0$ , which, as shown in the Appendix, implies that the PSD of  $\phi_j[n]$  is zero at  $\omega = 0$ . Therefore, the DAC noise PSD is also zero at  $\omega = 0$ .

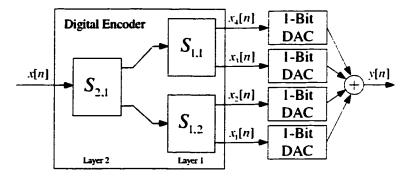

### TREE STRUCTURED

An example 5-level tree structured DAC is shown in Figure 1.5 [6]. Like the previously analyzed DACs, its input range is  $\{-N/2, -N/2 + 1, \dots, N/2\}$ , and all of its 1-bit DACs have the same nominal step size. This DAC requires that N be a power of two. The digital encoder consists of *switching blocks*, which are labeled  $S_{k,r}$ , where  $k = 1, \dots, b$ , denotes the layer number, and  $r = 1, \dots, 2^{b-k}$ , denotes the depth in the layer. If the input to  $S_{k,r}$  is denoted  $x_{k,r}[n]$  and each sequence  $x_i[n]$  is

also denoted  $x_{0,i}[n]$ , the switching blocks are interconnected such that the top and bottom outputs of  $S_{k,r}$  are  $x_{k-1,2r-1}[n]$  and  $x_{k-1,2r}[n]$ , respectively. The outputs of  $S_{k,r}$  are given by

$$x_{k-1,2r-1}[n] = \frac{1}{2} \left( x_{k,r}[n] + s_{k,r}[n] \right). \tag{36}$$

and

$$x_{k-1,2r}[n] = \frac{1}{2} \left( x_{k,r}[n] - s_{k,r}[n] \right). \tag{37}$$

where  $s_{k,r}[n]$  is called the *switching sequence* and is generated within  $S_{k,r}$ .

Analogously to the butterfly shuffler DAC, the switching blocks in the first-order tree structured DAC ensure that

$$\left| \sum_{m=0}^{n} s_{k,r}[m] \right| \le 1. \tag{38}$$

which, as shown in the Appendix, implies that the PSD of  $s_{k,r}[n]$  is zero at  $\omega = 0$ . By recursively solving the switching block outputs in (36) and (37) as functions of the switching sequences and the DAC input x[n], it follows that

$$x_i[n] = x[n]/N + \sum_{k=1}^{b} \sum_{r=1}^{2^{b-k}} d_{k,r}^{(i)} \cdot s_{k,r}[n].$$

(39)

where each  $d_{k,r}^{(i)}$  is a constant that is either  $\pm 1/2^k$  or 0.

Once again, Corollary 1 can be applied by using the N-1 sequences  $\phi_j[n] \equiv x_{j+1}[n] - x_j[n]$  for  $j = 1, \ldots, N-1$ . As previously shown, the N-1 sequences satisfy the linear independence condition in the corollary. The PSD of each  $\phi_j[n]$  sequence is zero at  $\omega = 0$  because, from (39), each sequence results from a linear combination of switching sequences whose PSDs are zero at  $\omega = 0$ . Therefore, the DAC noise PSD is also zero at  $\omega = 0$ .

### QUALITATIVE COMPARISONS

Comparisons among mismatch-shaping DACs can be made using the necessary and sufficient condition presented in the theorem. One comparison can be made concerning how easily each of the four previously analyzed DACs combat harmonic distortion in its DAC noise. In the butterfly shuffler and tree structured DACs, the DAC noise is a linear combination of shaped sequences—i.e., swapper and switching sequences—that are generated within their digital encoders. Therefore, as shown in the Appendix, if these shaped sequences have bounded PSDs, then their DAC noise PSDs are also bounded and thus do not contain spurious tones. This can be accomplished by incorporating randomness in the shaped sequences to prevent any tonal behavior. The relative ease for which this is accomplished is shown in [8] where pseudorandom sequences are employed by the switching blocks in both first-and second-order, lowpass tree structured DACs to eliminate harmonic distortion in the DAC noise.

However, the vector feedback and DWA DACs obtain DAC noise with the given set of PSD properties without explicitly generating sequences with these properties. This indirect approach for spectrally shaping the DAC noise makes it more difficult to eliminate or reduce spurious tones. To remove spurious tones in the vector feedback DAC, randomness must somehow be incorporated into the vector quantizer's operation, but, to the knowledge of the authors, no such vector quantizer has been demonstrated to date. To remove or reduce spurious tones in the DWA DAC, its architecture must be changed. Most variants of the DWA DAC are designed to reduce, relative to the DWA DAC, the harmonic distortion in the DAC noise. Examples of such DWA variants are presented in [7],[9], and [10]. To successfully reduce harmonic distortion, each of these published first-order architectures requires that the multi-bit DAC input includes a random component—e.g., the quantization noise from a  $\Delta\Sigma$  modulator. This is not required in the previously mentioned first-order, tree structured DAC whose DAC noise PSD is bounded regardless of

the DAC input [11].

Another comparison can be made concerning the ease for which a mismatch-shaping DAC obtains higher-order-i.e., greater than first-order—spectral shaping of the DAC noise. Such DACs are desirable because the DAC noise in a higher-order DAC usually has less signal-band power. This comparison does not include DWA because it is inherently a first-order DAC. The theorem states that, given the DAC input, N-1 sequences are required to generate the digital encoder outputs in a mismatch-shaping DAC. However, with  $N=2^b$ , where b is a positive integer, the butterfly shuffler DAC requires  $b \cdot N/2$  swapper sequences, which, for b>1, are more than necessary as  $b \cdot N/2 > N-1$ . Additionally, as b increases, the number of extra sequences utilized by the DAC grows at a faster rate than an exponential function. Each swapper sequence depends on its swapper cell input, which depends on the DAC input. This dependence and the extra swapper sequences makes it difficult to ensure that each swapper sequence has the desired PSD properties in higher-order implementations.

For example, to implement a second-order, lowpass butterfly shuffler DAC, it follows from [8] that each swapper sequence must satisfy the following:

$$\left| \sum_{j=0}^{n} \sum_{k=0}^{j} \hat{s}_{l,m}[k] \right| \le B. \tag{40}$$

where B is a constant. Because the value of each swapper cell output is either -1/2 or 1/2 at each sample time. n, it follows that

$$\hat{s}_{l,m}[n] = \begin{cases} \pm 1, & \text{if } \hat{x}_{2l-1,m}[n] \neq \hat{x}_{2l,m}[n]; \\ 0, & \text{if } \hat{x}_{2l-1,m}[n] = \hat{x}_{2l,m}[n]. \end{cases}$$

(41)

Therefore, if the N inputs to the column-one swapper cells are thermometer encoded as in Figure 1.4, then the column-one swapper sequences are restricted as follows:

$$\hat{s}_{l,1}[n] = \begin{cases} \pm 1, & \text{if } x[n] = N/2 - (2l - 1); \\ 0, & \text{otherwise.} \end{cases}$$

(42)

At each sample time, at most one of the  $2^{b-1}$  swapper sequences in the first column is nonzero; the choice of which is determined by the DAC input. As b increases, this dependence on the DAC input makes it more difficult for these swapper sequences to satisfy (40) and has prohibited the implementation of the second-order, lowpass butterfly shuffler DAC.

However, the vector feedback and tree structured DACs process N and N-1 internal sequences, respectively, to generate their digital encoder outputs. Because, for b > 2, these DACs process fewer internal sequences than the butterfly shuffler DAC, their internal sequences and DAC noise have less dependence on the DAC input, which enables the implementation of higher-order DACs. For example, in the tree structured DAC, the layer that directly processes the DAC input, layer b, only has one switching block as opposed to the  $2^{b-1}$  swapper cells in the first column of the butterfly shuffler DAC. For the switching blocks presented in [8], the switching sequence is restricted as follows:

$$s_{k,r}[n] = \begin{cases} \pm 1, & \text{if } x_{k,r}[n] + 2^{k-1} \text{ is odd:} \\ 0, & \text{if } x_{k,r}[n] + 2^{k-1} \text{ is even.} \end{cases}$$

(43)

Therefore, the switching sequence in layer b depends only on the parity of the DAC input, which is much less restrictive than the dependence exhibited by the column-one swapper sequences shown in (42). Examples of second-order lowpass implementations of the vector-feedback and tree structured DACs are presented in [12] and [13], respectively.

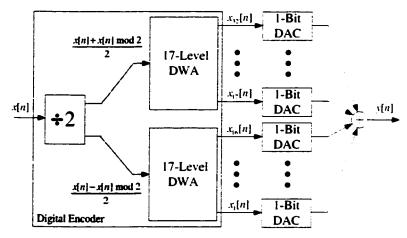

# PARTITIONED DWA

The partitioned DWA (P-DWA) DAC, shown in Figure 1.6, was designed to not only suppress the DAC noise power near  $\omega = 0$ , but to reduce, in comparison to the DWA DAC, the spurious tones in the DAC noise [7]. Its input range is

Figure 1.6: The partitioned DWA DAC.

$\{-16, -15, \ldots, 16\}$ . All of its 1-bit DACs have the same nominal step size. The digital encoder consists of two 17-level DWA digital encoders and a *divide-by-two* block. The top output of the divide-by-two block is x[n]/2 rounded up to the nearest integer (i.e.,  $\lceil x[n]/2 \rceil$ ), and the bottom output is x[n]/2 rounded down to the nearest integer (i.e.,  $\lfloor x[n]/2 \rfloor$ ).

Corollary 2 is applied next to show that the DAC noise PSD is *not* zero at  $\omega = 0$ . Since the difference between the outputs of the divide-by-two block is one when x[n] is odd and zero otherwise, it follows that

$$\sum_{i=17}^{32} x_i[n] - \sum_{i=1}^{16} x_j[n] = x[n] \mod 2.$$

(44)

By Corollary 2, if the above linear combination cannot be written as  $ax[n]+b+\varepsilon[n]$ , where a and b are constants and the PSD of  $\varepsilon[n]$  is zero at  $\omega=0$ , then the DAC noise PSD is not zero at  $\omega=0$ . Therefore, from (44), it is sufficient to show that, for some x[n], the PSD of the sequence

$$\varepsilon[n] \equiv (x[n] \bmod 2) - (ax[n] + b). \tag{45}$$

is not zero at  $\omega = 0$  for any choice of the constants a and b. Since

$$x[n] = 2 \left| \frac{x[n]}{2} \right| + (x[n] \mod 2).$$

(46)

Figure 1.7: Output noise PSD from a simulation of a 2nd-order, analog  $\Delta\Sigma$  modulator using the partitioned DWA DAC.

# (45) can be written as

$$\varepsilon[n] = (1-a)\left(x[n] \bmod 2\right) - \left(2a \left\lfloor \frac{x[n]}{2} \right\rfloor + b\right). \tag{47}$$

The DAC input, x[n], can be chosen so that the sequences  $2(x[n] \mod 2) - 1$  and  $\lfloor x[n]/2 \rfloor$  are white and uncorrelated. For this x[n], (47) implies that the PSD of  $\varepsilon[n]$  is not zero at  $\omega = 0$  for any selection of the constants a and b. Therefore, by Corollary 2, the DAC noise PSD is also not zero at  $\omega = 0$ .

Figure 1.7 displays the output noise PSD from a behavioral simulation of a second-order, analog  $\Delta\Sigma$  modulator that employs the P-DWA DAC. The  $\Delta\Sigma$  modulator input was a -1dB (relative to full scale) sinusoid with frequency 0.0015 $f_s$ , where  $f_s$  is the sample rate. The PSD units are dB relative to  $\Delta^2$ , where  $\Delta$  is the step size of the analog-to-digital converter within the  $\Delta\Sigma$  modulator. The frequency axis is normalized with respect to the sample rate. The 1-bit DAC errors were chosen as independent Gaussian random variables with a standard deviation of 1% of the 1-bit DAC's nominal step size.

The output noise in the simulation includes the DAC noise and quantization noise. The simulation shows that, as a result of the DAC noise, the output noise PSD is not zero at  $\omega = 0$ . However, the simulation suggests that, compared to conventional DWA, the DAC noise in this implementation has less harmonic distortion. The reduced harmonic distortion is a result of the randomness in x[n], which causes  $(x[n] \mod 2)/2$  to act as an additive and subtractive dither sequence that, as shown in Figure 1.6, is fed into top and bottom DWA DACs, respectively.

#### V. CONCLUSION

Necessary and sufficient conditions for mismatch shaping with a general multi-bit DAC have been presented, proved, and discussed. For the DAC noise to have certain PSD properties, the conditions show that there must be N-1 underlying sequences in the general multi-bit DAC that, when linearly combined, produce a sequence that consists of an offset, a scaled version of the multi-bit DAC input, and another sequence that has the given PSD properties. As example applications, the conditions have been used to show that the DAC noise PSDs of four widely-used lowpass DACs are zero at  $\omega=0$  and that the DAC noise PSD of another lowpass DAC is not zero at  $\omega=0$ . Additionally, the theory has been used to compare the ease for which several DACs combat spurious tones in their DAC noise and obtain higher-order shaped DAC noise.

# **APPENDIX**

Two lemmas are presented below that supplement the analyses in Section IV. The first lemma proves that if a sequence  $\gamma[n]$  has a partial sum that is a bounded sequence, then the PSD of  $\gamma[n]$  is zero at  $\omega = 0$ . The second lemma proves an inequality for PSDs that is used to show that an arbitrary linear combination of

sequences whose PSDs are zero or bounded at a given frequency gives rise to a sequence whose PSD is also zero or bounded, respectively, at that frequency. It is assumed throughout that the PSDs exist for all sequences considered.

**Lemma 1:** Let  $\gamma[n]$  be a sequence whose partial sum is bounded in magnitude by a constant B for all n: *i.e.*.

$$\left|\sum_{m=0}^{n} \gamma[m]\right| \le B. \tag{48}$$

for all n. Then, the PSD of  $\gamma[n]$  (if it exists) is zero at  $\omega = 0$ .

**Proof:** As proved in [14], the PSD of  $\gamma[n]$  is given by

$$S_{\gamma,\gamma}\left(e^{j\omega}\right) = \lim_{M \to \infty} \frac{1}{M} E\left\{ \left| \Gamma_M\left(e^{j\omega}\right) \right|^2 \right\}. \tag{49}$$

where  $E\{\cdot\}$  is the expectation operator, and  $\Gamma_M\left(e^{j\omega}\right)$  is the M-point Fourier transform of  $\gamma[n]$ :

$$\Gamma_M\left(e^{j\omega}\right) = \sum_{n=0}^{M-1} \gamma[n]e^{-j\omega n}.$$

(50)

Evaluating the PSD at  $\omega = 0$  gives

and z[n] = x[n] + y[n], then

$$S_{\gamma,\gamma}\left(e^{j0}\right) = \lim_{M \to \infty} \frac{1}{M} E\left\{ \left| \sum_{n=0}^{M-1} \gamma_i[n] \right|^2 \right\}. \tag{51}$$

However, from (48), the partial sum of  $\gamma[n]$  in the above expression is bounded in magnitude by B: therefore,

$$S_{\gamma,\gamma}\left(e^{j0}\right) \le \lim_{M \to \infty} \frac{B^2}{M} = 0. \tag{52}$$

Because  $S_{\gamma,\gamma}\left(e^{j\omega}\right)$  is nonnegative for all  $\omega$ , (52) implies that  $S_{\gamma,\gamma}\left(e^{j0}\right)=0$ .

**Lemma 2:** If  $S_{x,x}\left(e^{j\omega}\right)$  and  $S_{y,y}\left(e^{j\omega}\right)$  are the PSDs of x[n] and y[n], respectively.

$$S_{z,z}\left(e^{j\omega}\right) \le 2\left(S_{x,x}\left(e^{j\omega}\right) + S_{y,y}\left(e^{j\omega}\right)\right). \tag{53}$$

where  $S_{z,z}\left(e^{j\omega}\right)$  is the PSD of z[n].

**Proof:** Let  $X_M(e^{j\omega})$ .  $Y_M(e^{j\omega})$ , and  $Z_M(e^{j\omega})$  be the M-point Fourier transforms of x[n], y[n], and z[n], respectively—i.e..

$$X_M\left(e^{j\omega}\right) = \sum_{n=0}^{M-1} x[n]e^{-j\omega n}.$$

(54)

and likewise for the Fourier transforms of y[n] and z[n]. The Cauchy-Schwartz inequality implies that

$$|a+b|^2 \le 2(|a|^2+|b|^2).$$

(55)

where a and b are complex numbers. Therefore, it follows from the linearity of the Fourier Transform that, for every  $\omega$ .

$$\left|Z_{M}\left(e^{j\omega}\right)\right|^{2} \leq 2\left(\left|X_{M}\left(e^{j\omega}\right)\right|^{2} + \left|Y_{M}\left(e^{j\omega}\right)\right|^{2}\right). \tag{56}$$

As shown in [14].

$$S_{z,z}\left(e^{j\omega}\right) = \lim_{M \to \infty} \frac{1}{M} E\left\{ \left| Z_M\left(e^{j\omega}\right) \right|^2 \right\}. \tag{57}$$

and likewise for PSDs of x[n] and y[n], where  $E\{\cdot\}$  is the expectation operator. Therefore, (56), (57), and the linearity of the expectation operator imply (53).

Therefore, it follows from (53) that if, at some frequency  $\omega_o$ ,  $S_{x,x}\left(e^{j\omega_o}\right)=0$ , and  $S_{y,y}\left(e^{j\omega_o}\right)=0$ , then  $S_{z,z}\left(e^{j\omega_o}\right)=0$  because the PSD is always nonnegative. Thus, the sum of two sequences whose PSDs are zero at some frequency gives rise to a sequence whose PSD is also zero at that frequency. Additionally, if the PSDs of x[n] and y[n] are bounded functions—there exists a constant B such that  $S_{x,x}\left(e^{j\omega}\right)\leq B$ , and  $S_{y,y}\left(e^{j\omega}\right)\leq B$  for all  $\omega$ —then (53) implies that the PSD of z[n] is also a bounded function:  $S_{z,z}\left(e^{j\omega}\right)\leq 4B$ . Therefore, by mathematical induction, any linear combination of sequences whose PSDs are zero or bounded at

a given frequency give rise to another sequence whose PSD is also zero or bounded, respectively, at that frequency.

#### CHAPTER ACKNOWLEDGMENT

The text of Chapter 1 consists of material that has been submitted for publication as a Regular Paper in the *IEEE Transactions on Circuits and Systems-II:*Analog and Digital Signal Processing. The dissertation author was the primary researcher. Ian Galton supervised the research which forms the basis of the chapter.

#### REFERENCES

- 1. L. Hernández. "A model of mismatch-shaping D/A conversion for linearized DAC architectures." *IEEEc Trans. on Circuits and Systems—I: Fundamental Theory and Applications.* vol. 45. no. 10. pp. 1068-1076. Oct. 1998.

- 2. R. Schreier, B. Zhang, "Noise-shaped multi-bit D/A converter employing unit elements," *Electronics Letters*, vol. 31, no. 20, pp. 1712-1713, Sept. 28, 1995.

- 3. M. J. Story, "Digital to analogue converter adapted to select input sources based on a preselected algorithm once per cycle of a sampling signal," U.S. Patent No. 5.138.317. Aug. 11, 1992.

- 4. R. T. Baird, T. S. Fiez, "Linearity enhancement of multi-bit ΔΣ A/D and D/A converters using data weighted averaging," *IEEE Trans. on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 42, no. 12, pp. 753-762, Dec. 1995.

- 5. R. W. Adams, T. W. Kwan, "Data-directed scrambler for multi-bit noise shaping D/A converters," U.S. Patent No. 5,404,142, Apr. 4, 1995.

- I. Galton, "Spectral shaping of circuit errors in digital-to-analog converters," IEEE Trans. on Circuits and Systems II: Analog and Digital Signal Processing, vol. 44, no. 10, pp. 808-817, Oct. 1997.

- 7. K. Vleugels, S. Rabii, B.A. Wooley, "A 2.5 V sigma-delta modulator for broad-band communications applications," *IEEE Journal of Solid-State Circuits*, vol. 36, no. 12, pp. 1887-1899, Dec. 2001.

- 8. J. Welz, I. Galton, E. Fogleman, "Simplified logic for first-order and second-order

- mismatch-shaping digital-to-analog converters," *IEEE Transaction on Circuits and Systems—II: Analog and Digital Signal Processing*, vol. 48, no. 11, Nov. 2001.

- 9. I. Fujimori, L. Longo, A. Hairapetian, K. Seiyama, S. Kosic, J. Cao, S. Chan, "A 90dB SNR, 2.5 MHz output-rate ADC using cascaded multibit delta-sigma modulation at 8x oversampling ratio," *IEEE Journal of Solid-State Circuits*, vol. 35, no. 12, pp. 1820-1828, Dec. 2000.

- R. Radke, A. Eshraghi, T. Fiez, "A spurious-free delta-sigma DAC using rotated data weighted averaging," Proceedings of the 1999 IEEE Custom Integrated Circuits Conference, pp. 125-128, May, 1999.

- 11. J. Welz, I. Galton, "The mismatch-noise PSD from a tree-structured DAC in a second-order delta-sigma modulator with a midscale input," *Proceedings of the IEEE International Conference on Acoustics, Speech, and Signal Processing*, vol. 4, May 7-11, 2001.

- 12. A. Yasuda, H. Tanimoto, T. Iida, "A third-order  $\Delta\Sigma$  modulator using second-order noise-shaping dynamic element matching," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 1879-1886, Dec. 1998.

- 13. E. Fogleman, J. Welz, I. Galton, "An audio ADC delta-sigma modulator with 100dB SINAD and 102dB DR using a second-order mismatch-shaping DAC," *IEEE Journal of Solid State Circuits*, vol. 36, no. 3, pp. 339-48, March 2001.

- 14. S. Haykin. Adaptive Filter Theory. Prentice Hall. New Jersey. 1996.

# Simplified Logic for First-Order and Second-Order Mismatch-Shaping Digital-to-Analog Converters

Jared Welz, Ian Galton, Eric Fogleman

Abstract—Mismatch-shaping DACs have become widely used in high-performance delta-sigma data converters because they facilitate delta-sigma modulators with multibit quantization. Relative to single-bit quantization, multibit quantization significantly relaxes the analog circuit performance necessary to achieve a given level of data converter precision, but significant digital logic is required to perform the mismatch shaping. In modern VLSI processes optimized for digital circuitry, this tends to be a good tradeoff in terms of both area and power consumption. It is nonetheless desirable to minimize the digital complexity as much as possible. Moreover, in delta-sigma ADCs the mismatch-shaping logic is in the feedback path of the delta-sigma modulator, so it is essential to maintain a sufficiently small propagation delay through the mismatch-shaping logic. This paper presents and analyzes several variations of the switching blocks within a tree-structured mismatch-shaping DAC that result in the most hardware-efficient first-order and second-order mismatch-shaping DAC implementations yet known to the authors. The variations presented allow designers to trade off complexity for propagation-delay reduction so as to tailor designs to specific applications.

#### I. INTRODUCTION

$oldsymbol{\Lambda} oldsymbol{\Sigma}$  data converters, both  $oldsymbol{\Delta} oldsymbol{\Sigma}$  analog-to-digital converters (ADCs) and  $oldsymbol{\Delta} oldsymbol{\Sigma}$  digital-to-analog converters (DACs), coarse quantization is used in conjunction

with quantization-noise shaping and filtering to achieve high-precision data conversion. In both cases, coarse DACs are required. Unlike the error introduced by the coarse quantization, the error introduced by at least one of the coarse DACs in a  $\Delta\Sigma$  data converter is not attenuated inside the data converter's signal band. In switched-capacitor implementations, most of the DAC error arises from static capacitor mismatches, which give rise to step-size mismatches in the multibit DACs. The resulting step-size mismatches are memoryless functions of the DAC's input, so the DAC can be viewed as an ideal DAC followed by a memoryless nonlinear function. The nonlinearity tends to fold out-of-band quantization noise into the signal band thereby limiting the overall accuracy of the data converter.

To avoid this problem, many  $\Delta\Sigma$  data converters employ 1-bit quantization. With 1-bit quantization, the coarse DAC is implemented by a 1-bit DAC. Since a 1-bit DAC only generates two levels, it only has one step, and so it is inherently linear. However, with 1-bit quantization in the  $\Delta\Sigma$  modulator, quantization-noise shaping must be limited to maintain the  $\Delta\Sigma$  modulator's stability. Additionally, the power of the quantization noise in the 1-bit  $\Delta\Sigma$  modulator exceeds that of its input, so  $\Delta\Sigma$  data converters with 1-bit quantization are extremely sensitive to any nonlinearity or timing error, such as op-amp slewing or clock jitter, which can fold this quantization noise into the signal band.

To avoid these problems, multibit mismatch-shaping DACs have been developed [1]-[52]. In these DACs, digital logic is used to scramble the DAC capacitor or current-source connections in such a fashion that the error introduced by the device mismatches, referred to as DAC noise, is suppressed within the data converter's signal band. For lowpass mismatch-shaping DACs, the DAC noise is suppressed near dc so that its power spectral density (PSD) is shaped like the magnitude response of

a first-order, or in some cases, second-order highpass filter. The five main classes of mismatch-shaping DACs include individual-level averaging (ILA) [11]-[12], vector feedback [13]-[16], data-weighted averaging (DWA) [17]-[31], butterfly shuffler [32]-[37], and tree-structured [38]-[44]. The criteria used to compare these DACs include complexity, propagation delay, spurious-tone avoidance, and the order, or degree, of DAC noise suppression.

In [40], a tree-structured mismatch-shaping DAC is introduced that has led to the most efficient implementations of dithered first- and second-order mismatchshaping DACs known to the authors [43], [44]. Moreover, the first-order treestructured DAC is the only one for which dither is known to completely eliminate spurious tones in its DAC noise [46]. This paper furthers the development of this DAC by presenting new implementations of its digital logic that are more hardware efficient and have less propagation delay than those presented in [40]. The digital logic is first partitioned into functional blocks, one of which determines the shape of the DAC noise's PSD and another that is responsible for the digital logic's propagation delay. The hardware for the digital logic is presented through interchangeable variations of these functional blocks so that the DAC can be tailored to meet varying specifications for signal-band DAC noise power, propagation delay. and complexity. Efficient first and second-order mismatch-shaping logic are presented and the resulting DAC noise from each is analyzed to show it has the desired spectral shape. Additionally, medium-speed and high-speed implementations of the DAC are presented that offer a tradeoff between propagation delay and complexity.

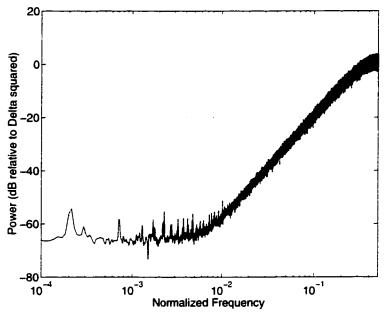

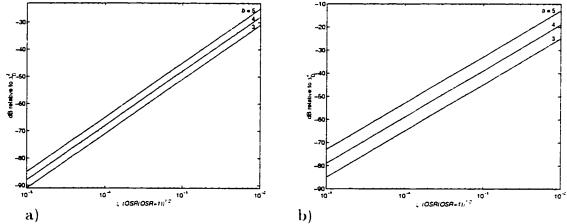

This paper is divided into six sections. Section II reviews the tree-structured DAC and presents the functional partitioning of its digital logic. Additionally, this section presents an example application of a 5-bit, second-order ADC  $\Delta\Sigma$  modulator

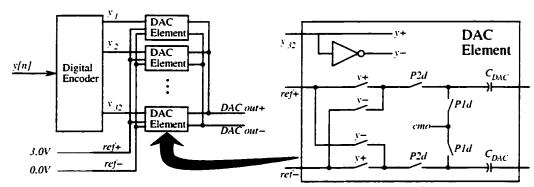

Figure 2.1: An example second-order, 33-level, lowpass analog  $\Delta\Sigma$  modulator realized with switched capacitors.

Figure 2.2: A 33-level mismatch-shaping DAC with switched capacitor DAC elements.

that is used throughout the paper to illustrate the DAC's performance and complexity. Section III presents and analyzes the first-order and second-order mismatch-shaping logic, while Section IV presents the medium-speed and high-speed implementations of the DAC. Section V presents a hardware comparison between the different tree-structured DAC implementations and other mismatch-shaping DACs presented in literature.

# II. THE TREE-STRUCTURED DAC

#### THE $\Delta\Sigma$ MODULATOR APPLICATION

The 5-bit ADC  $\Delta\Sigma$  modulator presented in [43] is shown in Figure 2.1. It consists of two delayed switched-capacitor integrators, a 33-level flash ADC, and

two 33-level DACs. As shown in Figures 2.1 and 2.2, each 33-level DAC consists of a bank of 32 *DAC elements* and a shared digital encoder whose outputs,  $y_i[n]$  ( $i=1,\ldots,32$ ), are 1-bit sequences. Each DAC element can be viewed as a 1-bit DAC whose analog output is a charge packet applied to the summing node of an integrator. A DAC element is said to be "selected high" when its input is high: otherwise it is said to be "selected low". For convenience, the output of the ADC, y[n], is interpreted as an integer between 0 and 32. For each ADC output sample, the digital encoder chooses which y[n] of the DAC elements to select high and which (32 - y[n]) of the DAC elements to select low. In other words, if  $y_i[n]$  is interpreted numerically as one when high and zero when low, the DAC encoder ensures that  $y[n] = y_1[n] + \cdots + y_{32}[n]$ .

Mismatches among the capacitor values of the DAC elements cause the output of each multibit DAC to be a nonlinear function of its input. The resulting nonlinear error is represented, without approximation, as an additive noise source referred to as DAC noise. As shown in Figure 2.1, an output from one of the DACs is added to the  $\Delta\Sigma$  modulator's input. Thus, the  $\Delta\Sigma$  modulator does not attenuate any of the signal-band noise power from this DAC. However, the digital encoder can select the DAC elements such that most of the DAC noise power resides outside of the signal band.

To demonstrate the improvements that are realized by mismatch shaping, the DAC presented in [44] was tested with and without the mismatch shaping. The input for each test was a 1.5kHz. -1dB (relative to full scale) sinusoid. With mismatch shaping, the resultant signal-to-noise-and-distortion ratio (SINAD) was 100dB, whereas without mismatch shaping, the resultant SINAD was 64dB. In general, the tradeoff for the improved performance is the additional hardware and

Figure 2.3: The 33-level tree-structured digital encoder.

Figure 2.4: The switching block  $S_{k,r}$ .

propagation delay incurred by the digital encoder. However, the propagation delay of the digital encoder only affects the design of high-speed  $\Delta\Sigma$  data converters. Examples of commercially available data converters that employ mismatch-shaping DACs to a similar advantage are presented in [47]-[52].

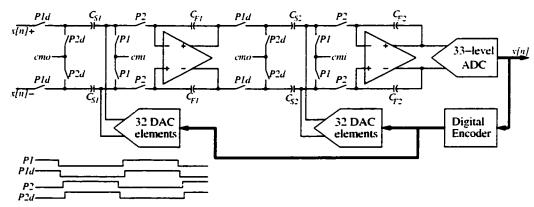

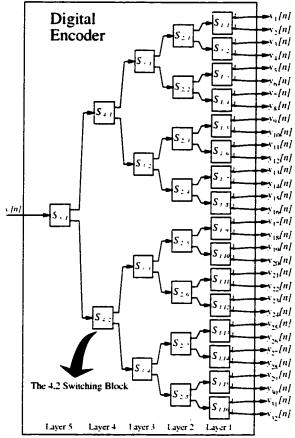

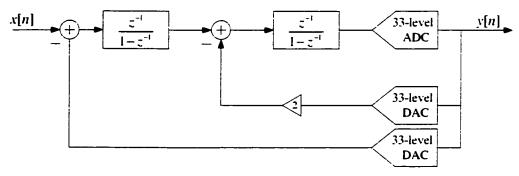

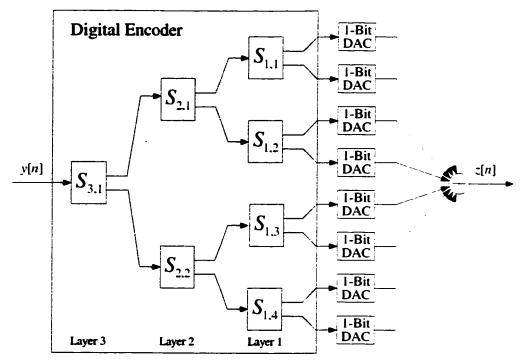

# THE TREE-STRUCTURED DIGITAL ENCODER

The architecture for a 33-level, tree-structured digital encoder is shown in Figure

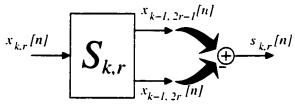

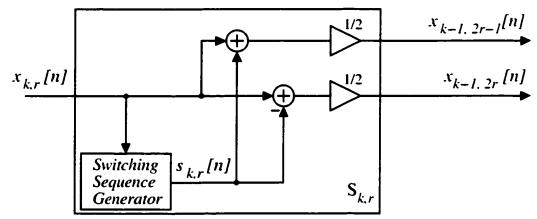

2.3. The nodes of this digital encoder are called switching blocks. Each switching block is labeled  $S_{k,r}$ , where k and r represent the switching block's layer number and position within the layer, respectively. Each switching block  $S_{k,r}$  has a single input, which is denoted  $x_{k,r}[n]$ , and two outputs. If each digital encoder output sequence  $y_i[n]$  is also denoted  $x_{0,i}[n]$ , then the switching blocks are interconnected such that the top output of  $S_{k,r}$  is  $x_{k-1,2r-1}[n]$  and the bottom output is  $x_{k-1,2r}[n]$ . The switching sequence  $s_{k,r}[n]$  is defined as the difference between the top and bottom output sequences of  $S_{k,r}$ :

$$s_{k,r}[n] = x_{k-1,2r-1}[n] - x_{k-1,2r}[n].$$

(1)

Figure 2.4 illustrates the input and output sequences of  $S_{k,r}$  along with the relationship between its switching sequence and output sequences.

As shown in [40], the DAC noise is a linear combination of the switching sequences. In general, for a DAC of the type shown in Figure 2.3 with  $2^b$  DAC elements, the output can be written as

$$u[n] = \gamma y[n] + \beta + e[n]. \tag{2}$$

where

$$e[n] = \sum_{k=1}^{b} \sum_{r=1}^{2^{b-k}} \Delta_{k,r} s_{k,r}[n].$$

(3)

and  $\gamma$ ,  $\beta$ , and  $\Delta_{k,r}$  are constants that are functions of the inevitable, static errors that result from process variations during VLSI circuit fabrication.