| Design Details                  |                      |         |                    |                             |         |                 |  |

|---------------------------------|----------------------|---------|--------------------|-----------------------------|---------|-----------------|--|

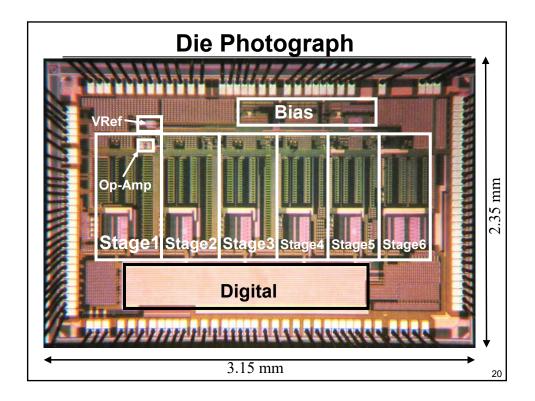

| Technology                      | 90 nm CMOS           |         |                    |                             |         |                 |  |

| Package                         | 56 pin QFN           |         |                    |                             |         |                 |  |

| Die Size Including Pads and     | 2.15 mm × 3.35 mm    |         |                    |                             |         |                 |  |

| Active Area                     | $4 \text{ mm}^2$     |         |                    |                             |         |                 |  |

| Digital Calibration             | on-chip              |         |                    |                             |         |                 |  |

| Voltage References              | on-chip              |         |                    |                             |         |                 |  |

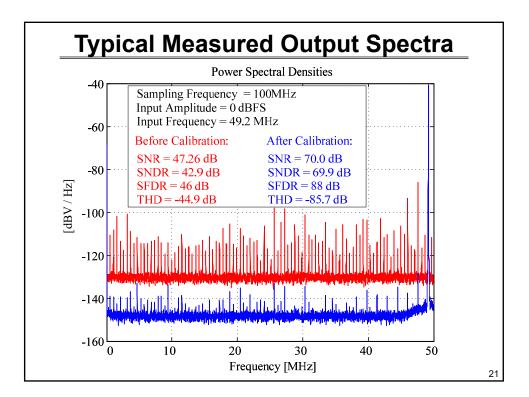

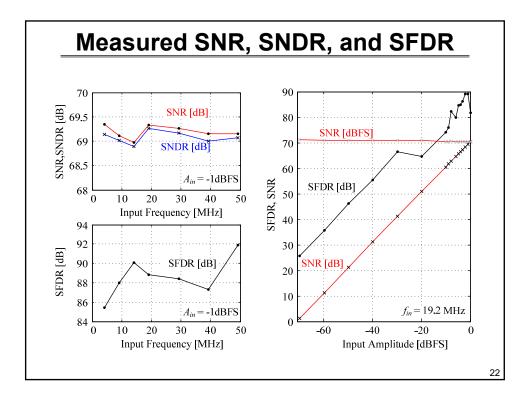

| Worst Case Measured Resu        | lts Over N           | Nyquist | Band for $f_s = 1$ | 100 MHz                     |         |                 |  |

| Derror Crownline                | V                    | DD Test | Case 1             | V <sub>DD</sub> Test Case 2 |         |                 |  |

| Power Supplies                  | V <sub>DD</sub> Powe |         | r Dissipation      | $V_{DD}$                    | Power D | wer Dissipation |  |

| Analog                          | 1.2 V                | 93 mV   | V                  | 1.0 V                       | 62 mW   | 92 mW           |  |

| Digital                         | 1.0 V                | 17 mV   | V 130 mW           | 0.7 V                       | 7 mW    |                 |  |

| Clock Generator                 | 1.0 V                | 1 mW    | 150 11 1           | 1.0 V                       | 1 mW    |                 |  |

| Clock Drivers and DEM           | 1.35 V               | 19 mV   | V                  | 1.35 V                      | 22 mW   |                 |  |

| Performance with HDC and DNC On |                      |         |                    |                             |         |                 |  |

| Peak SNR                        |                      | 70 d    | B                  | 68.3 dB                     |         |                 |  |

| SNDR at -1dBFS                  |                      | 68.8    | dB                 | 66.6                        |         |                 |  |

| SFDR at -1dBFS                  |                      | 85 d    | B                  | 75 dB                       |         |                 |  |

| 2-tone SFDR at -1dBFS           |                      | 86 d    | B                  | 80 dB                       |         |                 |  |

| Maximum INL                     |                      | 3.6 L   | SB                 | 3.8 LSB                     |         |                 |  |

| Maximum DNL                     |                      | 0.54 I  | LSB                | 0.39 LSB                    |         |                 |  |

| Reference<br>or Part<br>Number | fs<br>(MS/s) | SNDR<br>(dBFS) | SFDR<br>(dB) | V <sub>DD</sub><br>(V) | P <sub>tot</sub><br>(mW) | <i>FOM</i> 1<br>(pJ/step) | <i>FOM</i> 2<br>(pJ·V/step) |

|--------------------------------|--------------|----------------|--------------|------------------------|--------------------------|---------------------------|-----------------------------|

| [3]                            | 75           | 68             | 76           | 3                      | 314                      | 2.04                      | 6.12                        |

| LTC2259                        | 80           | 73             | 90           | 1.8                    | 93                       | 0.32                      | 0.57                        |

| AD9233                         | 80           | 70.5           | 90           | 1.8                    | 248                      | 1.13                      | 2.03                        |

| ADS6123                        | 80           | 72.3           | 89           | 3.3                    | 318                      | 1.18                      | 3.89                        |

| LTC2260                        | 105          | 73             | 90           | 1.8                    | 112                      | 0.29                      | 0.53                        |

| AD9233                         | 105          | 70.5           | 90           | 1.8                    | 320                      | 1.11                      | 2.00                        |

| ADS6124                        | 105          | 72.3           | 84           | 3.3                    | 374                      | 1.06                      | 3.49                        |

| [6]                            | 250          | 65.9           | 82           | 1.8                    | 150                      | 0.37                      | 0.67                        |

| This work                      | 100          | 69.8           | 85           | 1.2                    | 130                      | 0.52                      | 0.62                        |

| This work                      | 100          | 67.6           | 75           | 1.0                    | 92                       | 0.47                      | 0.47                        |

|                                |              |                |              |                        |                          |                           | $=\frac{SNDR-3}{6.02}$      |

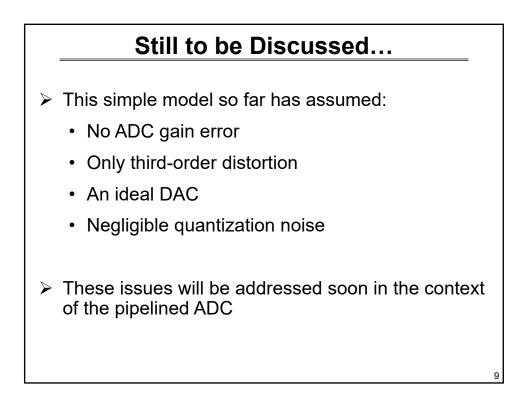

| Design Issues                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------|

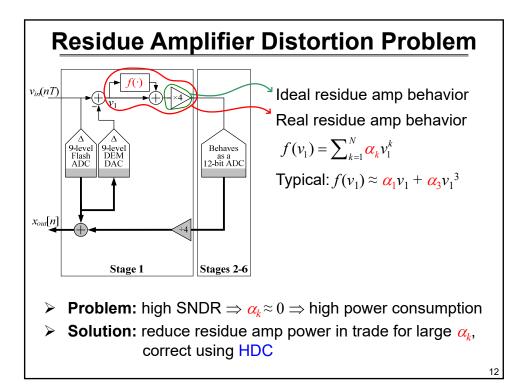

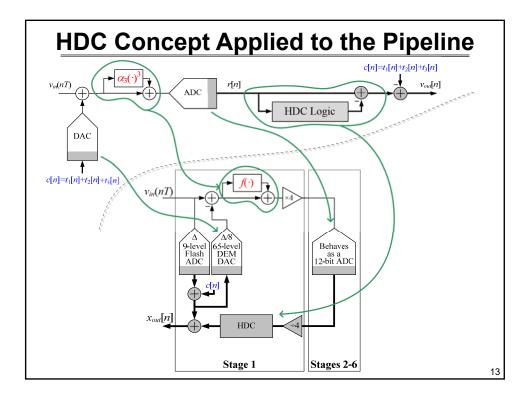

| Limitations of our design                                                                                              |

| <ul> <li>HDC convergence time is 120 seconds</li> </ul>                                                                |

| <ul> <li>Stages 2-6 are not optimized so area and power<br/>are higher than necessary</li> </ul>                       |

| Practical solutions                                                                                                    |

| <ul> <li>HDC auto-calibration phase would reduce<br/>convergence time to &lt; 1 second</li> </ul>                      |

| <ul> <li>Fewer bits per stage after stage 1 and more<br/>aggressive scaling would reduce power and<br/>area</li> </ul> |

| 2                                                                                                                      |