# Peer Reviewed

### Title:

Spurious Tone Mitigation in Fractional-N Phase-Locked Loops

# Author:

Familier, Eythan

Acceptance Date: 2016

#### Series:

UC San Diego Electronic Theses and Dissertations

#### Degree:

Ph.D., Electrical Engineering (Electronic Circuits and Systems)UC San Diego

# Advisor(s):

Galton, Ian A

#### Committee:

Buckwalter, James F, Cauwenberghs, Gert, Hodgkiss, William S, Milstein, Laurence B

### Permalink:

http://escholarship.org/uc/item/8kk1812j

# Abstract:

# **Copyright Information:**

All rights reserved unless otherwise indicated. Contact the author or original publisher for any necessary permissions. eScholarship is not the copyright owner for deposited works. Learn more at <a href="http://www.escholarship.org/help\_copyright.html#reuse">http://www.escholarship.org/help\_copyright.html#reuse</a>

eScholarship provides open access, scholarly publishing services to the University of California and delivers a dynamic research platform to scholars worldwide.

### UNIVERSITY OF CALIFORNIA, SAN DIEGO

Spurious Tone Mitigation in Fractional-N Phase-Locked Loops

A dissertation submitted in partial satisfaction of the requirements for the degree

Doctor of Philosophy

in

Electrical Engineering (Electronic Circuits and Systems)

by

Eythan Familier

Committee in charge:

Professor Ian A. Galton, Chair Professor James F. Buckwalter Professor Gert Cauwenberghs Professor William S. Hodgkiss Professor Laurence B. Milstein

2016

Copyright

Eythan Familier, 2016

All rights reserved.

The dissertation of Eythan Familier is approved, and it is acceptable in quality and form for publication on microfilm and electronically:

Chair

University of California, San Diego

2016

# DEDICATION

To my parents.

# TABLE OF CONTENTS

| Signature I                  | Page                                                                                                                 | iii    |

|------------------------------|----------------------------------------------------------------------------------------------------------------------|--------|

| Dedication                   | 1                                                                                                                    | iv     |

| Table of C                   | ontents                                                                                                              | V      |

| List of Fig                  | ures                                                                                                                 | viii   |

| List of Tab                  | bles                                                                                                                 | xiii   |

| Acknowled                    | dgements                                                                                                             | xiv    |

| Vita                         |                                                                                                                      | xvi    |

| Abstract of the Dissertation |                                                                                                                      | . xvii |

| Chapter 1                    | A Fundamental Limitation Of DC-Free Quantization Noise With Respective To Nonlinearity-Induced Spurious Tones        |        |

|                              | I. Introduction                                                                                                      | 2      |

|                              | II. Spurious Tones in Fractional-N PLLs                                                                              | 5      |

|                              | A. A Tone Definition Based on the Periodogram                                                                        | 5      |

|                              | B. Spurious Tone Generation in Fractional-N PLLs                                                                     | 6      |

|                              | III. Theory of Spurious Tones in DC-Free Quantization Noise                                                          | 9      |

|                              | IV. Alternate Method of Optimal Quantization                                                                         | 18     |

|                              | Appendix                                                                                                             | 21     |

|                              | Acknowledgements                                                                                                     | 23     |

|                              | Figures                                                                                                              | 24     |

|                              | References                                                                                                           | 28     |

| Chapter 2                    | A Class of Quantizers with DC-Free Quantization Noise and Optimal<br>Immunity to Nonlinearity-Induced Spurious Tones | 30     |

|           | I. Introduction                                                                                                                            | 31  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

|           | II. Successive Requantizer Background                                                                                                      | 33  |

|           | A. Spectral Properties of Interest                                                                                                         | 33  |

|           | B. Successive Requantizer Architecture                                                                                                     | 33  |

|           | C. Example Successive Requantizers                                                                                                         | 37  |

|           | D. Additional Successive Requantizer Properties                                                                                            | 38  |

|           | III. Optimal Quantization in Terms of Immunity to Spurious Tones                                                                           | 40  |

|           | A. Theory on Optimal Quantization                                                                                                          | 40  |

|           | B. Optimal Successive Requantizers                                                                                                         | 52  |

|           | Appendix                                                                                                                                   | 55  |

|           | Acknowledgements                                                                                                                           | 66  |

|           | Figures                                                                                                                                    | 67  |

|           | References                                                                                                                                 | 74  |

| Chapter 3 | Second and Third-Order Noise Shaping Digital Quantizers for Low Phas<br>Noise and Nonlinearity-Induced Spurious Tones in Fractional-N PLLs |     |

|           | I. Introduction                                                                                                                            | 77  |

|           | II. Second-Order Successive Requantizer Architecture                                                                                       | 79  |

|           | III. Second-Order Successive Requantizers with High Immunity to Spur<br>Tones                                                              |     |

|           | IV. Second-Order Successive Requantizers with Reduced Quantization<br>Noise at Low-Frequencies                                             | 94  |

|           | V. Third-Order Successive Requantizers with Reduced Quantization No at Low Frequencies                                                     |     |

|           | VI. Conclusion                                                                                                                             | 98  |

|           | Appendix                                                                                                                                   | 99  |

|           | Acknowledgements                                                                                                                           | 106 |

|           | Figures                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

|           | References                                                                                                                                     |

| Chapter 4 | A 3.35 GHz Fractional-N PLL Using a New Class of Digital Quantizers and a Linearity-Enhancement Timing Scheme for Spurious Tone Mitigation 119 |

|           | I. Introduction                                                                                                                                |

|           | II. High-Level Architecture and Functionality                                                                                                  |

|           | A. Spurious Tone Generation in Fractional-N PLLs 122                                                                                           |

|           | B. Second and Third-Order Successive Requantizers                                                                                              |

|           | C. Proposed PLL with Linearity-Enhancement Timing Scheme 129                                                                                   |

|           | III. Implementation Details                                                                                                                    |

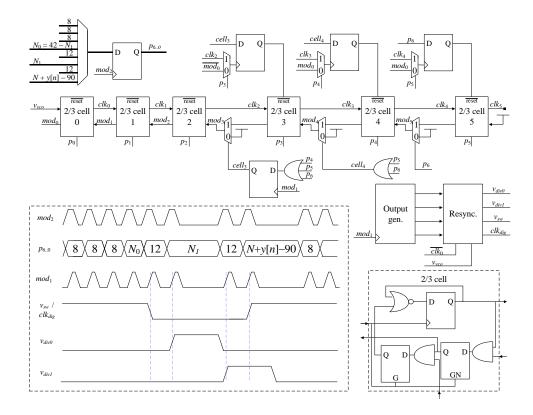

|           | A. Timing                                                                                                                                      |

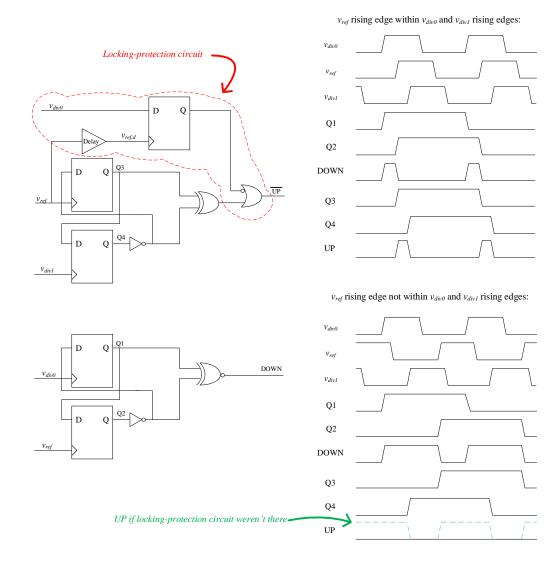

|           | B. PFD                                                                                                                                         |

|           | C. Charge pump and sampled loop filter                                                                                                         |

|           | D. VCO                                                                                                                                         |

|           | E. Digital and SPI                                                                                                                             |

|           | F. Power distribution                                                                                                                          |

|           | IV. Measurement Results                                                                                                                        |

|           | Acknowledgements                                                                                                                               |

|           | Figures                                                                                                                                        |

|           | Tables                                                                                                                                         |

|           | References                                                                                                                                     |

# LIST OF FIGURES

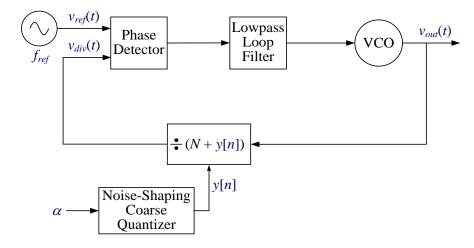

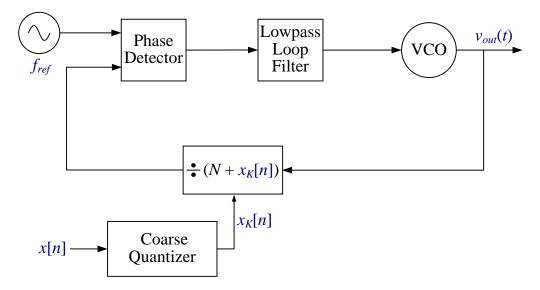

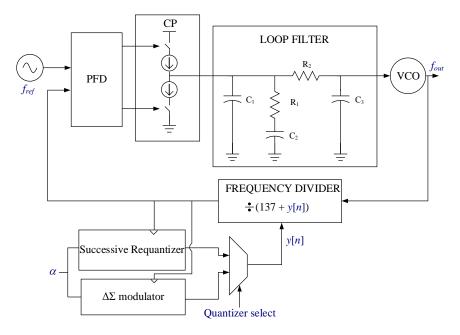

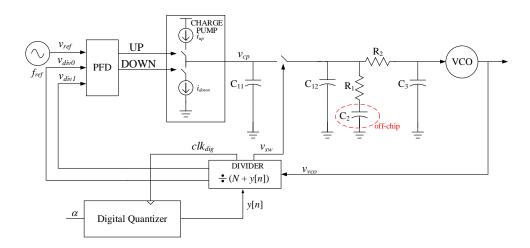

| Figure 1: Block diagram of a fractional- <i>N</i> PLL                                                         |

|---------------------------------------------------------------------------------------------------------------|

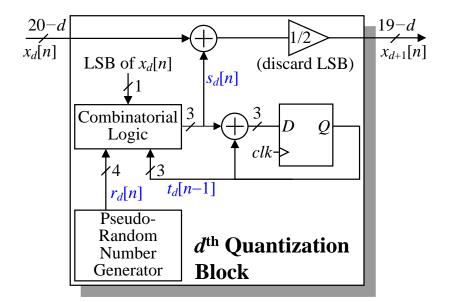

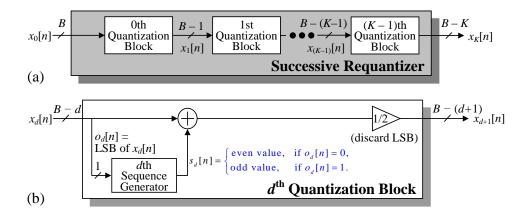

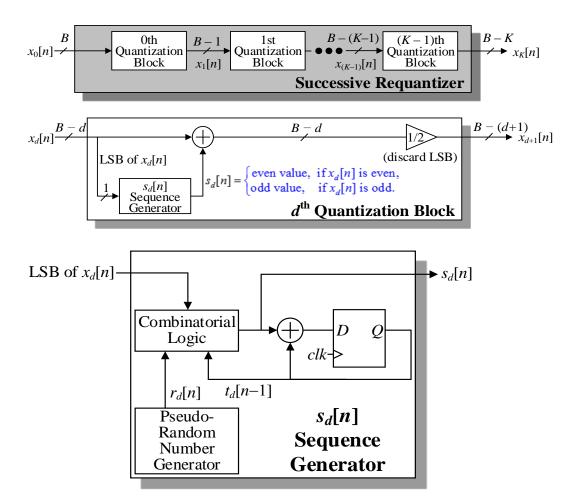

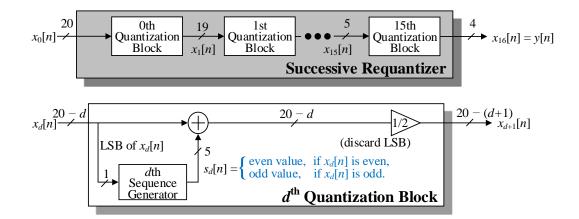

| Figure 2: High-level diagram of an example successive requantizer                                             |

| Figure 3: Details of each quantization block within the example successive                                    |

| requantizer25                                                                                                 |

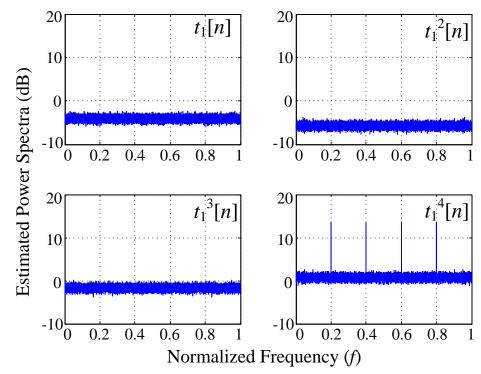

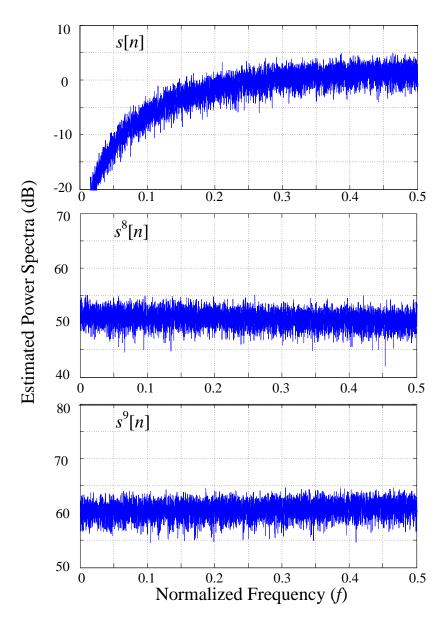

| Figure 4: Estimated power spectra of an optimal quantization noise running sum sequence                       |

| bounded by 2 when raised to different power                                                                   |

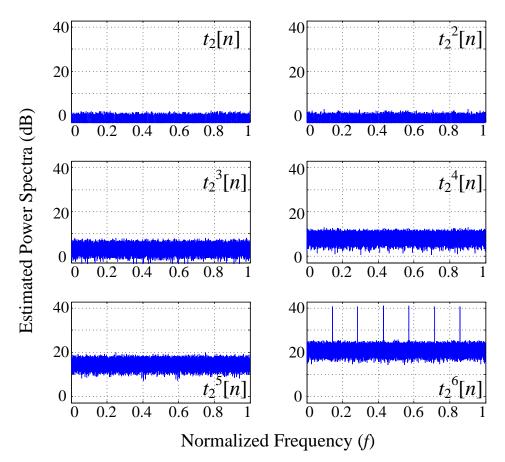

| Figure 5: Estimated power spectra of an optimal quantization noise running sum                                |

| sequence bounded by 3 when raised to different powers                                                         |

| Figure 6: Block diagram of a fractional- <i>N</i> PLL                                                         |

| Figure 7: High-level block diagram of a successive requantizer                                                |

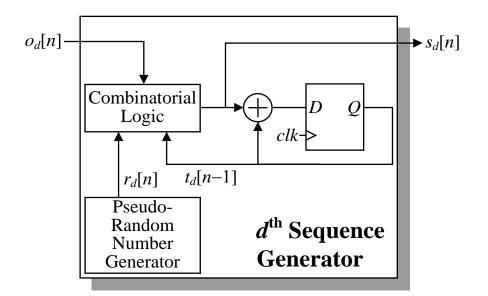

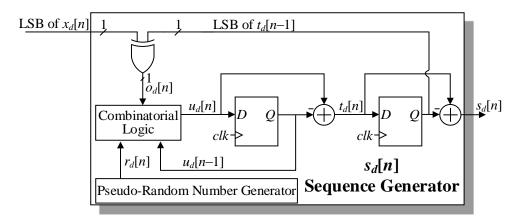

| Figure 8: Block diagram of a sequence generator                                                               |

| Figure 9: Example combinatorial logic truth tables of sequence generators corresponding                       |

| to the one-step state transition matrices in (a) equation (82) and (b) equation                               |

| (83). In both cases, $r_d[n]$ is a sequence of independent and identically                                    |

| distributed random variables which follow a uniform distribution                                              |

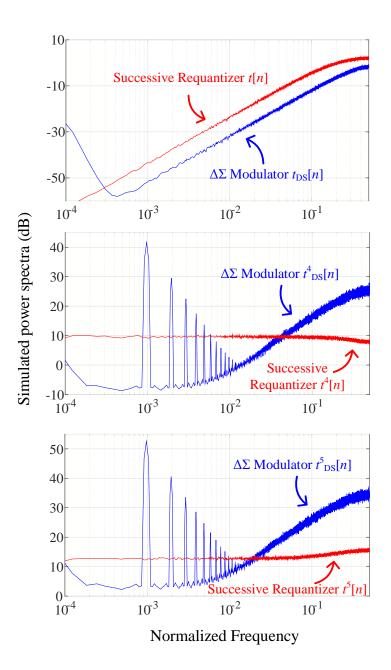

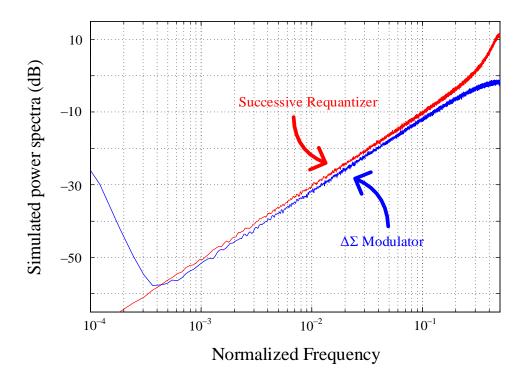

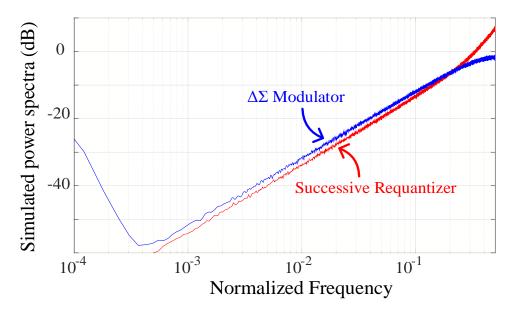

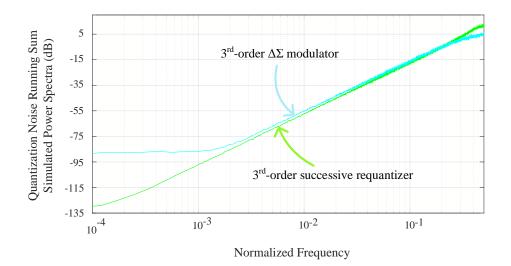

| Figure 10: Estimated power spectra of the quantization noise of a simulated successive                        |

| requantizer for which $N_t = 3$ before and after the application of 8 <sup>th</sup> and 9 <sup>th</sup> order |

| nonlinear distortion70                                                                                        |

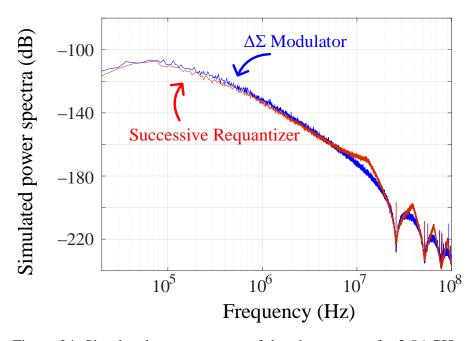

| Figure 11: Estimated power spectra of the running sum of the quantization noise of a                          |

| simulated successive requantizer for which $N_t = 3$ before and after the                                     |

| application of 5 <sup>th</sup> and 6 <sup>th</sup> order nonlinear distortion                                 |

- Figure 14: High-level diagram of a successive requantizer. ..... 107

Figure 21: Block diagram of the PLL used in phase error simulations...... 112

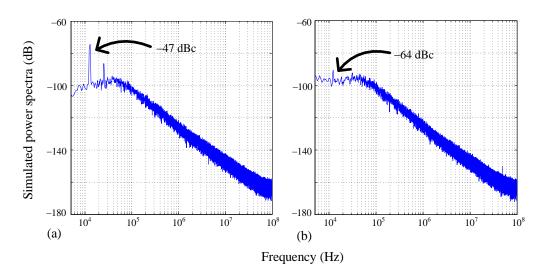

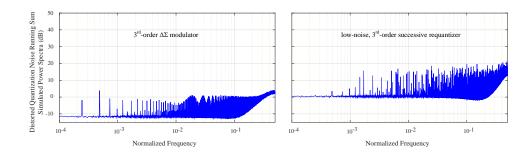

- Figure 27: Simulated power spectra of the phase error of a 3.56 GHz output frequency, 85 kHz bandwidth PLL when its digital quantizer is implemented as a thirdorder  $\Delta\Sigma$  modulator and a third-order successive requantizer that implements the state transition matrices in (232) when (a) there are no circuit noise ... 116

Figure 28: High-level diagram of a typical fractional-*N* PLL......142

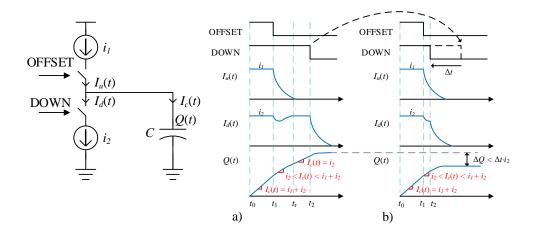

- Figure 38: Charge pump nonlinearity example when using an offset pulse generator. 146

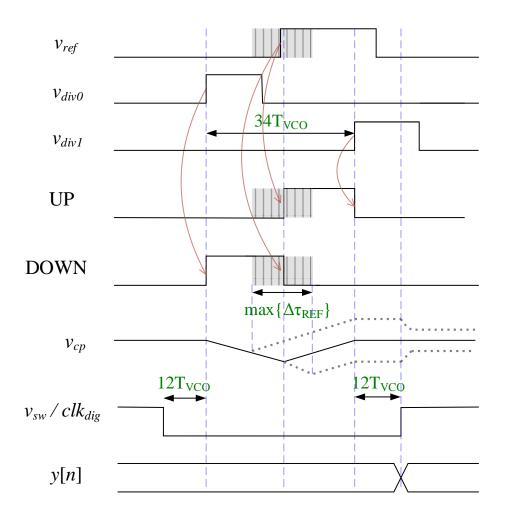

- Figure 40: Timing diagram of the implemented fractional-N PLL. ...... 147

- Figure 42: Block and timing diagrams of the PFD......149

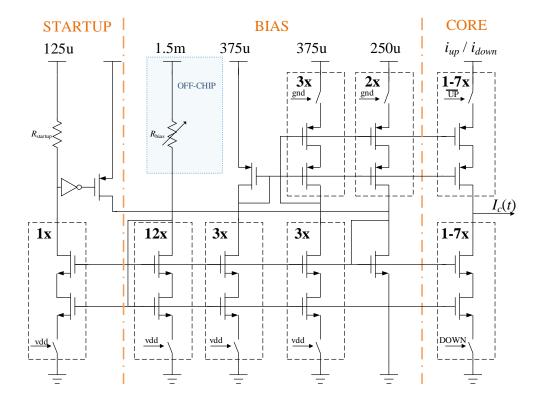

| Figure 43: Implemented charge pump 150                                                |

|---------------------------------------------------------------------------------------|

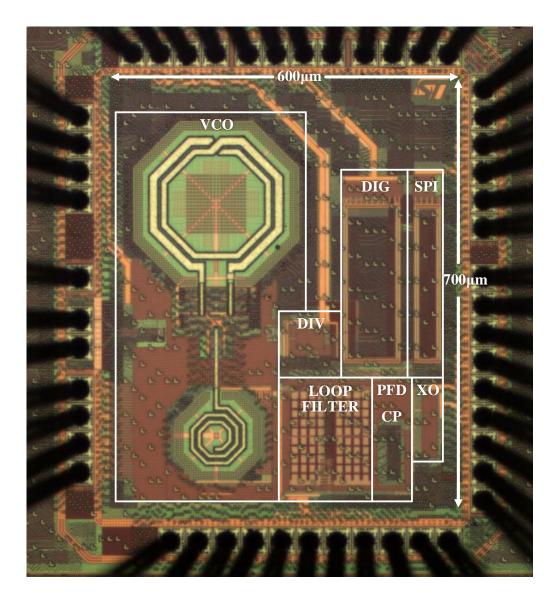

| Figure 44: Die photograph 151                                                         |

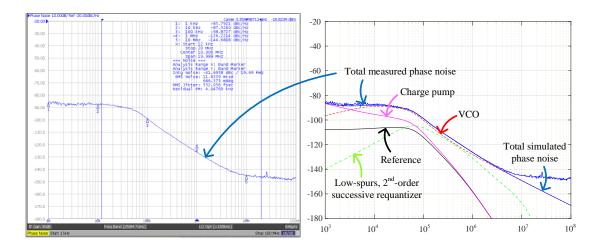

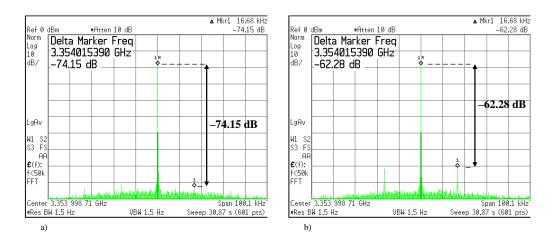

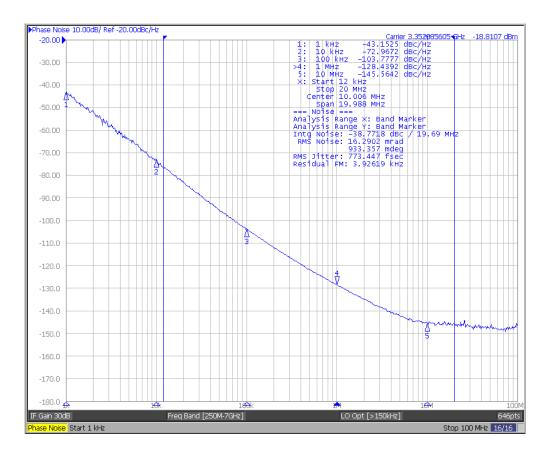

| Figure 45: Measured PLL phase noise for a 3.35 GHz output and 16.68 kHz fractional    |

| frequency when using the low-spurs, second-order successive requantizer, and          |

| estimated phase noise contributions152                                                |

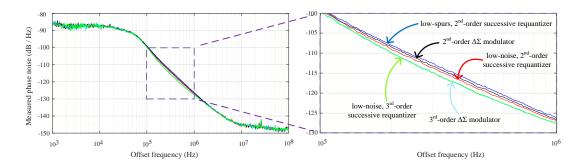

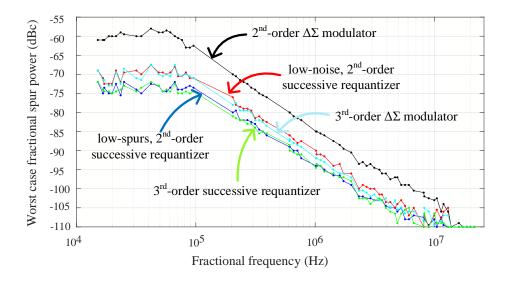

| Figure 46: Comparison of the measured PLL phase noise for a 3.35 GHz output and a     |

| 16.68 kHz fractional frequency between the five digital quantizers 152                |

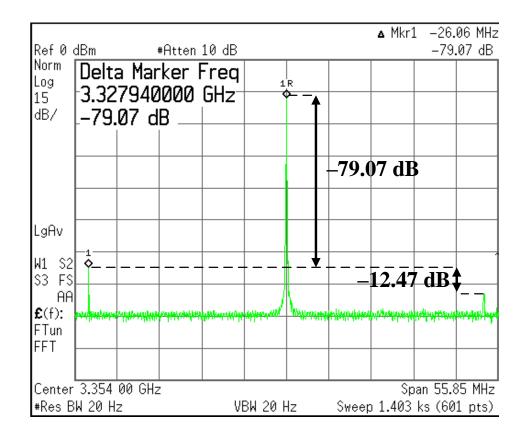

| Figure 47: Measured PLL output spectrum showing the worst fractional spurious tone at |

| 16.68 kHz when using a) the low-spurs, second-order successive requantizer            |

| and b) a second-order $\Delta\Sigma$ modulator                                        |

| Figure 48: The largest measured fractional spurious tone as a function of the PLL     |

| fractional frequency for the five digital quantizers                                  |

| Figure 49: Measured PLL output spectrum showing the reference spur 154                |

| Figure 50: Measured open-loop VCO phase noise 155                                     |

# LIST OF TABLES

| Table 1: Area and power breakdown of the IC.       | . 156 |

|----------------------------------------------------|-------|

| 1                                                  |       |

| Table 2: Performance summary and comparison table. | . 157 |

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Professor Ian Galton, for his invaluable support and advice throughout my time here. His passion for engineering, his relentless search for the truth, and his dedication to his students are admirable, and his role in my development as an engineer cannot be overstated.

I would also like to thank my lab mates, friends, and family for their constant support.

Chapter 1, in full, has been published in the IEEE Transactions on Signal Processing, volume 61, number 16, pages 4172-4180, August 2013. E. Familier, I. Galton, 2013. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

Chapter 2, in full, has been published in the IEEE Transactions on Signal Processing, volume 61, number 17, pages 4270-4283, September 2013. E. Familier, C. Venerus, I. Galton, 2013. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

Chapter 3, in full, has been submitted for publication to the IEEE Transactions on Circuits and Systems I: Regular Papers. E. Familier, I. Galton, 2016. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

Chapter 4, in full, is currently being prepared for submission for publication of the material. E. Familier, I. Galton. The dissertation author is the primary investigator and

author of this material. Professor Ian Galton supervised the research which forms the basis for this material.

#### VITA

....

| 2016 | Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems), University of California, San Diego |

|------|-----------------------------------------------------------------------------------------------------------------------|

| 2012 | Master of Science in Electrical Engineering (Electronic Circuits and Systems), University of California, San Diego    |

| 2010 | Bachelor of Science in Electrical Engineering, California Institute of Technology                                     |

#### PUBLICATIONS

E. Familier, I. Galton, "Second and Third-Order Noise Shaping Digital Quantizers for Low Phase Noise and Nonlinearity-Induced Spurious Tones in Fractional-*N* PLLs," *IEEE Trans. Circuits Syst. I*, accepted for publication.

C. Weltin-Wu, E. Familier, I. Galton, "A Linearized Model for the Design of Fractional-*N* Digital PLLs Based on Dual-Mode Ring Oscillator FDCs," *IEEE Trans. Circuits Syst. I*, vol. 62, no. 8, 2015.

E. Familier, C. Venerus, I. Galton, "A Class of Quantizers with DC-Free Quantization Noise and Optimal Immunity to Nonlinearity-Induced Spurious Tones," *IEEE Trans. Signal Process.*, vol. 61, no. 17, 2013.

E. Familier, I. Galton, "A Fundamental Limitation of DC- Free Quantization Noise with respect to Nonlinearity-Induced Spurious Tones," *IEEE Trans. Signal Process.*, vol. 61, no. 16, 2013.

A. Vakili, E. Familier, B. Hassibi, "On the Eigendistribution of the Steady-State Error Covariance Matrix for the Extended RLS Algorithm", *IEEE ICASSP*, 2009.

#### ABSTRACT OF THE DISSERTATION

Spurious Tone Mitigation in Fractional-N Phase-Locked Loops

by

Eythan Familier

Doctor of Philosophy in Electrical Engineering (Electronic Circuits and Systems)

University of California, San Diego, 2016

Professor Ian A. Galton, Chair

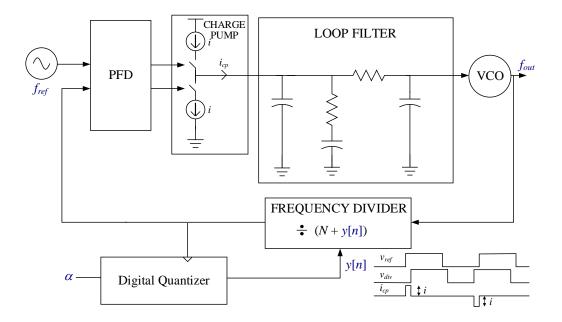

Fractional-*N* phase-locked loops (PLLs) are widely used to synthesize local oscillator signals for modulation and demodulation in communication systems. Their phase error inevitably consists of both a periodic component made up of spurious tones and a random component called phase noise. Spurious tones are particularly harmful to the performance of typical communication systems, so most communication standards stipulate stringent limits on their maximum power in relevant frequency bands.

High-performance PLLs generally contain noise-shaping coarse quantizers to control their output frequency. Such quantizers are a fundamental source of spurious tones in the PLL's phase error. This is because spurious tones are inevitably induced when the quantizer's quantization noise is subjected to nonlinear distortion from analog circuit imperfections. This dissertation presents a rigorous analysis of this effect and a way to mitigate it through the use of a class of digital quantizers with first and higher-order highpass shaped quantization noise which are optimized for spurious tone and phase noise mitigation.

The first chapter of this dissertation presents a mathematical analysis of spurious tone generation via nonlinear distortion of quantization noise. It proves that subjecting the quantization noise running sum of a digital quantizer to a nonlinearity of a certain order will inevitably induce spurious tones, and shows the relation between such nonlinearity order and the range of values the quantization noise running sum takes. The results are general and apply to any digital quantizer.

The second chapter of this dissertation presents a class of digital quantizers with optimal immunity to nonlinearity-induced spurious tones and with first-order highpass shaped quantization noise. It presents design solutions for digital quantizers with quantization noise that can be subjected to nonlinear distortion of a given order without inducing spurious tones, and relies on the results from the first chapter to prove that the presented solutions are optimal in terms of spurious tone generation.

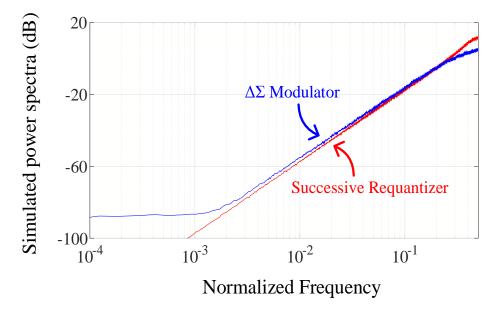

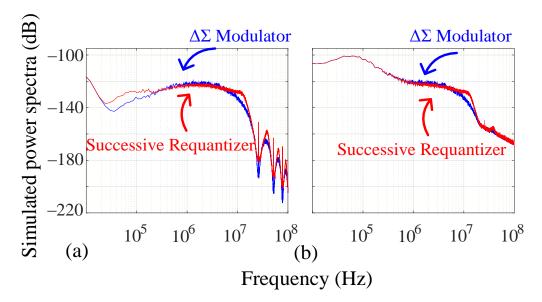

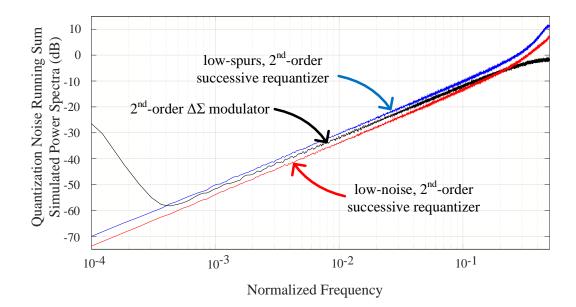

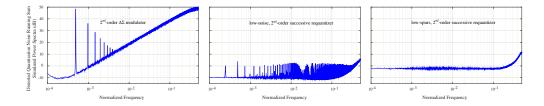

The third chapter of this dissertation presents digital quantizers with second and third-order highpass shaped quantization noise which can be optimized for either spurious tone or phase noise mitigation. These quantizers can replace the often-used delta-sigma modulators in high-performance PLLs to either improve spurious-tone performance at the expense of slightly higher PLL phase noise or lower PLL phase noise.

The fourth chapter of this dissertation present an integrated circuit PLL which implements the second and third-order digital quantizers presented in the third chapter. It demonstrates record-setting spurious tone performance due to the use of these digital quantizers and to a new linearity-enhancement PLL timing scheme.

#### **CHAPTER 1**

# A FUNDAMENTAL LIMITATION OF DC-FREE QUANTIZATION NOISE WITH RESPECT TO NONLINEARITY-INDUCED SPURIOUS TONES

**Abstract**—Fractional-*N* phase-locked loops (PLLs) are widely used to synthesize local oscillator signals for modulation and demodulation in communication systems. Such PLLs generate and subsequently lowpass filter DC-free quantization noise as part of their normal operation. Unfortunately, the quantization noise and its running sum inevitably are subjected to nonlinear distortion from analog circuit imperfections which causes spurious tones in the PLL output signal that can degrade communication system performance. This paper presents the first general mathematical analysis of this phenomenon. It proves that if the running sum of the quantization noise, t[n], satisfies  $t_{low} < t[n] \le t_{high}$  for all *n*, where  $t_{low}$  and  $t_{high} = t_{low}$  will result in spurious tones for most fractional-*N* PLL output frequencies regardless of how the quantization is performed. It also shows that quantizers exist which are optimal in the sense that subjecting the running

Manuscript received January 25, 2013; revised April 26, 2013; accepted May 07, 2013. Date of publication May 16, 2013; date of current version July 22, 2013. The associate editor coordinating the review of this manuscript and approving it for publication was Prof. Ljubisa Stankovic. This work was supported by the National Science Foundation under Award 0914748.

The authors are with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093-0407 USA (e-mail: galton@ucsd.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/TSP.2013.2263504

sum of their quantization noise to kth-order distortion for any  $k \in \{1, 2, 3, ..., t_{high} - t_{low} - 1\}$  does not result in any spurious tones. In a typical fractional-*N* PLL, the larger the range of t[n] the greater the power of the PLL's phase noise, so these results imply a fundamental tradeoff between phase noise power and spurious tones in PLLs.

#### I. INTRODUCTION

Fractional-*N* phase-locked loops (PLLs) are widely used to synthesize local oscillator signals for modulation and demodulation in communication systems, as they can provide fine frequency tuning resolution with relatively low power consumption and integrated circuit area [1], [2]. Ideally, a fractional-*N* PLL's output signal is perfectly periodic, so its phase increases linearly with time. Unfortunately, non-ideal circuit behavior causes the actual phase of the output signal to deviate from its ideal phase, where the deviation is referred to as *phase noise*. The phase noise inevitably consists of both periodic components called spurious tones and random components. Spurious tones are particularly harmful to the performance of typical communication systems, so most communication standards directly or indirectly stipulate stringent limits on the maximum power of the spurious tones in addition to specifying the maximum tolerable power of the overall phase noise in relevant frequency bands [3].

Fractional-*N* PLLs generally contain noise-shaping coarse quantizers, most commonly implemented as digital delta-sigma ( $\Delta\Sigma$ ) modulators, which have recently been shown to be a significant, albeit indirect, source of phase noise spurious tones [4]–

[10]. The output frequency of a fractional-*N* PLL is controlled by a digital codeword that represents a rational number,  $\alpha$ , between 0 and 1. The coarse quantizer operates on  $\alpha$  and generates a digital sequence that can be viewed as the sum of  $\alpha$  and DC-free *quantization noise* [11]–[13]<sup>2</sup>. The quantization noise is converted into analog form, integrated, and lowpass filtered within the PLL, and the resulting waveform directly adds to the PLL phase noise [1]. Unfortunately, the quantization noise and its running sum are subjected to nonlinear distortion from inevitable analog circuit imperfections, and this can induce spurious tones even when the quantization noise itself is free of spurious tones.

This problem is mitigated in the fractional-*N* PLL presented in [7] wherein the *successive requantizer* proposed in [6] is used in place of a  $\Delta\Sigma$  modulator. The successive requantizer offers the advantage that its quantization noise and the running sum of its quantization noise remain free of spurious tones even when subjected to the type of nonlinear distortion commonly imposed by non-ideal circuit behavior in PLLs. This enables the PLL presented in [7] to achieve state-of-the-art spurious tone performance, but a price is paid for this benefit. In return for the enhanced immunity to nonlinearity-induced spurious tones, the power of the quantization noise introduced by the successive requantizer is significantly higher than that of a comparable  $\Delta\Sigma$  modulator. The PLL presented in [7] employs a technique known as phase noise cancellation to overcome this problem at the expense of additional power consumption and circuit area.

No previous publications have addressed the question of whether the tradeoff between immunity to nonlinearity-induced spurious tones and increased quantization

$<sup>^2</sup>$  A sequence whose running sum is bounded for all time is said to be DC-free.

noise power observed in the successive requantizer is inevitable. This is an important question because if the tradeoff were just an idiosyncrasy of the successive requantizer, it might be possible to design an improved coarse quantizer with good immunity to spurious tones that is not subject to the tradeoff. This paper answers this question.

The results of the paper prove that spurious tones are inevitably generated for most values of  $\alpha$  when the running sum of DC-free quantization noise from a quantizer operating on  $\alpha$  is subjected to the type of nonlinear distortion typically imposed by fractional-*N* PLLs. Specifically, if the running sum of the quantization noise, t[n], satisfies  $t_{low} < t[n] \le t_{high}$  for all *n*, where  $t_{low}$  and  $t_{high}$  are integers, then subjecting t[n] to *k*th-order distortion for at least one *k* in the set {1, 2, 3, ...,  $t_{high}-t_{low}$ } will result in spurious tones for most values of  $\alpha$  regardless of how the quantization is performed. The paper also shows that quantizers exist which are optimal in the sense that subjecting the running sum of their quantization noise to *k*th-order distortion for any value of *k* in the set {1, 2, 3, ...,  $t_{high}-t_{low}-1$ } does not result in any spurious tones. Therefore, the results imply a fundamental tradeoff between phase noise power and spurious tone suppression in a PLL.

The remainder of the paper consists of three main sections. Section II describes the details of the spurious tone problem in fractional-*N* PLLs, Section III presents and proves the theoretical results outlined above, and Section IV presents a method of quantization that is optimal in the sense described above.

#### II. SPURIOUS TONES IN FRACTIONAL-N PLLS

#### A. A Tone Definition Based on the Periodogram

Consider a discrete-time complex-coefficient image-rejection bandpass filter with a positive-frequency passband centered at any non-zero frequency  $\omega_p$  and an adjustable equivalent noise bandwidth,  $\Delta \omega_p$ , wherein the passband's peak power gain times  $\Delta \omega_p$  is unity. A sequence applied to the filter is said to contain a tone at  $\omega_p$  if the squared magnitude of the output of the filter grows without bound as  $\Delta \omega_p$  is reduced to zero. This description of a tone is consistent with the way that tones are measured in the laboratory using a spectrum analyzer [14].

An example of such a bandpass filter has a length-*L* impulse response given by

$$h_{L}[n] = \begin{cases} \frac{1}{\sqrt{L}} e^{-j\omega_{p}(L-1-n)} & \text{if } 0 \le n \le L-1, \\ 0, & \text{otherwise,} \end{cases}$$

(1)

where  $\Delta \omega_p$  goes to zero as *L* goes to infinity. If the filter is applied to a sequence, *x*[*n*], the squared magnitude of the filter output at time index n = L - 1 can be written as

$$I_{x,L}(\omega_p) = \frac{1}{L} \left| \sum_{k=0}^{L-1} x[k] e^{-j\omega_p k} \right|^2.$$

(2)

The expression given by (2) for any positive integer L and any  $0 \le |\omega_p| \le \pi$  is known as the periodogram [15]. Therefore, the periodogram performs a function analogous to that of a laboratory spectrum analyzer, where increasing L in the periodogram is akin to decreasing the resolution bandwidth of the spectrum analyzer.

Accordingly, a mathematical definition of a tone that reflects the way that tones are measured in the laboratory is as follows.

Definition: Given any  $\omega_p \neq 0$ , x[n] contains a tone at  $\omega_p$  if  $I_{x,L}(\omega_p)$  is unbounded as  $L \rightarrow \infty$ .

The definition implies that a sequence x[n] is free of tones if and only if  $I_{x,L}(\omega)$  is bounded in *L* for all  $0 < |\omega| \le \pi_{\pm}^{3}$

#### B. Spurious Tone Generation in Fractional-NPLLs

Ideally, a fractional-*N* PLL generates a periodic output signal  $v_{out}(t)$  with frequency  $f_{PLL} = f_{ref}(N + \alpha)$ , where  $f_{ref}$  is the frequency of a reference oscillator, *N* is an integer, and  $0 \le \alpha < 1$ . In practice, however, the output signal is more accurately modeled by

$$v_{out}(t) = g(2\pi f_{PLL}t + \theta_{PLL}(t)), \tag{3}$$

where g is a  $2\pi$ -periodic function and  $\theta_{PLL}(t)$  is the phase noise of the PLL [16].

As shown in Fig. 1, a typical fractional-*N* PLL consists of a phase detector, a lowpass loop filter, a voltage controlled oscillator (VCO), a frequency divider, and a noise-shaping coarse quantizer that introduces DC-free quantization noise. The phase detector drives the loop filter with a signal that represents the phase difference between the reference oscillator and frequency divider outputs. The instantaneous frequency of the VCO output signal deviates from its center frequency by an amount proportional to

<sup>&</sup>lt;sup>3</sup> An alternative definition of a tone could be constructed based on traditional power spectral density (PSD) functions. However, the periodogram-based definition is preferred in this work for two reasons. First, the periodogram can be computed for any signal, whereas the PSD is only defined for a relatively small class of signals. Second, the phase noise performance of PLLs is usually quantified by time averages using laboratory equipment such as spectrum analyzers, not by ensemble averages. In this sense, the periodogram provides a meaningful representation of the power spectrum as used in practice.

the output of the loop filter at each point in time. The frequency divider output is a twolevel signal in which the  $n^{th}$  and  $(n+1)^{th}$  rising edges are separated by N + y[n] cycles of the VCO output, where y[n] for each n is an integer generated by the coarse quantizer. The PLL feedback loop adjusts the output frequency so as to zero the DC component of the phase detector output, causing the output frequency to settle to  $f_{ref}$  times the average of N + y[n]. If y[n] could be set to  $\alpha$  for all n, the PLL would have the desired output frequency. However, practical frequency dividers can only count integer numbers of VCO cycles, so y[n] must be integer-valued. Therefore, the coarse quantizer ensures that y[n] is integer-valued but averages to  $\alpha$  in time. This results in the desired PLL output frequency, but the deviations of y[n] from  $\alpha$  contribute an extra component to the PLL's phase noise.

In general, y[n] can be viewed as a representation of  $\alpha$  quantized to be integer valued, and thus can be written as  $y[n] = \alpha + s[n]$ , where s[n] is the quantization noise of y[n]. As explained in the introduction, it is desirable to engineer both s[n] and its running sum t[n], defined by

$$t[n] = \sum_{k=0}^{n} s[k],$$

(4)

to be free of spurious tones and also such that sequences resulting from nonlinearly distorting s[n] and t[n] are free of spurious tones. In practice, it is most critical for t[n] to have these properties, because spurious tones generated by nonlinearly distorting s[n] usually can be sufficiently mitigated by well-known frequency divider linearization techniques such as periodically resynchronizing each frequency divider output rising edge to the next rising edge of the VCO output signal [17].

As described in the introduction, it is usually highly undesirable for the phase noise of a PLL to contain tones, so any tones in a PLL's phase noise are usually referred to as *spurious tones*. Given that this paper describes a spurious tone generation mechanism in PLLs, all tones in the following will be denoted as spurious tones. Nevertheless, from a mathematical point of view there is no distinction between tones and spurious tones.

A sequence x[n] is said to be *immune to spurious tones up to order h* if  $x^p[n]$  is free of tones for all positive integers  $p \le h$ . Based on simulation and experimental results, the nonlinearities to which t[n] is subjected in a PLL tend to be well-modeled as truncated memoryless power series, i.e. functions of the form

$$f(t[n]) = a_0 + a_1 t[n] + a_2 t^2[n] + \dots + a_k t^k[n]$$

(5)

for some positive integer k [6], [7], [18]. Thus, mitigating spurious tone generation in a PLL can be achieved by ensuring that t[n] is immune to spurious tones up to a certain order. As explained in the introduction, s[n] is required to be DC-free, which means that t[n] is bounded, so

$$t_{low} < t[n] \le t_{high} \tag{6}$$

for all *n*, where  $t_{low}$  and  $t_{high}$  are integers. Larger values of  $t_{high} - t_{low}$  offer more flexibility in the design of the coarse quantizer, which can be exploited to increase the order of the spurious tone immunity of t[n]. The results presented in Section III show that the maximum attainable order of spurious tone immunity t[n] can achieve is bounded by ( $t_{high}$  $- t_{low} - 1$ ) regardless of how the quantization is performed.

# III. THEORY OF SPURIOUS TONES IN DC-FREE QUANTIZATION NOISE

The following theorem shows that it is not possible to quantize most values of  $\alpha$  such that the quantization noise is DC-free and its running sum is immune to spurious tones up to order  $t_{high} - t_{low}$ . The result is general in that it holds regardless of how the quantization is performed.

**Theorem:** Let  $\alpha$  be a constant that satisfies  $0 < \alpha < 1$ , let s[n] be a sequence such that

$$y[n] = \alpha + s[n] \tag{7}$$

is integer-valued for all *n*, and let

$$t[n] = \sum_{k=0}^{n} s[k].$$

(8)

If

$$t_{low} < t[n] \le t_{high} \tag{9}$$

for all n, where  $t_{low}$  and  $t_{high}$  are integers, and

$$\alpha = \frac{P}{Q},\tag{10}$$

where *P* and *Q* are relatively prime integers with  $Q > t_{high} - t_{low}$ , then

$$I_{t^{p},L}(2\pi f) = \frac{1}{L} \left| \sum_{n=0}^{L-1} t^{p} \left[ n \right] e^{-j2\pi f n} \right|^{2}$$

(11)

is unbounded in *L* for at least one  $p \in \{1, 2, ..., t_{high} - t_{low}\}$  and at least one  $f \in \{\alpha, 2\alpha, ..., (Q-1)\alpha\}$ .

A practical implication of the theorem is that trying to develop a coarse quantizer applicable to fractional-*N* PLLs that eliminates the spurious tone generation mechanism

described in Section II-B is futile. The coarse quantizer in any fractional-N PLL consists entirely of digital logic and its variables are represented by finite-width data buses, so all variables associated with the coarse quantizer, including  $\alpha$ , are rational numbers. In particular, this implies that  $\alpha$  satisfies (10). Furthermore, the coarse quantizer in a fractional-N PLL is required to have DC-free quantization noise. Thus, any coarse quantizer applicable to a fractional-N PLL must satisfy the theorem's hypothesis. The theorem places no other restrictions on the quantizer; the quantization noise can be deterministic or probabilistic and the theorem does not make any assumptions whatsoever about the quantizer's structure.

Another practical implication of the theorem is that the order of immunity to nonlinearity-induced spurious tones of t[n] from the coarse quantizer in a fractional-*N* PLL can only be increased at the expense of increasing the range of values spanned by t[n]. The sequence t[n] can be viewed as a lowpass filtered version of the quantization noise, so increasing its range tends to increase the power of the quantization noise at low frequencies where the PLL's loop filter provides little or no attenuation. The portion of t[n] within a fractional-*N* PLL's bandwidth is an additive component of the PLL's phase noise, so all other things being the same, increasing the range of t[n] increases power of the PLL's phase noise [1]. Furthermore, most integrated circuit based fractional-*N* PLLs use a phase-frequency detector and charge pump to implement the phase detector in Fig. 1, so the larger the magnitude of t[n] at any time index *n*, the longer the current sources in the charge pump are turned on during the *n*th reference period. Increasing the on-time of the current sources causes more of the current source noise to be converted to phase

noise, so all other things being the same, increasing the range of t[n] also increases the power of the phase noise component contributed by the charge pump.

#### **Proof of the Theorem:**

Equations (7) and (8) imply that

$$t[n] = \sum_{k=0}^{n} y[k] - (n+1)\alpha,$$

(12)

which can be written as

$$t[n] = \sum_{k=0}^{n} y[k] - \lfloor (n+1)\alpha \rfloor - \langle (n+1)\alpha \rangle, \qquad (13)$$

where  $\lfloor x \rfloor$  denotes the largest integer less than or equal to x and  $\langle x \rangle$  denotes the fractional part of x, i.e.  $\langle x \rangle = x - \lfloor x \rfloor$ . Let

$$r[n] = \sum_{k=0}^{n} y[k] - \lfloor (n+1)\alpha \rfloor$$

(14)

with which (13) can be written as

$$t[n] = r[n] - \langle (n+1)\alpha \rangle, \tag{15}$$

By definition, r[n] is an integer-valued sequence.<sup>4</sup> Furthermore,

$$r[n] \in \left\{ t_{low} + 1, t_{low} + 2, \dots, t_{high} \right\}$$

(16)

for all *n*, because t[n] is bounded according to (9) and the last term in (15) is non-negative and less than 1.

Let

$$I_{t^{p},L}(\omega) = \frac{1}{L} \left| \sum_{n=0}^{L-1} t^{p} [n] e^{-j\omega n} \right|^{2}.$$

(17)

Substituting (15) into (17) results in

<sup>&</sup>lt;sup>4</sup> It follows from this and (15) that the fractional part of t[n] is periodic, so it consists entirely of spurious tones. The fractional part operator is a memoryless nonlinearity, so this demonstrates that it is not possible for t[n] to be immune to spurious tones for all memoryless nonlinearities.

$$I_{t^{p},L}(\omega) = \frac{1}{L} \left| \sum_{n=0}^{L-1} (r[n] - \langle (n+1)\alpha \rangle)^{p} e^{-j\omega n} \right|^{2}.$$

(18)

Let L = RQ, where R is any positive integer, and  $\omega = 2\pi i/Q$ , where  $i \in \{1, 2, ..., N\}$

Q-1}. Then (18) can be written as

$$I_{t^{p},RQ}\left(\frac{2\pi i}{Q}\right) = \frac{1}{RQ}\left|\sum_{k=0}^{R-1}\sum_{n=0}^{Q-1} \left(r[kQ+n] - \left((kQ+n+1)\alpha\right)\right)^{p} e^{-j\frac{2\pi i}{Q}(kQ+n)}\right|^{2}.$$

(19)

Given that  $\alpha = P/Q$ , where *P* and *Q* are relatively prime integers (so they have no common integer factors other than 1), the smallest value of *n* greater than zero for which  $n\alpha$  is integer-valued is *Q*. Therefore,  $\langle (n+1)\alpha \rangle$  is a periodic sequence with period *Q*, so

$$\langle (kQ+n+1)\alpha \rangle = \langle (n+1)\alpha \rangle$$

(20)

for each integer k. Substituting (20) into (19), interchanging the summations, and rearranging factors gives

$$I_{r^{p},RQ}\left(\frac{2\pi i}{Q}\right) = \frac{R}{Q} \left[\sum_{n=0}^{R-1} \left[\sum_{k=0}^{R-1} \frac{1}{R} \left(r[kQ+n] - \langle (n+1)\alpha \rangle\right)^{p}\right] e^{-j\frac{2\pi i}{Q}n}\right]^{2}.$$

(21)

Given that r[kQ + n] is integer-valued and bounded according to (16), this can be

rewritten as

$$I_{t^{p},RQ}\left(\frac{2\pi i}{Q}\right)$$

$$= \frac{R}{Q} \left| \sum_{n=0}^{Q-1} \left[ \sum_{m=t_{low}+1}^{t_{high}} P_{R}\left[m,n\right] \left(m - \langle (n+1)\alpha \rangle \right)^{p} \right] e^{-j\frac{2\pi i}{Q}n} \right|^{2},$$

(22)

where

$$P_{R}[m,n] = \frac{1}{R} \sum_{k=0}^{R-1} \gamma[k,m,n], \qquad (23)$$

and

$$\gamma[k,m,n] = \begin{cases} 1, & \text{if } r[kQ+n] = m, \\ 0, & \text{otherwise.} \end{cases}$$

(24)

The summation in (23) counts the number of times that r[kQ + n] = m over the *R* consecutive values of *k* from 0 to R - 1. It follows that  $P_R[m, n]$  has the same properties as a probability distribution in *m* for each *n* and each *R*, i.e.,

$$0 \le P_R[m,n] \le 1 \tag{25}$$

and

$$\sum_{m=t_{low}+1}^{t_{high}} P_R[m,n] = 1.$$

(26)

Equation (22) can be rewritten as

$$I_{t^{p},RQ}\left(\frac{2\pi i}{Q}\right) = \frac{R}{Q} \left| \sum_{n=0}^{Q-1} \beta_{R}^{(p)}[n] e^{-j\frac{2\pi i}{Q}n} \right|^{2}, \qquad (27)$$

where

$$\beta_{R}^{(p)}[n] = \sum_{m=t_{low}+1}^{t_{high}} P_{R}[m,n] (m - \langle (n+1)\alpha \rangle)^{p}.$$

(28)

Thus, the right side of (27) is R/Q times the squared magnitude of the discrete Fourier transform (DFT) of  $\beta_R^{(p)}[n]$ . A necessary condition for the DFT of  $\beta_R^{(p)}[n]$ , i.e.,

$$\sum_{n=0}^{Q-1} \beta_R^{(p)}[n] e^{-j\frac{2\pi i}{Q}n},$$

(29)

to converge to 0 for every i = 1, 2, ..., Q - 1 as *R* goes to infinity, and, therefore, for *R*/Q times the DFT of  $\beta_R^{(p)}[n]$  to be bounded in *R* for every i = 1, 2, ..., Q - 1, is

$$\beta_{R}^{(p)}[n] \rightarrow b_{p} \quad \text{as} \quad R \rightarrow \infty,$$

(30)

where  $b_p$  does not depend on *n*. Given that L = RQ, it follows that (30) is also a necessary condition for (11) to remain bounded in *L*.

Suppose the theorem is false. Then the above implies that there must exist Q probability distributions in m, P[m, n] for n = 0, 1, 2, ..., Q - 1, each of which must satisfy

$$\sum_{n=t_{low}+1}^{t_{high}} P[m,n] \left( m - \langle (n+1)\alpha \rangle \right)^p = b_p$$

(31)

for  $p = 1, 2, ..., t_{diff}$ , where

$$t_{diff} = t_{high} - t_{low}.$$

(32)

Additionally, given that P[m, n] for n = 0, 1, 2, ..., Q - 1 are probability distributions, (31) must hold for p = 0 and  $b_0 = 1$ . Thus, (31) represents  $Q(t_{diff} + 1)$  equations that must be satisfied by  $t_{diff}Q$  probability values and  $t_{diff}$  values of  $b_p$ . This can be viewed a linear system of  $Q(t_{diff} + 1)$  equations with  $t_{diff}Q + t_{diff}$  unknowns. With  $Q > t_{diff}$ , the system has more equations than unknowns, so if the theorem is false the equations must be linearly dependent.

The equations represented by (31) for each  $n \in \{0, 1, 2, ..., Q-1\}$  and all  $p \in \{0, 1, ..., t_{diff} - 1\}$  can be written as

$$\mathbf{M}(x)\mathbf{p}(x) = \mathbf{b} \tag{33}$$

with values of *x* given by

$$x = \langle (n+1)\alpha \rangle, \tag{34}$$

where

$$\mathbf{M}(x) = \begin{pmatrix} 1 & 1 & \dots & 1 \\ (t_{low} + 1 - x) & (t_{low} + 2 - x) & \dots & (t_{high} - x) \\ (t_{low} + 1 - x)^{2} & (t_{low} + 2 - x)^{2} & \dots & (t_{high} - x)^{2} \\ \dots & \dots & \dots & \dots \\ (t_{low} + 1 - x)^{t_{diff} - 1} & (t_{low} + 2 - x)^{t_{diff} - 1} & \dots & (t_{high} - x)^{t_{diff} - 1} \end{pmatrix},$$

(35)

$$\mathbf{b} = \begin{pmatrix} 1 & b_1 & b_2 & \dots & b_{t_{diff}-1} \end{pmatrix}^T,$$

(36)

and

$$\mathbf{p}(\langle (n+1)\alpha \rangle) = (P[t_{low}+1,n] \quad P[t_{low}+2,n] \quad \cdots \quad P[t_{high},n])^{T}.$$

(37)

Furthermore, the equations represented by (31) for each  $n \in \{0, 1, 2, ..., Q - 1\}$  and  $p = t_{diff}$  can be written as

$$\mathbf{m}_{t_{diff}}\left(x\right)\mathbf{p}\left(x\right) = b_{t_{diff}},$$

(38)

with x given by (34) and

$$\mathbf{m}_{t_{diff}}(x) = \left( \left( t_{low} + 1 - x \right)^{t_{diff}} \quad \left( t_{low} + 2 - x \right)^{t_{diff}} \quad \dots \quad \left( t_{high} - x \right)^{t_{diff}} \right).$$

(39)

It follows from the lemma presented in the Appendix that  $\mathbf{m}_{t_{diff}}(x)$  can be

expressed in terms of  $\mathbf{M}(x)$  as

$$\mathbf{m}_{t_{diff}}\left(x\right) = \mathbf{r}\left(x\right)\mathbf{M}\left(x\right),\tag{40}$$

where the *k*th element of  $\mathbf{r}(x)$  is given by

$$(-1)^{t_{diff}-k} \sum_{1 \le i_1 < i_2 < \dots < i_{t_{diff}-k+1} \le t_{diff}} y_{i_1}(x) y_{i_2}(x) \cdots y_{i_{t_{diff}-k+1}}(x),$$

(41)

with

$$y_{i_q}(x) = (t_{low} + i_q - x).$$

(42)

Therefore, (38) and (40) imply

$$b_{t_{diff}} = \mathbf{r}(x)\mathbf{M}(x)\mathbf{p}(x).$$

(43)

Substituting (33) into this result yields

$$b_{t_{diff}} = \mathbf{r}(x)\mathbf{b}.$$

(44)

If the theorem is false, (44) must hold for all values of x in the set

$$\{\langle \alpha \rangle, \langle 2\alpha \rangle, \dots, \langle Q\alpha \rangle\},\tag{45}$$

with  $Q > t_{diff}$ . The set contains Q distinct values of x because P and Q are relatively prime integers, so (44) must hold for more than  $t_{diff}$  distinct values of x if the theorem is false. It follows from (41) and (42) that the first element of  $\mathbf{r}(x)$  is a polynomial in x of degree  $t_{diff}$ , and each of the other elements of  $\mathbf{r}(x)$  is a polynomial in x of degree less than  $t_{diff}$ . Given that the first element of  $\mathbf{b}$  is non-zero, this implies that

$$\mathbf{r}(x)\mathbf{b} - b_{t_{star}} \tag{46}$$

is a polynomial of degree  $t_{diff}$ . Therefore, (46) has  $t_{diff}$  roots, so there can be at most  $t_{diff}$  distinct values of *x* that satisfy (44). This contradicts the supposition that the theorem is false.

The theorem presented above implies that it is not possible to quantize most values of  $\alpha$  such that the quantization noise is DC-free and its running sum is immune to spurious tones up to order  $t_{high} - t_{low}$ . As explained below, this bound on performance is tight in the sense that quantizers exist with the property that the running sum of their quantization noise is immune to spurious tones up to order  $t_{high} - t_{low} - 1$ . The theorem implies that a quantizer with this property is optimal with respect to spurious tone immunity in the sense that the running sum of its quantization noise has the highest possible order of immunity to spurious tones.

The successive requantizer provides an existence proof that quantizers exist which are optimal with respect to spurious tone immunity. As an example, the successive requantizer proposed in [6] and demonstrated in the fractional-*N* PLL integrated circuit presented in [7] is shown in Figs. 2 and 3. For this particular successive requantizer,  $\alpha$ can be any multiple of 2<sup>-16</sup> that is non-negative and less than 1. As shown in Fig. 2, the successive requantizer multiples  $\alpha$  by 2<sup>16</sup> and processes the integer-valued result via a cascade of 16 *quantization blocks*, each of which simultaneously quantizes by one bit and halves each sample of its input sequence. The implementation details of each quantization block are shown in Fig. 3. As proven in [6], *y*[*n*] is an integer-valued quantized version of  $\alpha$ , its quantization noise is DC-free with  $t_{high} - t_{low} = 4$ , and the running sum of its quantization noise is immune to spurious tones up to order 3.

The results in [6] are extended in [19] to show that for each positive integer  $N_t \ge$ 2 there exist multiple successive requantizers that have  $t_{high} - t_{low} = 2N_t$  and for which the running sum of their quantization noise is immune to spurious tones up to order  $2N_t - 1$ . Therefore, each of these successive requantizers is an optimal quantizer with respect to spurious tone immunity in the sense that the running sum of its quantization noise has the highest possible order of immunity to spurious tones.

While the theorem quantifies the relationship between the value of Q and the possible frequencies of the nonlinearity-induced spurious tones, it does not quantify the power of the nonlinearity-induced spurious tones. This is because the theorem is applicable to any quantizer with DC-free quantization noise, whereas the effect of varying Q on quantizer performance for a particular quantizer depends on the quantizer's design. For example, in most delta-sigma modulators with DC-free quantization noise the nonlinearity-induced spurious tone powers are strongly dependent on Q, whereas for the successive requantizer described above computer simulations suggest that they are nearly independent of Q. Thus, the effect of varying Q on quantizer performance must be evaluated in a quantizer specific fashion.

The successive requantizer is not the only type of quantizer that is optimal with respect to spurious tone immunity. An alternate method of quantization that is optimal with respect to spurious tone immunity is presented in this section. Unlike the successive requantizer, the idea upon which it is based follows directly from the proof of the theorem presented in Section III, so it gives some insight into the connection between the quantization process and the theorem.

Suppose that a quantized sequence with mean  $\alpha = P / Q$ , where *P* and *Q* are relatively prime integers, is to be generated, and that the running sum of the quantization noise is required to satisfy  $-N_t < t[n] \le N_t$  over all *n* for some positive integer  $N_t$ . Thus,  $t_{low} = -N_t$  and  $t_{high} = N_t$ . By the analysis presented in the proof of the theorem up to (31), a necessary condition for t[n] to be immune to spurious tones up to order  $t_{high} - t_{low} - 1 = 2N_t - 1$  is that there exist *Q* probability distributions in *m*, P[m, u], where  $m \in \{-N_t + 1, -N_t + 2, ..., N_t\}$  and  $u \in \{0, 1, 2, ..., Q - 1\}$ , which satisfy (31) for  $p = 1, 2, ..., 2N_t - 1$ . It follows from (31) that these probability distributions must satisfy

$$\sum_{m=-N_{t}+1}^{N_{t}} P[m,i] \left(m - \langle (i+1)\alpha \rangle\right)^{p}$$

$$= \sum_{m=-N_{t}+1}^{N_{t}} P[m,i+1] \left(m - \langle (i+2)\alpha \rangle\right)^{p},$$

(47)

for all  $i \in \{0, 1, 2, ..., Q-2\}$ , and  $p \in \{1, 2, 3, ..., 2N_t - 1\}$ . To be probability distributions, they must also be non-negative and satisfy

$$\sum_{n=-N_t+1}^{N_t} P[m,u] = 1,$$

(48)

for all  $u \in \{0, 1, 2, ..., Q - 1\}$ . Any set of P[m, n] that satisfy (47) and (48), can be used to generate r[n] such that

$$r[n] \in \{-N_t + 1, -N_t + 2, \dots, N_t\}$$

(49)

for all *n* and

$$\lim_{R \to \infty} \frac{1}{R} \sum_{k=0}^{R-1} \gamma[k, m, u] = P[m, u]$$

(50)

where

$$\gamma[k,m,u] = \begin{cases} 1, & \text{if } r[kQ+u] = m, \\ 0, & \text{otherwise.} \end{cases}$$

(51)

This can be done either probabilistically or deterministically. For each n, once r[n] is known the running sum of the quantization noise, the quantization noise, and the quantizer output can be calculated using

$$t[n] = r[n] - \langle (n+1)\alpha \rangle, \qquad (52)$$

$$s[n] = t[n] - t[n-1],$$

(53)

and

$$y[n] = \alpha + s[n], \tag{54}$$

respectively.

For instance, as done in the following examples, r[n] can be generated as a sequence of independent random variables with probability distributions

$$\Pr(r[n] = m) = P[m, n \mod Q]$$

(55)

for all  $m \in \{-N_t + 1, -N_t + 2, ..., N_t\}$  and all integers *n*. It follows from (52) that  $t^p[n]$  is

a sequence of independent random variables, and from (47) that the mean of  $t^{p}[n]$  is

independent of *n* for  $p \in \{1, 2, 3, ..., 2N_t - 1\}$ . It follows that  $t^p[n]$  is white noise and is therefore free of spurious tones for each  $p \in \{1, 2, 3, ..., 2N_t - 1\}$ .

There are many sets of non-negative P[m, u] values that satisfy the system of equations specified by (47) and (48), because the system is under-constrained; it has  $(Q - 1)(2N_t - 1) + Q$  equations and  $2N_tQ$  unknowns. Therefore, additional constraints can be imposed on the P[m, u] values. For example, imposing additional constraints of the form

$$\sum_{m=-N_{t}+1}^{N_{t}} P[m,i] \left(m - \langle (i+1)\alpha \rangle \right)^{2N_{t}}$$

$$= \sum_{m=-N_{t}+1}^{N_{t}} P[m,u] \left(m - \langle (u+1)\alpha \rangle \right)^{2N_{t}}$$

(56)

for as many *i*,  $u \in \{0, 1, 2, ..., Q - 1\}$  as possible has the effect of minimizing spurious tone power in  $t^{2N_t}[n]$ .

Two quantization noise running sum sequences,  $t_1[n]$  and  $t_2[n]$ , based on the method described above are presented below and demonstrated by simulation to have optimal orders of spurious tone immunity. The magnitude bounds on  $t_1[n]$  and  $t_2[n]$  are  $N_{t1} = 2$  and  $N_{t2} = 3$ , respectively, and the quantized sequences corresponding to  $t_1[n]$  and  $t_2[n]$  have means of  $\alpha_1 = 1/5$  and  $\alpha_2 = 1/7$ , respectively. The P[m, u] values found in both cases are presented in matrices  $\mathbf{P}_1$  and  $\mathbf{P}_2$ , defined by

$$\mathbf{P}_{k}(i,j) = P[-N_{tk} + i, j - 1]$$

for  $i \in \{1, 2, ..., 2N_{tk}\}, j \in \{1, 2, ..., Q\}$ , and  $k = 1$  or 2:

$$(57)$$

$$\mathbf{P}_{1} = \begin{pmatrix} \frac{14}{125} & \frac{7}{125} & \frac{3}{125} & \frac{1}{125} & \frac{1}{5} \\ \frac{73}{125} & \frac{64}{125} & \frac{51}{125} & \frac{37}{125} & \frac{3}{5} \\ \frac{37}{125} & \frac{51}{125} & \frac{64}{125} & \frac{73}{125} & \frac{1}{5} \\ \frac{1}{125} & \frac{3}{125} & \frac{7}{125} & \frac{14}{125} & 0 \end{pmatrix},$$

$$\mathbf{P}_{2} = \begin{pmatrix} \frac{132}{16807} & \frac{66}{16807} & \frac{30}{16807} & \frac{12}{16807} & \frac{4}{16807} & \frac{1}{16807} & \frac{5}{343} \\ \frac{137}{780} & \frac{2190}{16807} & \frac{273}{2945} & \frac{97}{1538} & \frac{687}{16807} & \frac{185}{7368} & \frac{78}{343} \\ \frac{236}{465} & \frac{880}{1821} & \frac{272}{611} & \frac{738}{1861} & \frac{2519}{2551} & \frac{236}{343} \\ \frac{724}{2551} & \frac{860}{2519} & \frac{738}{1538} & \frac{272}{16807} & \frac{880}{16807} & \frac{236}{780} & \frac{78}{343} \\ \frac{185}{7368} & \frac{687}{16807} & \frac{97}{1538} & \frac{273}{2945} & \frac{2190}{16807} & \frac{137}{780} & \frac{5}{343} \\ \frac{1}{16807} & \frac{4}{16807} & \frac{12}{16807} & \frac{30}{16807} & \frac{66}{16807} & \frac{132}{16807} & 0 \end{pmatrix}$$

(58)

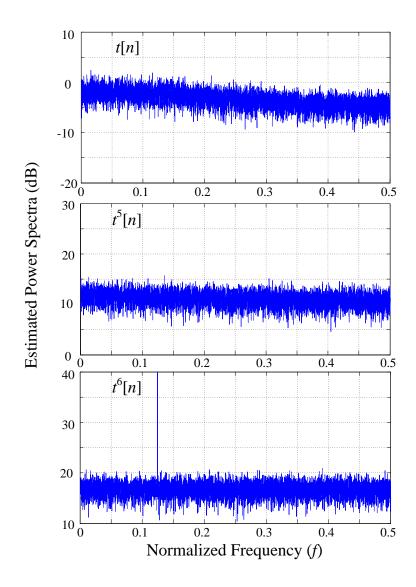

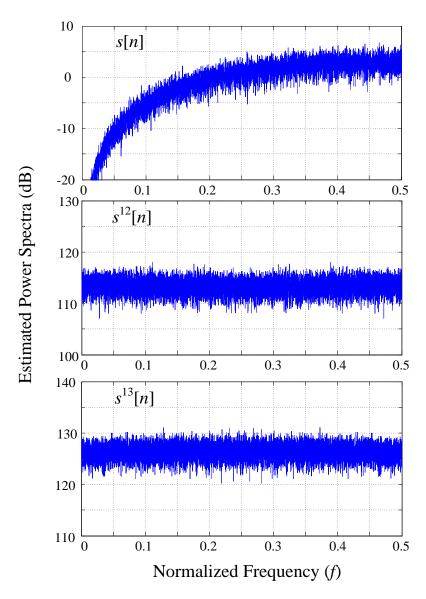

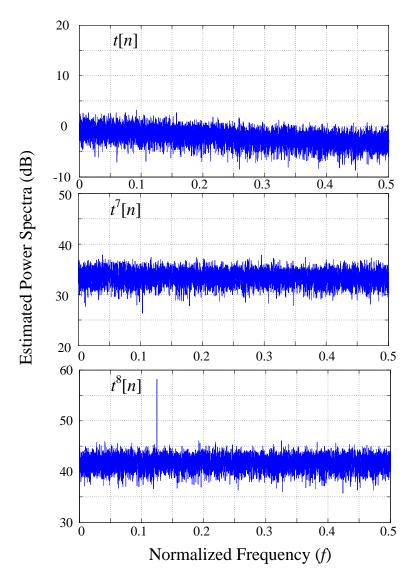

Figs. 4 and 5 show the estimated power spectra of  $t_1^p[n]$  for  $p \in \{1, 2, 3, 4\}$  and

$t_2^{q}[n]$  for  $q \in \{1, 2, ..., 6\}$ . The figures demonstrate that spurious tones in  $t_1^{p}[n]$  are present only when  $p = 2N_{t1} = 4$  and that spurious tones in  $t_2^{q}[n]$  are present only when q $= 2N_{t2} = 6$ . This supports the assertion that both examples represent optimal quantization in terms of spurious tone immunity.

$P_{2} =$

1

16807

16807

#### APPENDIX

The following lemma is used in the proof of the theorem in Section III.

**Lemma:** Given arbitrary  $a_1, a_2, ..., a_n$ , let **V** be the following  $n \ge n$  matrix:

$$\mathbf{V} = \begin{pmatrix} 1 & 1 & 1 & \dots & 1 \\ a_1 & a_2 & a_3 & \dots & a_n \\ a_1^2 & a_2^2 & a_3^2 & \dots & a_n^2 \\ \dots & \dots & \dots & \dots & \dots \\ a_1^{n-1} & a_2^{n-1} & a_3^{n-1} & \dots & a_n^{n-1} \end{pmatrix}.$$

(60)

Then, the row vector

$$\mathbf{v}_{n} = \begin{pmatrix} a_{1}^{n} & a_{2}^{n} & a_{3}^{n} & \dots & a_{n}^{n} \end{pmatrix}$$

(61)

can be expressed as

$$\mathbf{v}_n = \mathbf{r} \cdot \mathbf{V},\tag{62}$$

where  $\mathbf{r}$  is a row vector whose elements are given by

$$\mathbf{r}(1) = (-1)^{n-1} \sum_{1 \le i_1 < i_2 < \dots < i_n \le n} a_{i_1} a_{i_2} \cdots a_{i_n},$$

$$\mathbf{r}(2) = (-1)^{n-2} \sum_{1 \le i_1 < i_2 < \dots < i_{n-1} \le n} a_{i_1} a_{i_2} \cdots a_{i_{n-1}},$$

$$\vdots$$

$$\mathbf{r}(n) = \sum_{1 \le i_1 \le n} a_{i_1}.$$

(63)

**Proof:**

Consider the polynomial

$$P(x) = (x - a_1)(x - a_2) \cdots (x - a_n),$$

(64)

which can be expanded as

$$P(x) = x^{n} - x^{n-1} \sum_{1 \le i_{1} \le n} a_{i_{1}} + x^{n-2} \sum_{1 \le i_{1} < i_{2} \le n} a_{i_{1}} a_{i_{2}} - \dots + (-1)^{n} \sum_{1 \le i_{1} < i_{2} \le \dots < i_{n} \le n} a_{i_{1}} a_{i_{2}} \dots a_{i_{n}}.$$

(65)

It follows from (64) that  $a_k$  is a root of P(x) for any  $k \in \{1, 2, ..., n\}$ , i.e.

$$P(a_k) = 0. \tag{66}$$

Additionally, it is seen from (65) that  $P(a_k)$  can be expressed as

$$P(a_k) = a_k^{\ n} - (\mathbf{r} \cdot \mathbf{V})(k), \tag{67}$$

where  $(\mathbf{r} \cdot \mathbf{V})(k)$  is the *k*th element of the vector  $\mathbf{r} \cdot \mathbf{V}$ . Therefore, (66) and (67) yield

$$(\mathbf{r} \cdot \mathbf{V})(k) = a_k^n, \tag{68}$$

which proves the result.

### ACKNOWLEDGEMENTS

Chapter 1, in full, has been published in the IEEE Transactions on Signal Processing, volume 61, number 16, pages 4172-4180, August 2013. E. Familier, I. Galton, 2013. The dissertation author is the primary investigator and author of this paper. Professor Ian Galton supervised the research which forms the basis for this paper.

Figure 1: Block diagram of a fractional-N PLL.

Figure 2: High-level diagram of an example successive requantizer.

# **Combinatorial Logic Truth Table:**

| LSB of $x_d[n] = 0$ |                              |          | LSB of $x_d[n] = 1$ |                              |          |

|---------------------|------------------------------|----------|---------------------|------------------------------|----------|

| $t_d[n-1]$          | $r_d[n]$                     | $s_d[n]$ | $t_d[n-1]$          | $r_d[n]$                     | $s_d[n]$ |

| 2                   | $\geq 0$ and $\leq 3$        | 0        | 2                   | $\leq -1 \text{ or } \geq 4$ | -1       |

| 2                   | $\leq -1 \text{ or } \geq 4$ | -2       | 2                   | $\geq 0$ and $\leq 3$        | -3       |

| 1                   | $\leq -1 \text{ or } \geq 6$ | 0        | 1                   | $\geq 1$ and $\leq 3$        | 1        |

| 1                   | $\geq 0$ and $\leq 5$        | -2       | 1                   | $\leq -1 \text{ or } \geq 4$ | -1       |

| 0                   | 0 or 1                       | 2        | 1                   | 0                            | -3       |

| 0                   | $\leq -1 \text{ or } \geq 4$ | 0        | 0                   | $\geq 0$                     | 1        |

| 0                   | 2 or 3                       | -2       | 0                   | $\leq -1$                    | -1       |

| -1                  | $\leq -1 \text{ or } \geq 6$ | 0        | -1                  | $\geq 1$ and $\leq 3$        | -1       |

| -1                  | $\geq 0$ and $\leq 5$        | 2        | -1                  | $\leq -1 \text{ or } \geq 4$ | 1        |

| -2                  | $\geq 0$ and $\leq 3$        | 0        | -1                  | 0                            | 3        |

| -2                  | $\leq -1 \text{ or } \geq 4$ | 2        | -2                  | $\leq -1 \text{ or } \geq 4$ | 1        |

|                     | •                            |          | -2                  | $\geq 0$ and $\leq 3$        | 3        |

Figure 3: Details of each quantization block within the example successive requantizer.

Figure 4: Estimated power spectra of an optimal quantization noise running sum sequence bounded by 2 when raised to different powers.

Figure 5: Estimated power spectra of an optimal quantization noise running sum sequence bounded by 3 when raised to different powers.

### REFERENCES

- 1. B. Razavi, Phase-Locking in High-Performance Systems: From Devices to Architectures, Wiley-Interscience, 2003.

- 2. T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, Second Edition, Cambridge University Press, 2003.

- 3. S. Ting, A. H. Sayed, "Digital Suppression of Spurious PLL Tones in A/D Converters," *IEEE Transactions on Signal Processing*, vol. 59, no. 11, pp. 5275-5288, November 2011.

- B. De Muer, M. Steyaert, "A CMOS Monolithic ΔΣ-Controlled Fractional-N Frequency Synthesizer for DCS-1800," *IEEE Journal of Solid-State Circuits*, vol. 37, no. 7, July 2002.

- 5. S. Pamarti, L. Jansson, I. Galton, "A Wideband 2.4GHz ΔΣ Fractional-N PLL with 1 Mb/s In-Loop Modulation," *IEEE Journal of Solid-State Circuits*, vol. 39, no. 1, pp. 49-62, January 2004.

- 6. A. Swaminathan, A. Panigada, E. Masry, I. Galton, "A Digital Requantizer with Shaped Requantization Noise that Remains Well Behaved after Nonlinear Distortion," *IEEE Transactions on Signal Processing*, vol. 55, no. 11, pp. 5382-5394, November 2007.

- K. J. Wang, A. Swaminathan, I. Galton, "Spurious Tone Suppression Techniques Applied to a Wide-Bandwidth 2.4 GHz Fractional-N PLL," *IEEE Journal of Solid-State Circuits*, vol. 43, issue 12, pp. 2787-2797, December 2008.

- H. Jian, Z. Xu, Y. Wu, F. Chang, "A Compact 0.8-6GHz Fractional-N PLL with Binary-Weighted D/A Differentiator and Offset-Frequency Δ–Σ Modulator for Noise and Spurs Cancellation," 2009 Symposium on VLSI Circuits, pp. 186-187, 16-18 June 2009.

- 9. P. Su, S. Pamarti, "Mismatch Shaping Techniques to Linearize Charge Pump Errors in Fractional-N PLLs," *IEEE Transactions on Circuits and Systems–I: Regular Papers*, vol. 57, no. 6, June 2010.

- K. Hosseini, B. Fitzgibbon, M.P. Kennedy, "Observations Concerning the Generation of Spurious Tones in Digital Delta-Sigma Modulators Followed by a Memoryless Nonlinearity," *IEEE Transactions on Circuits and Systems-II: Express Briefs*, vol. 58, no. 11, November 2011.

- 11. B. Miller, B. Conley, "A Multiple Modulator Fractional Divider," Annual IEEE

Symposium on Frequency Control, vol. 44, pp. 559-568, March 1990.

- 12. B. Miller, B. Conley, "A Multiple Modulator Fractional Divider," *IEEE Transactions on Instrumentation and Measurement*, vol. 40, no. 3, pp. 578-583, June 1991.

- 13. T. A. Riley, M. A. Copeland, T. A. Kwasniewski, "Delta-Sigma Modulation in Fractional-N Frequency Synthesis," *IEEE Journal of Solid-State Circuits*, vol. 28, no. 5, pp. 553-559, May 1993.

- 14. Agilent Technologies, Inc, *Agilent Spectrum Analysis Basics*, Application Note 150, August 2006.

- 15. A. V. Oppenheim, R. W. Schafer, J. R. Buck, *Discrete-Time Signal Processing*, Second Edition, Englewood Cliffs, NJ: Prentice-Hall, 1999.

- 16. A. Hajimiri, T. H. Lee, "A General Theory of Phase Noise in Electrical Oscillators," *IEEE Journal of Solid-State Circuits*, vol. 33, no. 2, pp.179-194, February 1998.

- 17. L. Lin, L. Tee, P. R. Gray, "A 1.4 GHz Differential Low-Noise CMOS Frequency Synthesizer using a Wideband PLL Architecture," *IEEE ISSCC Digest of Technical Papers*, pp. 204-205, February 2000.

- 18. H. Hedayati, B. Bakkaloglu, W. Khalil, "Closed-loop Nonlinear Modeling of Wideband  $\Delta\Sigma$  Fractional-N Frequency Synthesizers," *IEEE Transactions on Microwave Theory and Techniques*, vol. 54, no. 10, pp. 3654-3663, October 2006.

- 19. E. Familier, C. Venerus, I. Galton, "A Class of Quantizers with DC-Free Quantization Noise and Optimal Immunity to Nonlinearity-Induced Spurious Tones," *IEEE Transactions on Signal Processing*, vol. 61, no. 17, 2013.

#### **CHAPTER 2**

# A CLASS OF QUANTIZERS WITH DC-FREE QUANTIZATION NOISE AND OPTIMAL IMMUNITY TO NONLINEARITY-INDUCED SPURIOUS TONES

**Abstract**—Fractional-*N* phase-locked loops (PLLs) typically use noise-shaping coarse quantizers to control their instantaneous output frequency. The resulting quantization noise and its running sum inevitably get distorted by non-ideal analog components within the PLL, which induces undesirable spurious tones in the PLL's output signal. A recently proposed quantizer, called a successive requantizer, has been shown to mitigate this problem. Its quantization noise and the running sum of its quantization noise can be subjected to up to 5th-order and 3rd-order nonlinear distortion, respectively, without inducing spurious tones. This paper extends the previously published successive requantizer results to design successive requantizers whose quantization noise running sum sequences can attain such immunity to nonlinearity-induced spurious tones up to arbitrarily high orders of distortion. It also presents successive requantizers whose

Manuscript received November 8, 2012; revised February 22, 2013; accepted April 01, 2013. Date of publication May 16, 2013; date of current version August 07, 2013. The associate editor coordinating the review of this manuscript and approving it for publication was Prof. Ljubisa Stankovic. This work was supported by the National Science Foundation under Award 0914748.

The authors are with the Department of Electrical and Computer Engineering, University of California at San Diego, La Jolla, CA 92093-0407 USA (e-mail: galton@ucsd.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identifier 10.1109/TSP.2013.2263503

### I. INTRODUCTION

Fractional-*N* phase locked loops (PLLs) are widely used to synthesize local oscillator signals in communication systems [1], [2]. They typically use noise-shaping coarse quantizers, most commonly implemented as digital delta-sigma ( $\Delta\Sigma$ ) modulators, to quantize digital sequences that control their output frequency. Each quantized sequence can be viewed as the sum of the quantizer's input sequence plus *DC-free quantization noise* [3]–[5].<sup>6</sup> In practical PLLs, the quantization noise and its running sum inevitably are subjected to nonlinear distortion from analog circuit imperfections within the PLL. This has the undesirable effect of inducing spurious tones in the sequences, even when the undistorted sequences are free of spurious tones [6]–[12]. Spurious tones induced in this fashion are referred to as *nonlinearity-induced spurious tones*.

Most communication applications require the power of spurious tones to be very low, as they ultimately appear in the PLL's output signal and can be critically harmful to communication system performance. One way to minimize spurious tone power is to make the analog circuitry of the PLL very linear. Unfortunately, improving analog circuit linearity tends to increase power dissipation and integrated circuit area significantly. Alternatively, the coarse quantizer can be designed to ensure that the quantization noise

<sup>&</sup>lt;sup>6</sup> A sequence whose running sum is bounded for all time is said to be DC-free.

and its running sum remain free of spurious tones even when subjected to the type of nonlinear distortion commonly imposed within the PLL.

A sequence x[n] is said to be immune to spurious tones up to order *h* if  $x^p[n]$ , for p = 1, 2, ..., h, are free of spurious tones. A recently proposed quantizer, called a successive requantizer, was introduced in [6] and implemented as part of a phase-noise cancelling PLL in [7] to mitigate the power of nonlinearity-induced spurious tones. Its quantization noise and the running sum of its quantization noise are immune to spurious tones up to orders 5 and 3, respectively.

This paper extends the previously published successive requantizer results to design successive requantizers with higher immunity to nonlinearly-induced spurious tones. It proves that the order up to which the quantization noise running sum of a successive requantizer is immune to spurious tones can be arbitrarily increased at the expense of increasing the range of values spanned by the quantization noise running sum. In a PLL, increasing this range tends to increase the quantization noise power, and, therefore, the phase noise. Hence, a tradeoff exists between enhanced immunity to nonlinearity-induced spurious tones and increased phase noise power. The paper also presents successive requantizers that are optimal in the sense that their quantization noise and quantization noise running sum are immune to spurious tones up to the maximum possible orders for the range of values spanned by the quantization noise running sum.

#### II. SUCCESSIVE REQUANTIZER BACKGROUND

### A. Spectral Properties of Interest

The periodogram of any sequence x[n] is defined as

$$I_{x,L}(\omega) = \frac{1}{L} \left| \sum_{n=0}^{L-1} x[n] e^{-j\omega n} \right|^2$$

(69)

for any positive integer *L* [13]. By definition, x[n] contains a tone at  $\omega_n \neq 0$  if  $I_{x,L}(\omega)$  is unbounded at  $\omega = \omega_n$  as  $L \to \infty$  [6], [14]. In a PLL, the nonlinearities to which the quantization noise sequence s[n] and the quantization noise running sum sequence

$$t[n] = \sum_{k=0}^{n} s[k]$$

(70)

are subjected tend to be well-modeled as truncated memoryless power series [7]. Therefore, this work focuses on the properties of  $I_{s^q,L}(\omega)$  and  $I_{t^p,L}(\omega)$  for integer values of q and p up to some maximum values.

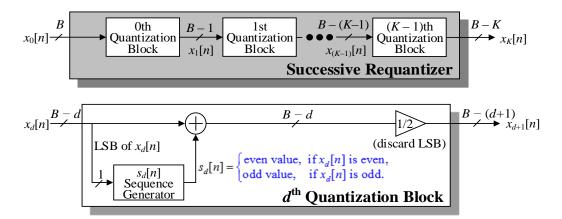

## B. Successive Requantizer Architecture

As shown in Fig. 6, a typical fractional-*N* PLL consists of a phase detector, a lowpass loop filter, a voltage controlled oscillator (VCO), a frequency divider, and a noise-shaping coarse quantizer that introduces DC-free quantization noise. Its purpose is to generate a periodic or frequency modulated output signal with an instantaneous frequency of  $(N + x[n])f_{ref}$ , where *N* is a positive integer, x[n] is a sequence of fractional values, and  $f_{ref}$  is the frequency of a reference oscillator. In most applications x[n] is constant, and in other applications it varies slowly. The PLL's feedback loop adjusts the output frequency to be  $f_{ref}$  times the average of the divider modulus  $N + x_K[n]$ . If  $x_K[n]$  could be set to x[n] for all n, the PLL would have the desired output frequency. However, practical frequency dividers can only count integer numbers of VCO cycles, so  $x_K[n]$  must be integer-valued. Therefore, the coarse quantizer ensures that  $x_K[n]$  is integer-valued but averages to x[n] in time. This results in the desired PLL output frequency, although the deviations of  $x_K[n]$  from x[n] contribute an extra component to the PLL's phase noise. As explained in the introduction, the coarse quantizer can be implemented as the successive requantizer presented in [6].

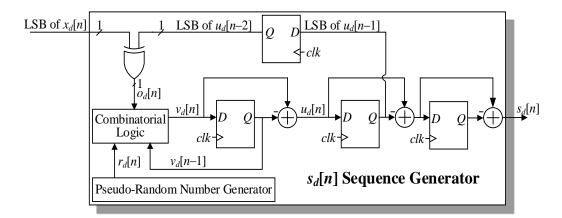

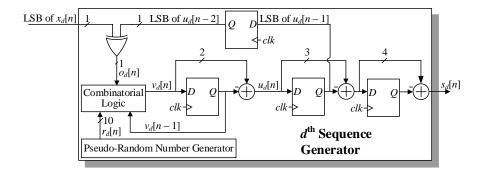

The high-level architecture of the successive requantizer is shown in Figs. 7 and 8, wherein all node variables are integer-valued sequences in two's complement format. The successive requantizer consists of K serially-connected quantization blocks, each of which quantizes its input by 1 bit, so the successive requantizer quantizes its input by K bits. Its input,

$$x_0[n] = 2^{\kappa} x[n], (71)$$

is a *B*-bit sequence which satisfies  $|x_0[n]| \le 2^{B-2}$  for all *n*. The *d*th quantization block's input,  $x_d[n]$ , and output,  $x_{d+1}[n]$ , are related through

$$x_{d+1}[n] = \frac{1}{2} \left( x_d[n] + s_d[n] \right), \tag{72}$$

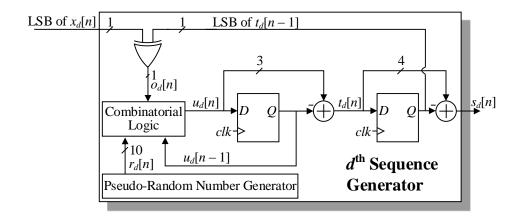

where  $s_d[n]$  is a sequence generated by the quantization block's *sequence generator*. The sequence generator (Fig. 8) generates  $s_d[n]$  as a function of the *parity sequence*,  $o_d[n]$ , which at each time, n, is 1 if  $s_d[n]$  is odd and 0 if  $s_d[n]$  is even. It chooses  $s_d[n]$  to have the same parity as  $x_d[n]$  for each n so that  $x_{d+1}[n]$  is an integer-valued sequence, and to have a sufficiently small magnitude that the two's complement representation of  $x_{d+1}[n]$  requires one less bit than that of  $x_d[n]$ . Hence, the output of the successive requantizer is a two's complement integer-valued sequence given by

$$x_{K}[n] = 2^{-K} x_{0}[n] + s[n] = x[n] + s[n],$$

(73)

where

$$s[n] = \sum_{d=0}^{K-1} 2^{d-K} s_d[n]$$

(74)

is the quantization noise. The running sum of  $s_d[n]$  is

$$t_d[n] = \sum_{k=0}^n s_d[k],$$

(75)

so (74) implies that the running sum of the quantization noise can be written as

$$t[n] = \sum_{d=0}^{K-1} 2^{d-K} t_d[n].$$

(76)

The lowest integer bound on the magnitude of each  $t_d[n]$  sequence is denoted as  $N_t$ , so  $|t_d[n]| \le N_t$  for all *d* and *n*. Therefore, it follows from (76) that  $|t[n]| < N_t$  for all *n*.

As shown in [6], if the sequence generator is designed such that the probability mass function (pmf) of  $s_d[n]$  for each n depends only on  $o_d[n]$  and  $t_d[n - 1]$ , then  $t_d[n]$  is a discrete-valued Markov random sequence conditioned on  $o_d[n]$ . Hence, for any parity sequence,  $o_d[n]$ , the evolution of  $t_d[n]$  from times u to u + m can be represented by an mstep  $(2N_t + 1) \times (2N_t + 1)$  state transition matrix,  $\mathbf{A}_{\{o_d[n]\}}[u, m]$ , where the element on the *i*th row and *j*th column is

$$\left(\mathbf{A}_{\{o_d[n]\}}[u,m]\right)(i,j) = \Pr(t_d[u+m] = \mathbf{t}(j) \mid t_d[u] = \mathbf{t}(i), \\ o_d[n]; n = u+1, u+2, \dots, u+m)$$

$$(77)$$

and

$$\mathbf{t} = (N_t \quad N_t - 1 \quad \dots \quad -N_t)^T \,. \tag{78}$$

It follows from the properties of state transition matrices that for m > 1  $\mathbf{A}_{\{o_d[n]\}}[u, m]$  can be expanded as a product of one-step state transition matrices as

$$\mathbf{A}_{\{o_d[n]\}}[u,m] = \mathbf{A}_{\{o_d[n]\}}[u,1]\mathbf{A}_{\{o_d[n]\}}[u+1,1]\cdots\mathbf{A}_{\{o_d[n]\}}[u+m-1,1].$$

(79)

As is also shown in [6],  $\mathbf{A}_{\{o_d[n]\}}[v-1, 1]$  at each time index v is equal to one of two one-step state transition matrices, denoted as  $\mathbf{A}_{\mathbf{e}}$  and  $\mathbf{A}_{\mathbf{o}}$ : when  $o_d[v] = 0$ ,  $\mathbf{A}_{\{o_d[n]\}}[v-1, 1] = \mathbf{A}_{\mathbf{e}}$ , and when  $o_d[v] = 1$ ,  $\mathbf{A}_{\{o_d[n]\}}[v-1, 1] = \mathbf{A}_{\mathbf{o}}$ . It follows from (75) that

$$s_d[n] = t_d[n] - t_d[n-1],$$

(80)